一.硬件设计

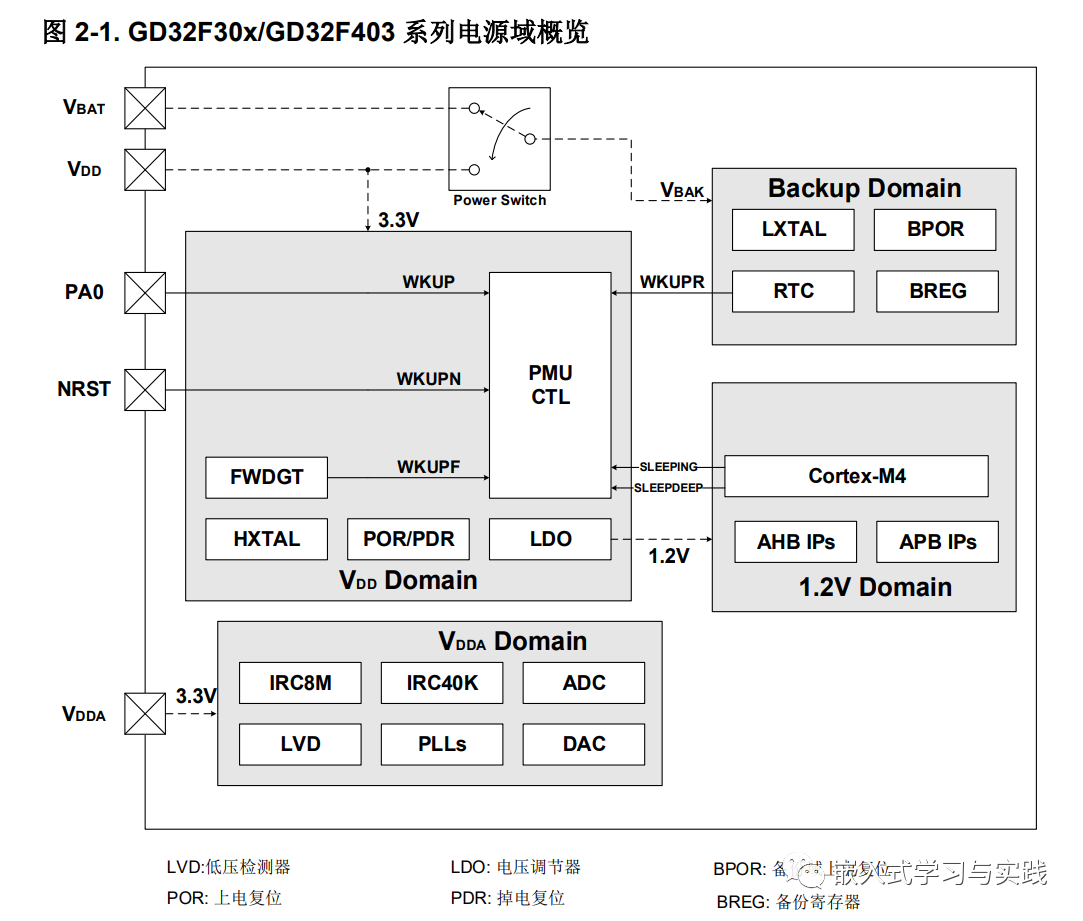

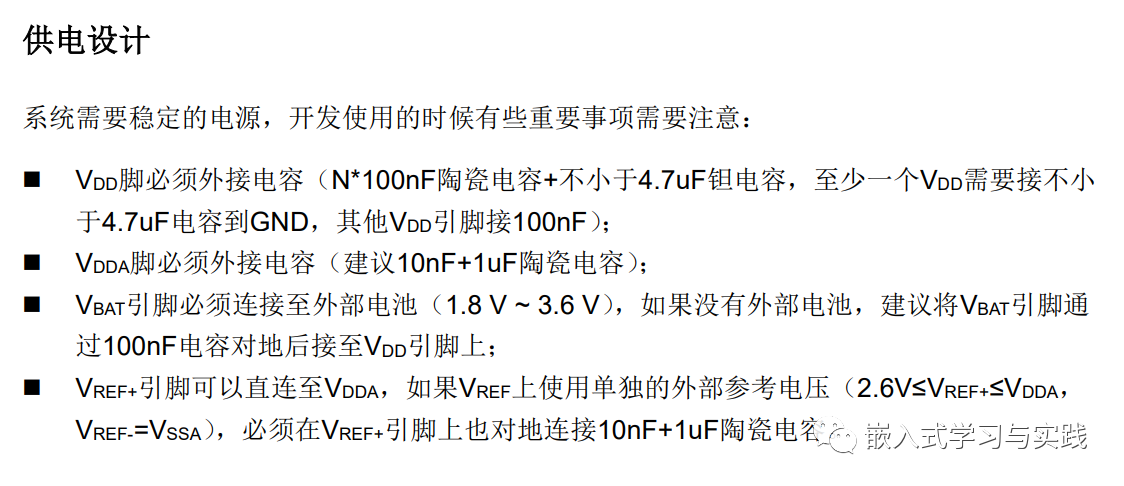

1.电源

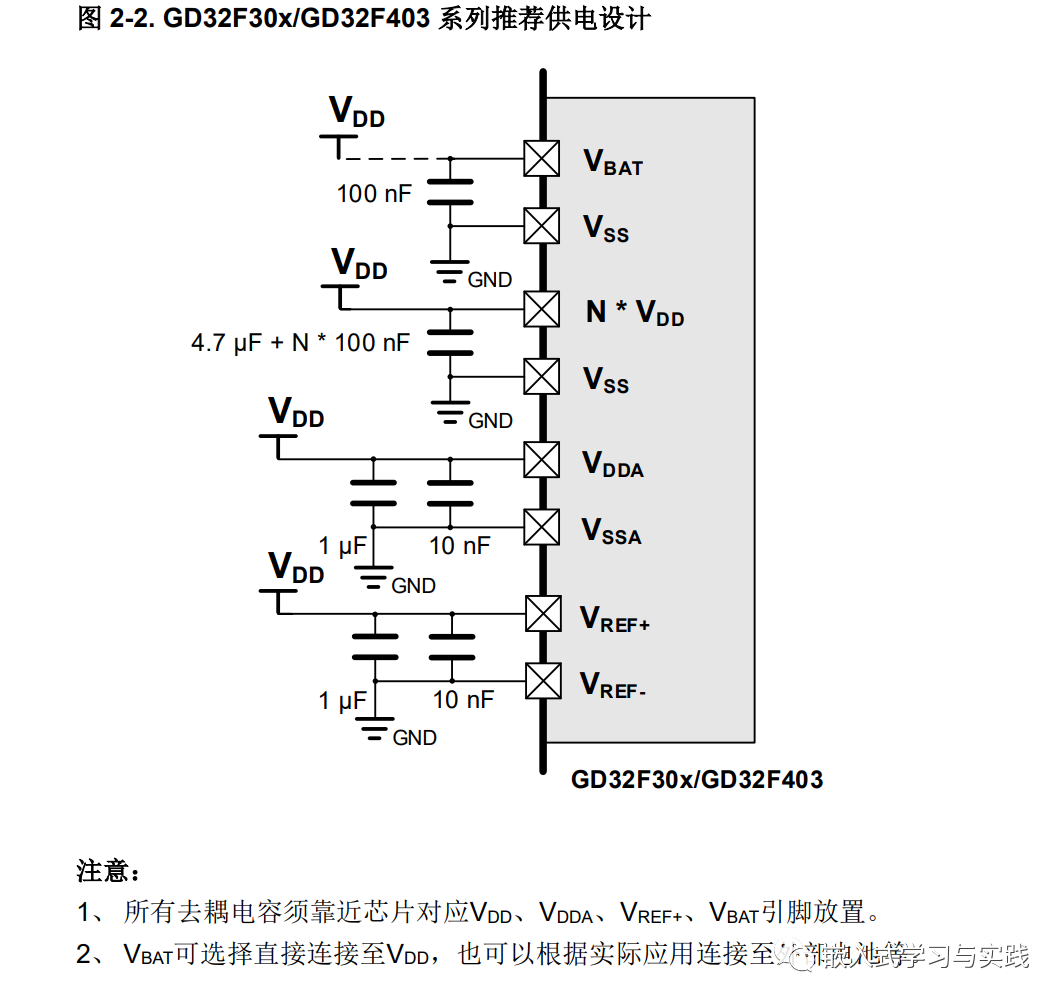

2.复位

注意:

1. 内部上拉电阻40kΩ,建议外部上拉电阻建议10kΩ,以使得电压干扰不会导致芯片工作异常;

2. 若考虑静电等影响,可在NRST管脚处放置ESD保护二极管;

3. 尽管MCU内部有硬件POR电路,仍推荐外部加NRST复位阻容电路;

4. 如果MCU启动异常(由于电压波动等),可适当增加NRST对地电容值,拉长MCU复位完成时间,避开上电异常时序区。

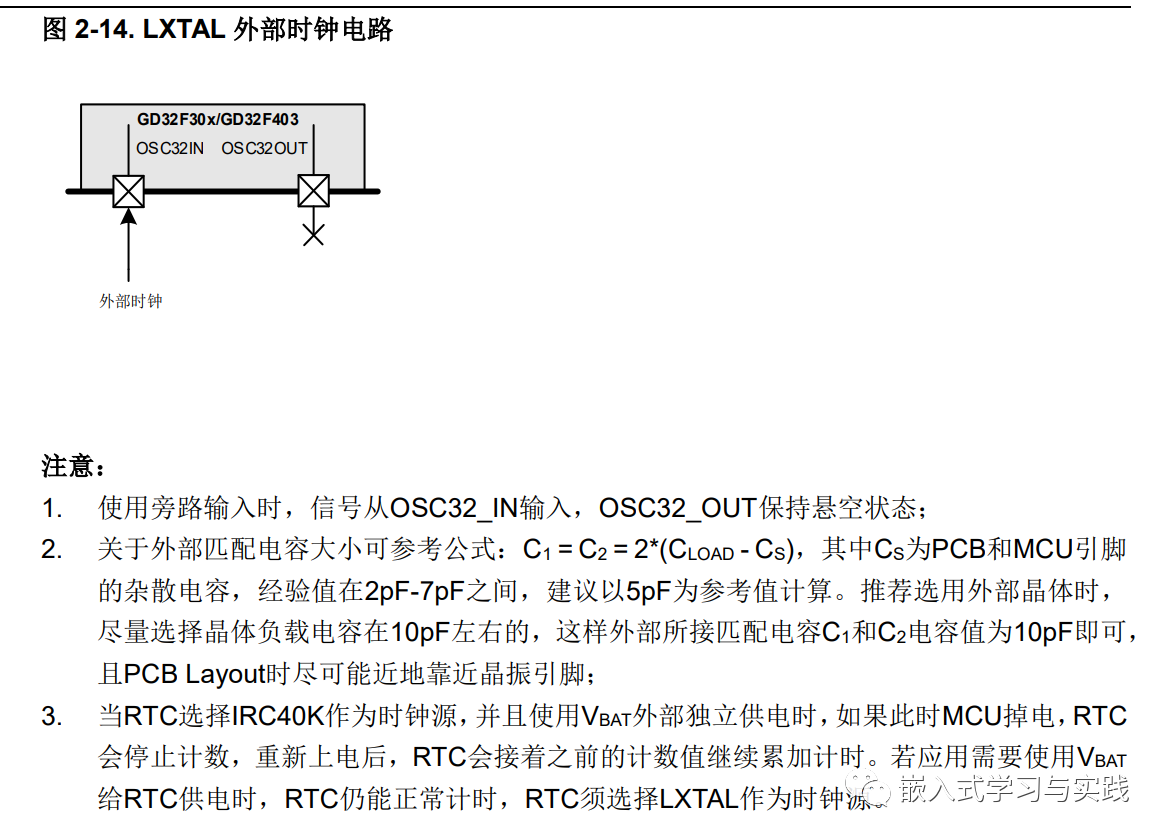

3.时钟

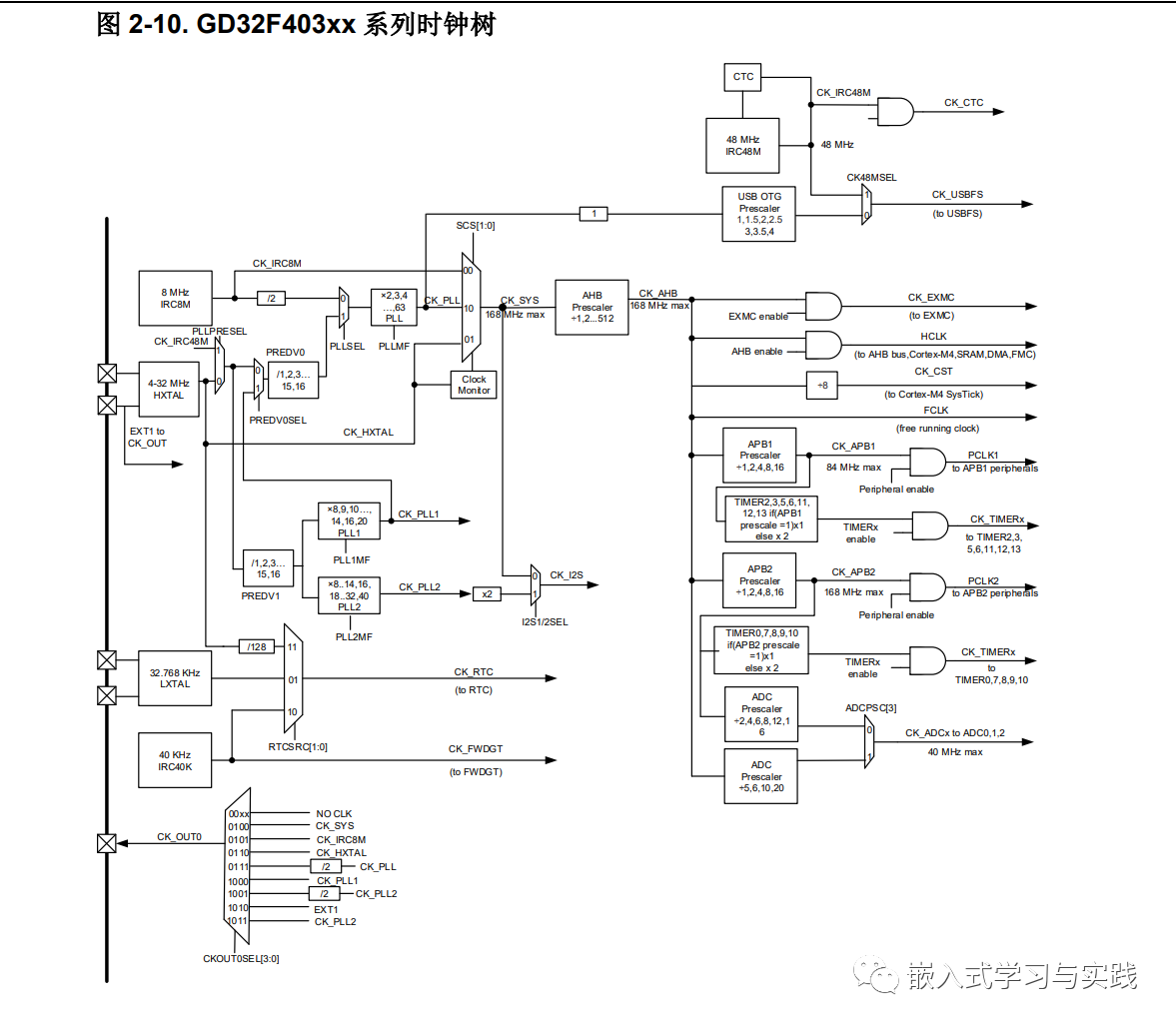

GD32F30x/GD32F403系列内部有完备的时钟系统,可以根据不同的应用场合,选择合适的时钟源,时钟主要特征:

4-32MHz外部高速晶体振荡器(HXTAL);

8MHz内部高速RC振荡器(IRC8M);

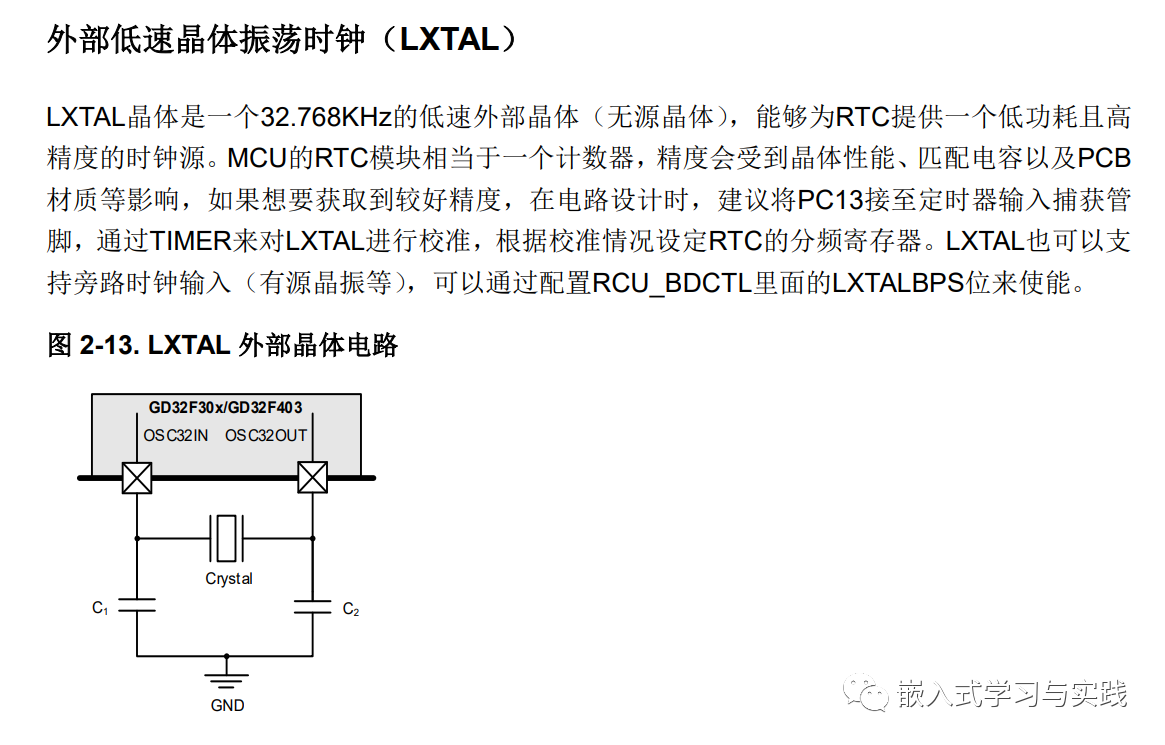

32.768KHz外部低速晶体振荡器(LXTAL);

48 MHz内部高速RC振荡器(IRC48M);

40kHz内部低速RC振荡器(IRC40K);

PLL时钟源可选HXTAL、IRC8M或IRC48M;

HXTAL时钟可监控;

时钟树如下:

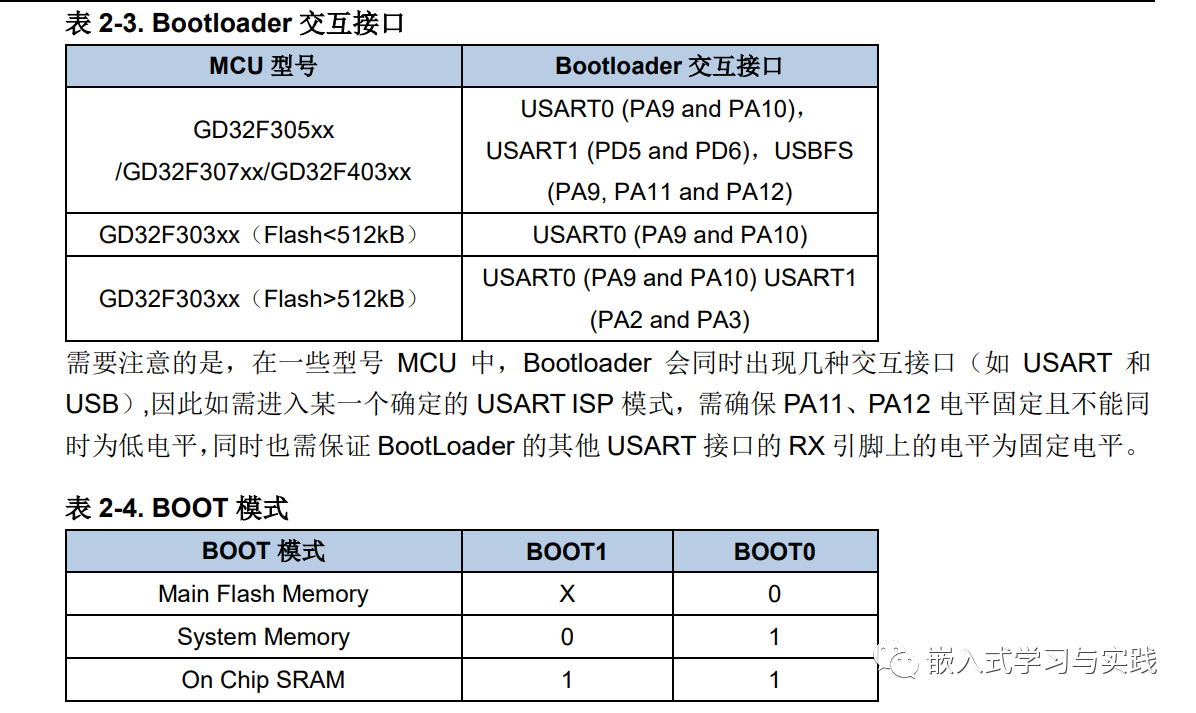

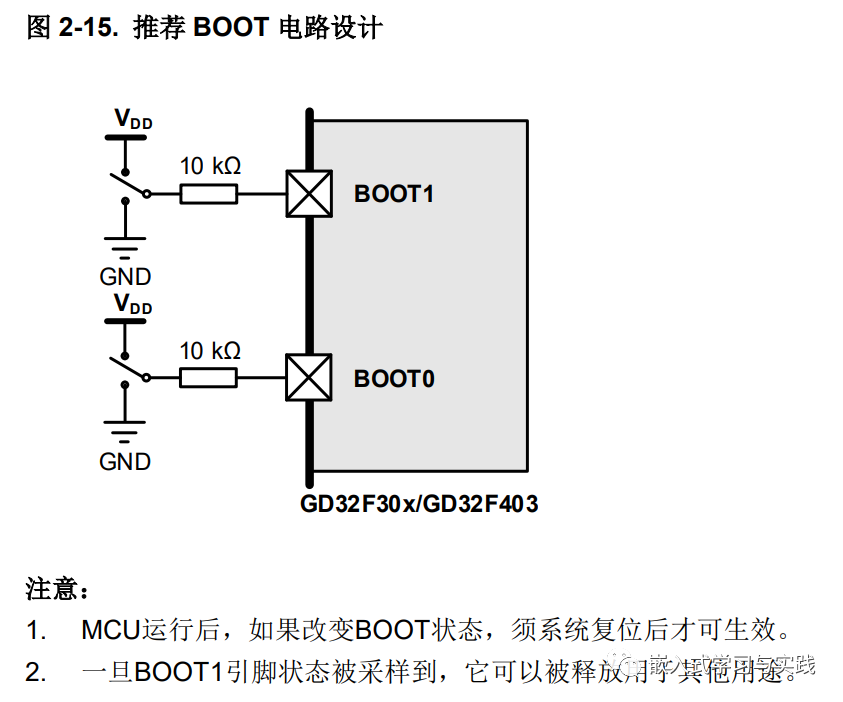

4.启动配置

GD32F30x/GD32F403系列提供三种启动方式,可以通过BOOT0和BOOT1来进行相关的配置。

用户可以配置BOOT0和BOOT1,进行上电复位或系统复位,从而确定启动选项。电路设计时,运行用户程序,BOOT0不能悬空,建议通过一个10kΩ电阻到GND;运行System Memory进行程序更新,需要将BOOT0接高,BOOT1接低,更新完成后,再将BOOT0接低上电才能运行用户程序;SRAM执行程序多用于调试状态下。

嵌入式的 Bootloader 存放在系统存储空间,用于对 FLASH 存储器进行重新编程。在GD32F305xx/ GD32F307xx/ GD32F403xx设备中,Bootloader可以通过USART0 (PA9 andPA10),USART1 (PD5 and PD6),USBFS (PA9, PA11 and PA12)和外界交互。在GD32F303xx(Flash<512kB)设备中,Bootloader可以通过USART0 (PA9 and PA10) 和外界交互, 在GD32F303xx(Flash>512kB)设备中,Bootloader可以通过USART0 (PA9 and PA10) USART1(PA2 and PA3)和外界交互。

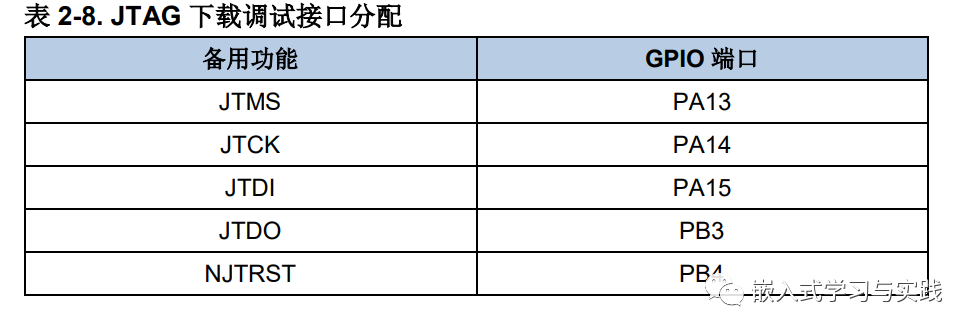

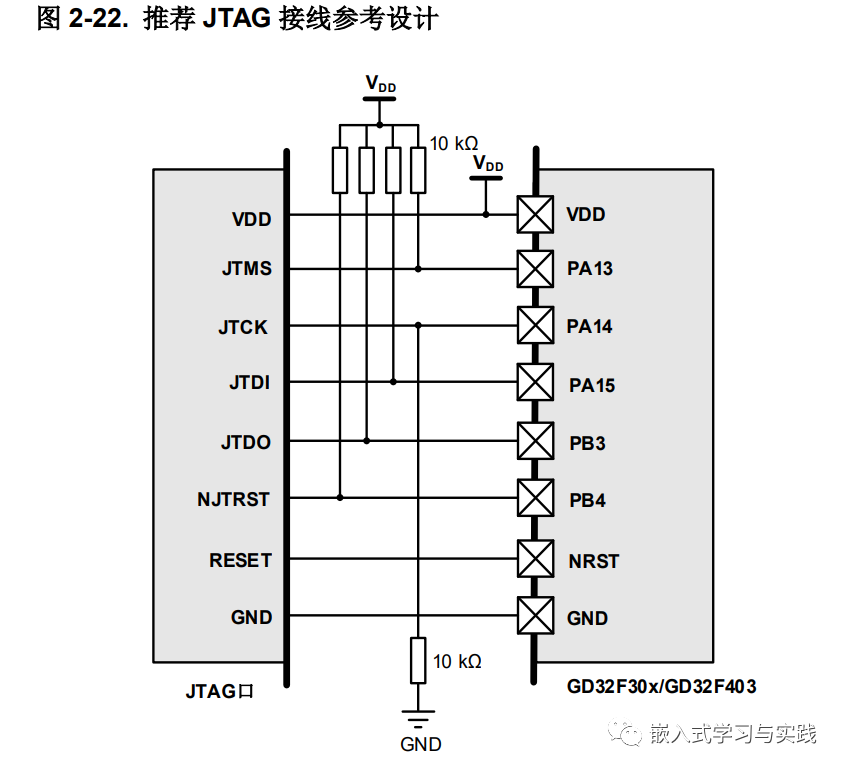

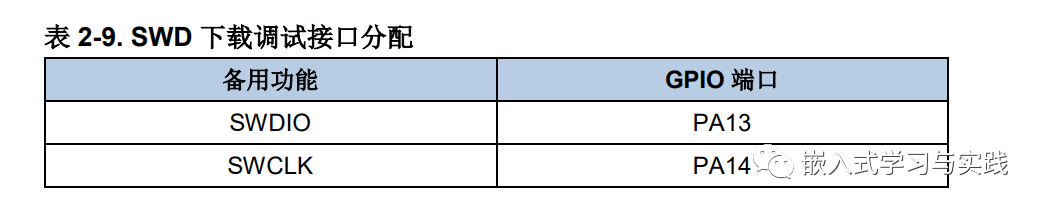

5.下载调试

GD32F30x/GD32F403系列内核支持JTAG调试接口和SWD接口。JTAG接口标准为20针接口,其中5根信号接口,SWD接口标准为5针接口,其中2根信号接口。

注意:复位后,调试相关端口为输入PU/PD模式,其中:

PA15:JTDI为上拉模式;

PA14:JTCK / SWCLK为下拉模式;

PA13:JTMS / SWDIO为上拉模式;

PB4:NJTRST为上拉模式;

PB3:JTDO为浮空模式。

有以下几种方式可以提高SWD下载调试通信的可靠性,增强下载调试的抗干扰能力。

1. 缩短SWD两个信号线长度,最好15cm以内;

2. 将SWD两根线和GND线编个麻花,缠在一起;

3. 在SWD两根信号线对地各并几十pF小电容;

4. SWD两根信号线任意IO串入100Ω~1KΩ电阻。

6.典型外设

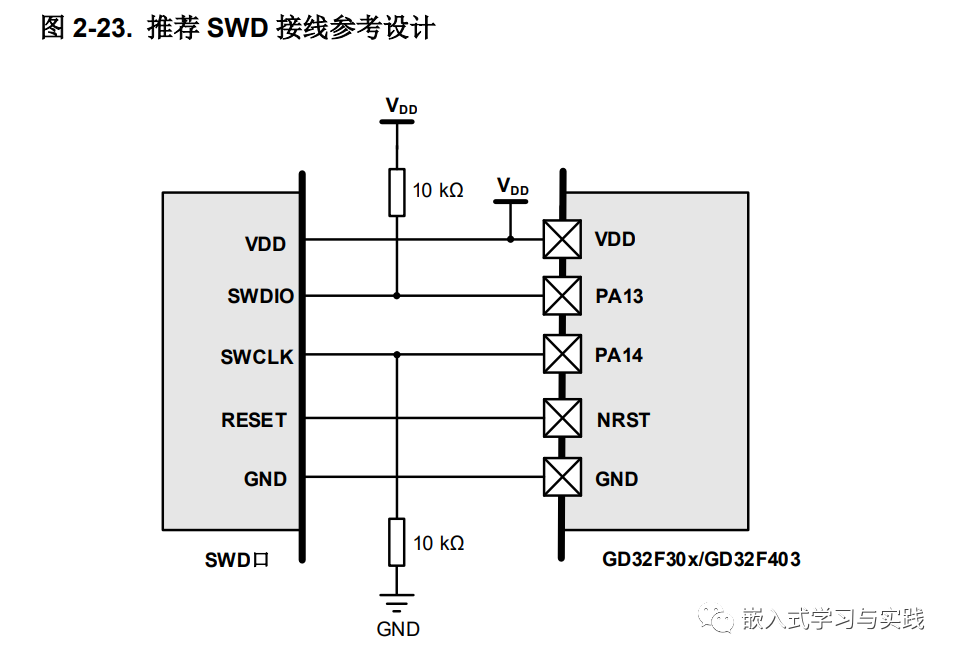

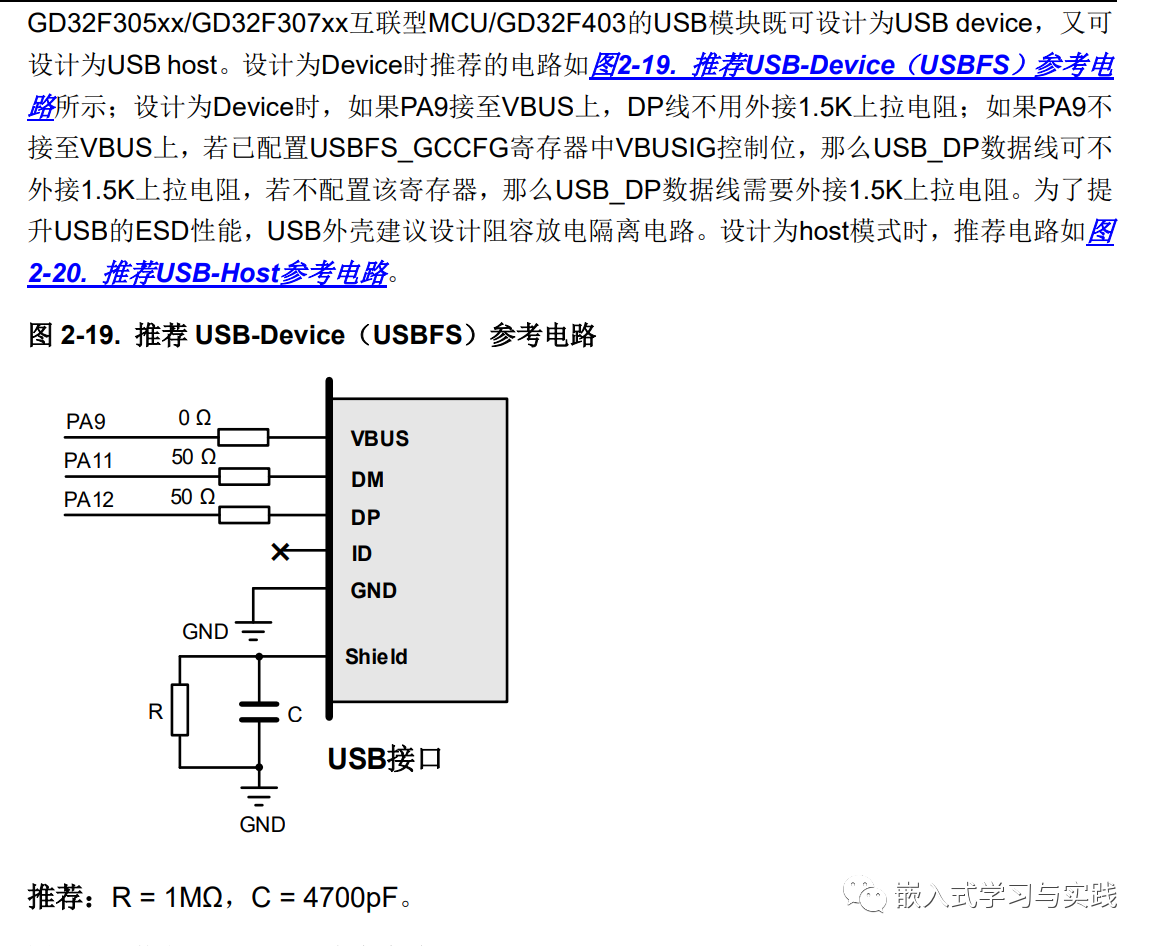

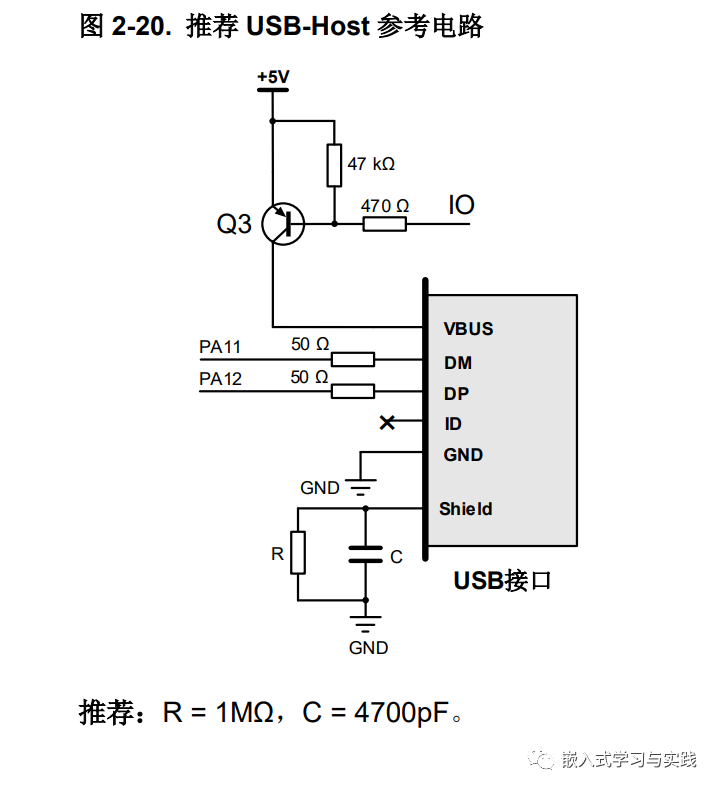

ubs外设电路

二.PCB Layout

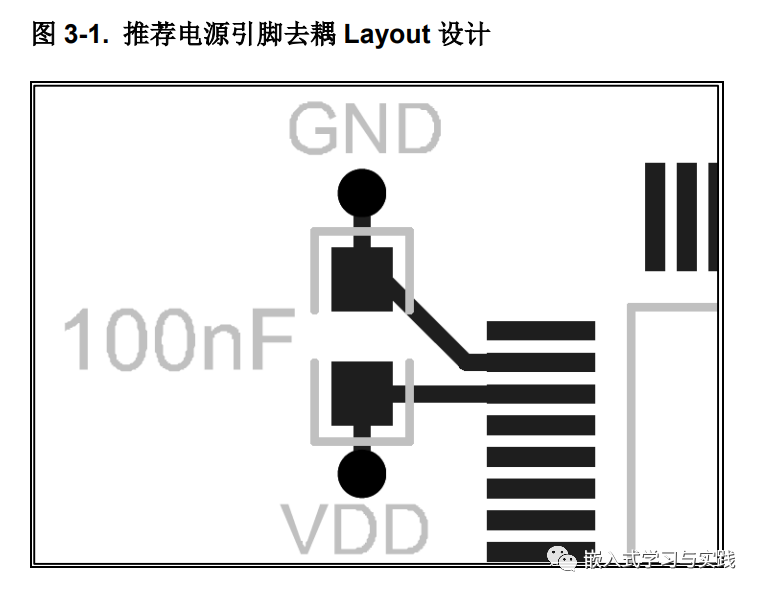

1.电源去耦电容

GD32F30x/GD32F403系列电源有VDD、VDDA、VREF+和VBAT四个供电脚,100nF去耦电容采用陶瓷即可,且需要保证位置尽可能地靠近电源引脚。电源走线要尽量使得经过电容后再到达MCU电源引脚,建议可通过靠近电容PAD处打Via的形式Layout。

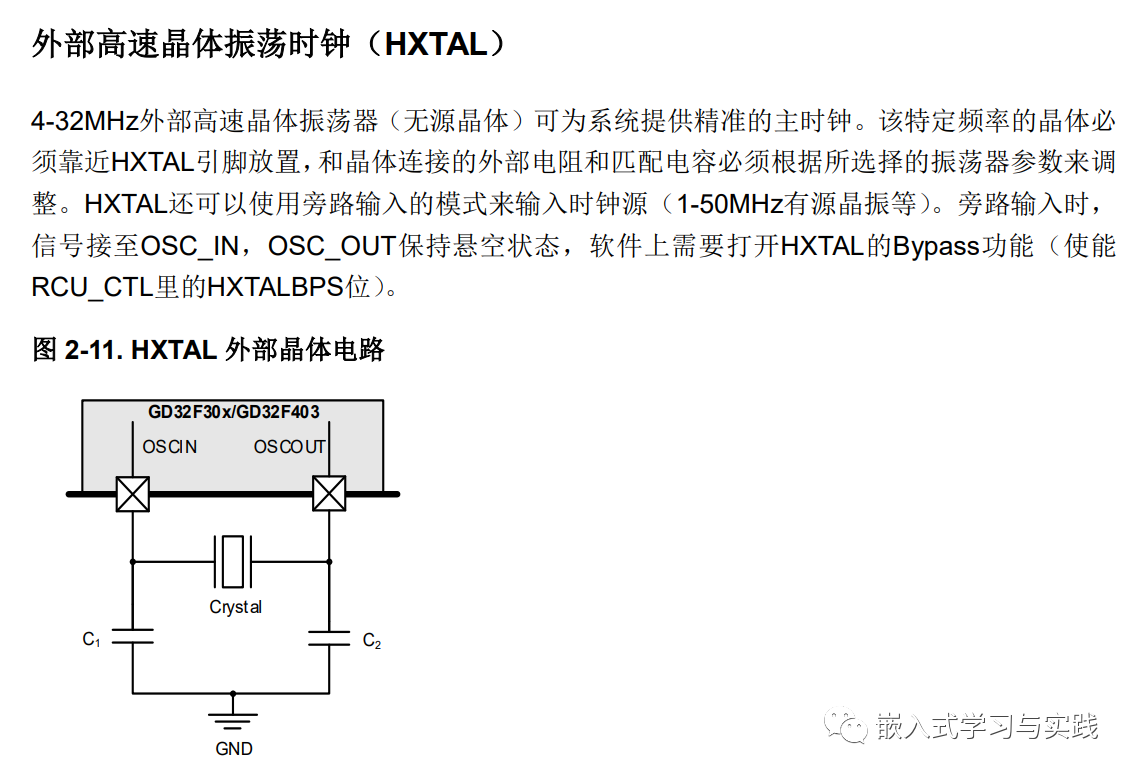

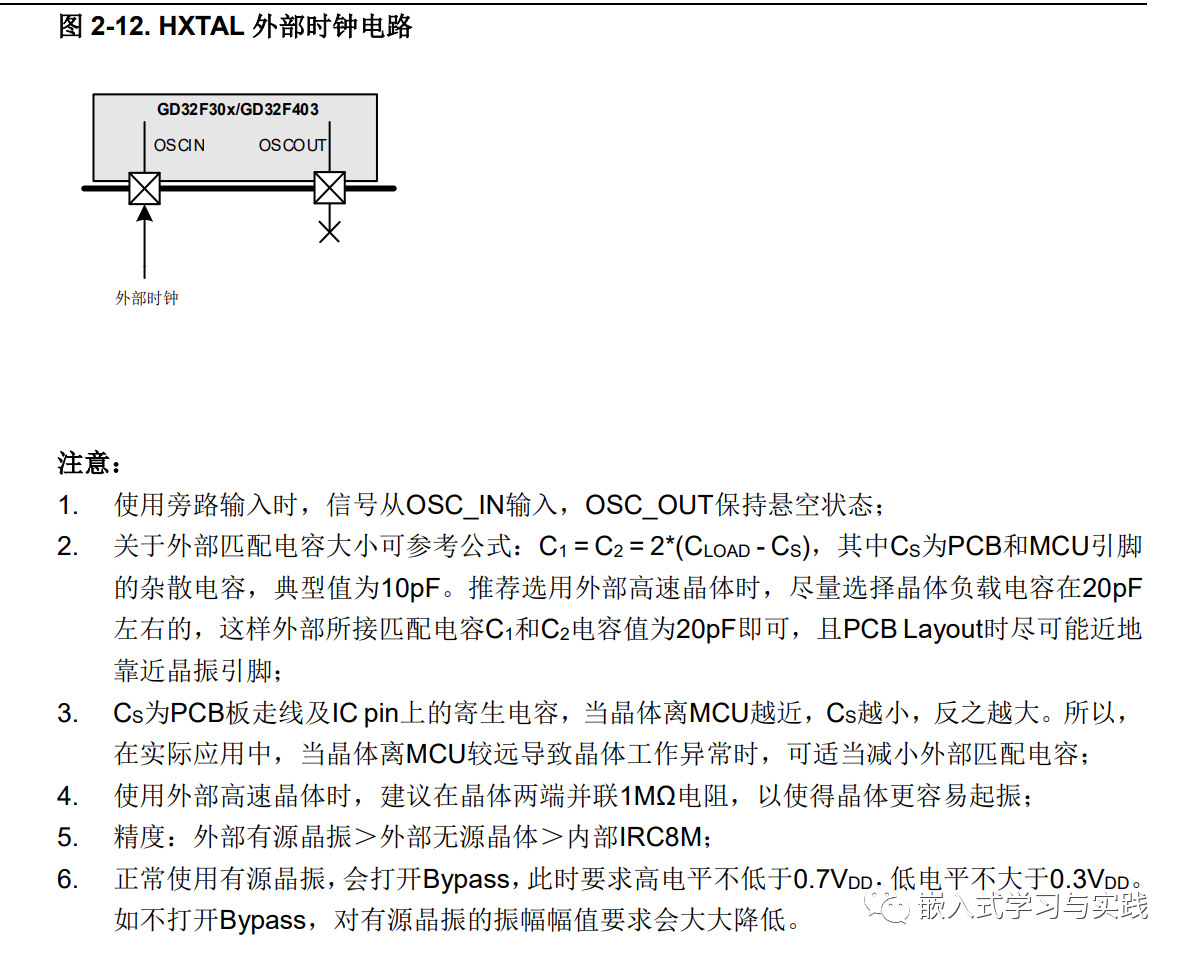

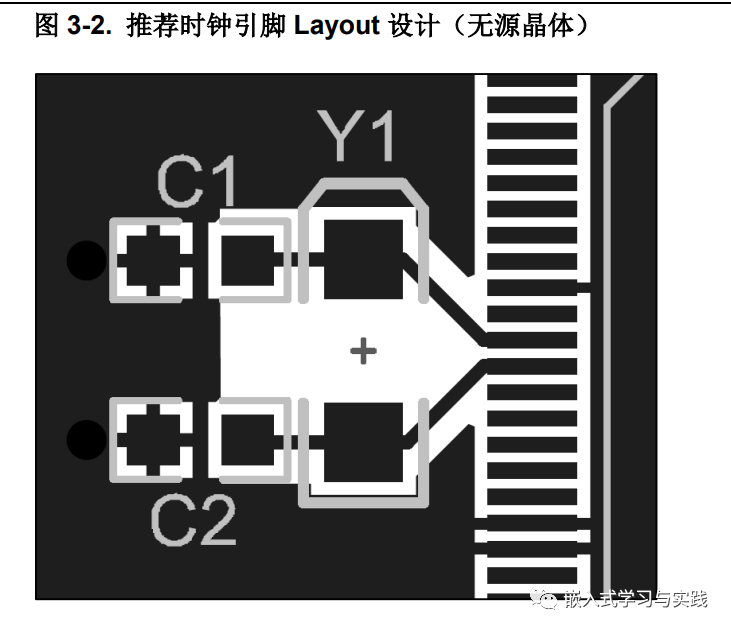

2.时钟电路

GD32F30x/GD32F403系列时钟有HXTAL和LXTAL,要求时钟电路(包括晶体或晶振及电容等)靠近MCU时钟引脚放置,且尽量时钟走线由GND包裹起来。

注意:

1. 晶体尽量靠近MCU时钟Pin,匹配电容等尽量靠近晶体;

2. 整个电路尽量与MCU在同层,走线尽量不要穿层;

3.时钟电路PCB区域尽量禁空,不走任何与时钟无关走线;

4. 大功率、强干扰风险器件及高速走线尽量远离时钟晶体电路;

5.时钟线进行包地处理,以起到屏蔽效果。

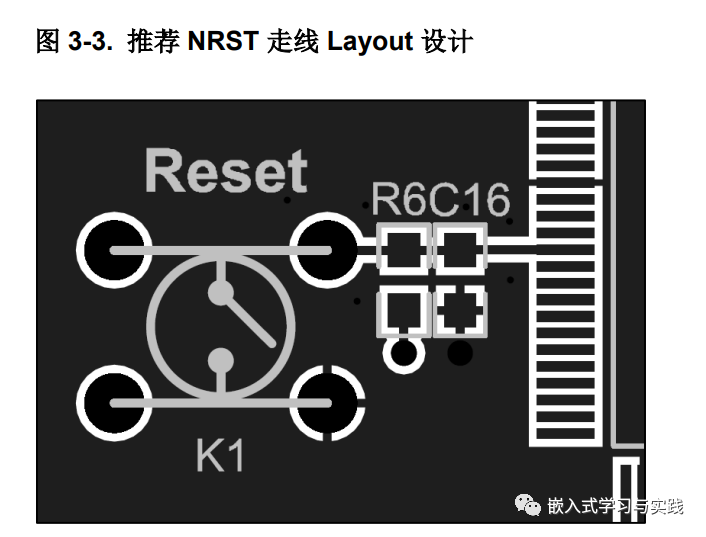

3.复位电路

注意:复位电路阻容等尽可能地靠近MCU NRST引脚,且NRST走线尽量远离强干扰风险器件及高速走线等,条件允许的话,最好将NRST走线做包地处理,以起到更好的屏蔽效果。

4.USB 电路

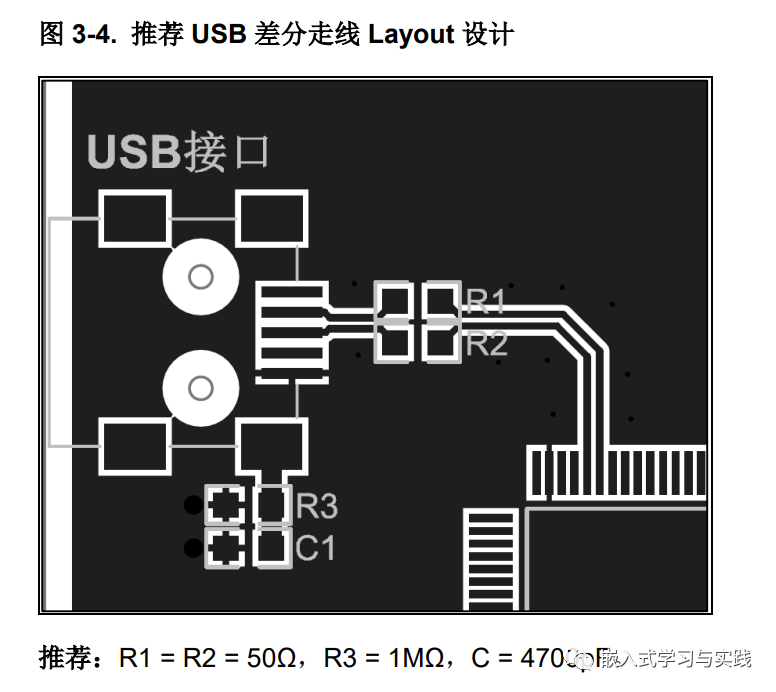

USB模块有DM、DP两根差分信号线,建议PCB走线要求做特性阻抗90ohm,差分走线严格按照等长等距规则来走,且尽量使走线最短,如果两条差分线不等长,可在终端用蛇形线补偿短线。

由于阻抗匹配考虑,串联匹配电阻建议50Ω左右即可。当USB终端接口离MCU较远的时候,需要适当增大该串联电阻值。

注意:

1.布局时摆放合理,以缩短差分走线距离;

2. 优先绘制差分线,一对差分线上尽量不要超过两对过孔,且需要对称放置;

3. 对称平行走线,保证两根线紧密耦合,避免90°、弧形或45°走线方式;

4. 差分走线上所接阻容、EMC等器件,或测试点,也要做到对称原则。

对于USB HS模块,MCU与外部HS PHY之间的数据线与信号控制线也尽量走短,需要用蛇形线做等长处理,注意事项如下:

1.布局时摆放合理,USB HS-PHY芯片与MCU之间尽量紧凑;

2. 布线时,以信号线中最长的一根线长度为目标,将其他信号线通过蛇形走线补偿即可。

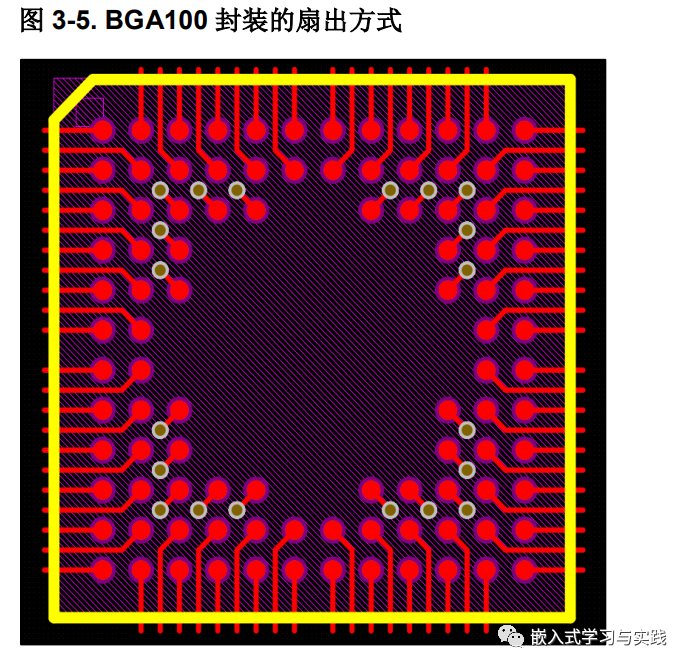

5.BGA 走线

GD32F403x 系列中包含 BGA100 的封装,对应的型号为 GD32F403VxH6,该芯片走线和其它 BGA 芯片类似,先对各个球型焊盘进行扇出,再进行布线操作。对于0.5 mm Pitch 的 BGA封装,若将 BGA 焊盘大小设置为 0.25/0.35,过孔距焊盘以及线宽线距为 3 mil 时,可以使用Dog bone 型扇出,扇出后如图 3-5. BGA100 封装的扇出方式所示,过孔距焊盘距离为 4.5mil;但此种布线对 PCB 制造商工艺要求较高,需与 PCB 制造商沟通后再进行布线,若制造商工艺达不到要求,可对此BGA 封装打盘中孔以及盲埋孔

来源: 嵌入式学习与实践

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理

审核编辑 黄宇

-

单片机

+关注

关注

6032文章

44513浏览量

632881 -

mcu

+关注

关注

146文章

16984浏览量

350275 -

pcb

+关注

关注

4317文章

23001浏览量

396205 -

Layout

+关注

关注

14文章

402浏览量

61650

发布评论请先 登录

相关推荐

【高手问答】从事单片机软硬件开发15年的工程师们,与您探讨单片机软硬件设计

单片机硬件学习思路

多个单片机硬件系统的案例分析

单片机数据采集系统PCB板制作

【毕设狗】【单片机毕业设计】基于单片机的温控水杯的设计(实物+proteus仿真+源码+原理图+PCB+软件设计流程

单片机新手指导3:STM32单片机学习步骤---偏硬件方向

单片机硬件设计和PCB Layout参考

单片机硬件设计和PCB Layout参考

评论