位带操作可能现在用的比较少了,但在以前MCU性能不是很好的时候,位带操作却是众多软件工程师常用操作。

本文主要结合Cortex-M3内核(STM32F1)来讲述,相信许多朋友在初学的时候都被绕晕过。

1、关于位带操作

Bit-banding简称位带,有人也叫位段。支持位带操作后,可以使用普通的加载/存储指令来对单一的比特进行读写。

很多朋友是从学习51单片机过来的,都知道P1.1这个引脚可以单独控制,我们操作的这个引脚就是一个Bit位。

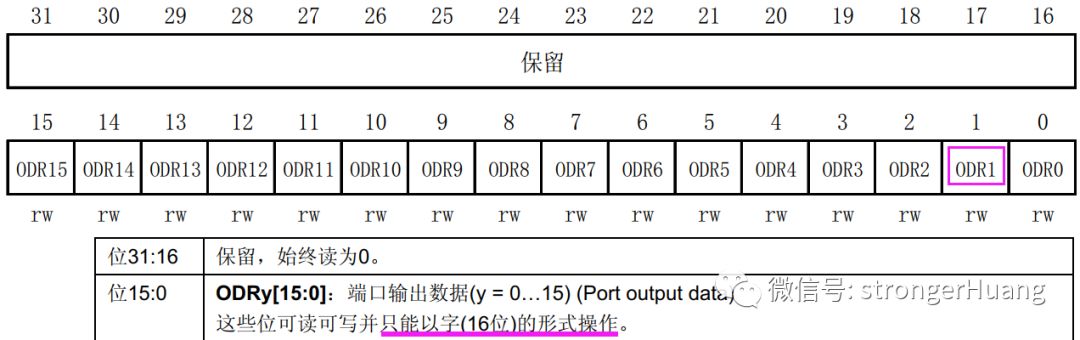

我们都知道在STM32中不能直接操作寄存器的某一个Bit位,比如单独控制PA端口输出数据寄存器中的ODR1,如下图:

STM32F1内核Cortex-M3早就考虑到了这个问题,为了能达到直接操作ODR1这类Bit位,就在内核中开辟了一块地址区域(位带别名):可以将ODR1这类Bit位(位带区)映射到位带别名区域对应的地址,只需要操作映射后的地址,就可以实现操作这个ODR1位了。

简单来说就是映射操作,只是这个映射操作有许多约定要遵循。

2、位带操作中的映射关系

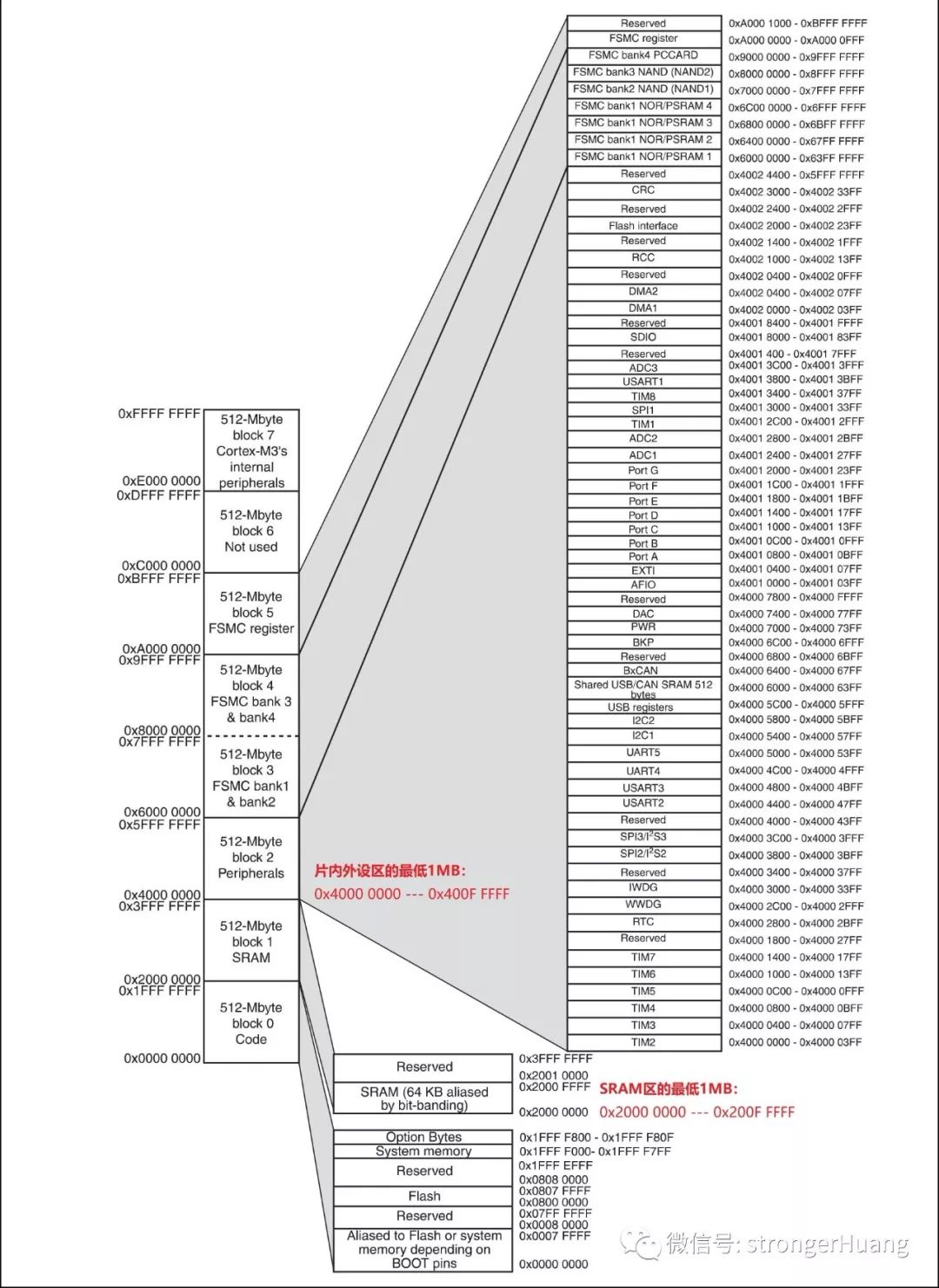

在Cortex-M3中有两个区实现了位带操作,其中一个是SRAM区的最低 1MB 范围,第二个则是片内外设区的最低 1MB 范围。

这两个区域如下图红色标注的区域:

这两个1MB将分别映射到另外两个地址区域:1.SRAM区的最低1MB(0x2000 0000 --- 0x200F FFFF) 映射到(0x2200 0000 --- 0x23FF FFFF)。

2.片内外设区的最低1MB(0x4000 0000 --- 0x400F FFFF)映射到(0x4200 0000 --- 0x43FF FFFF)。

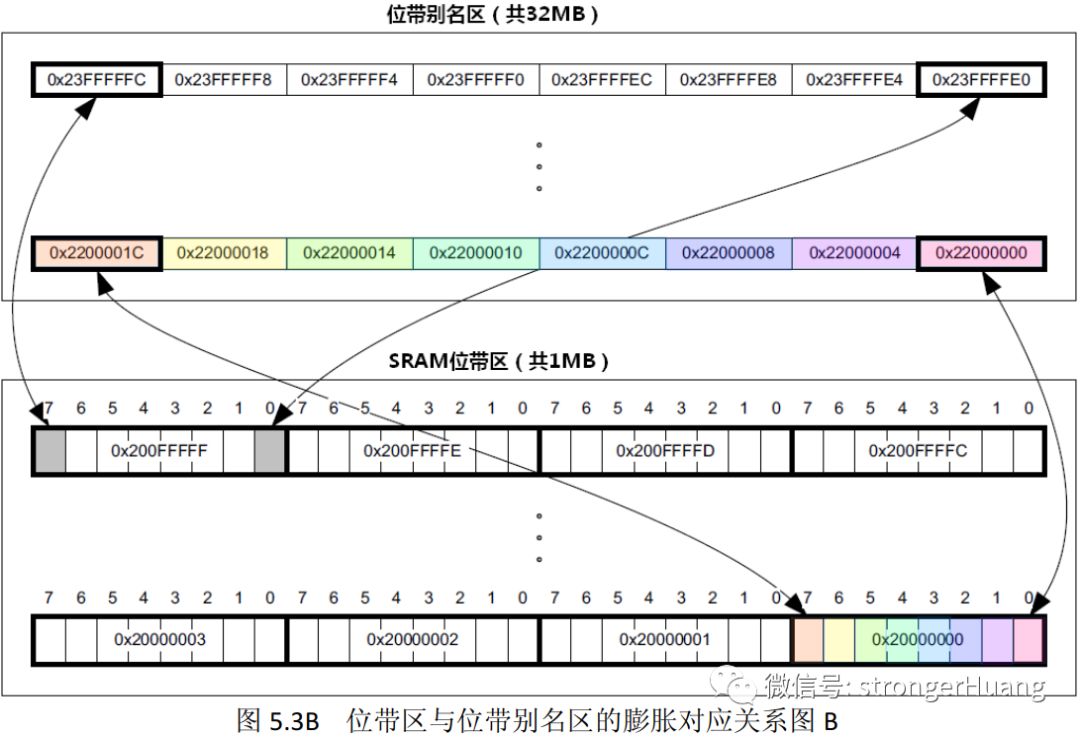

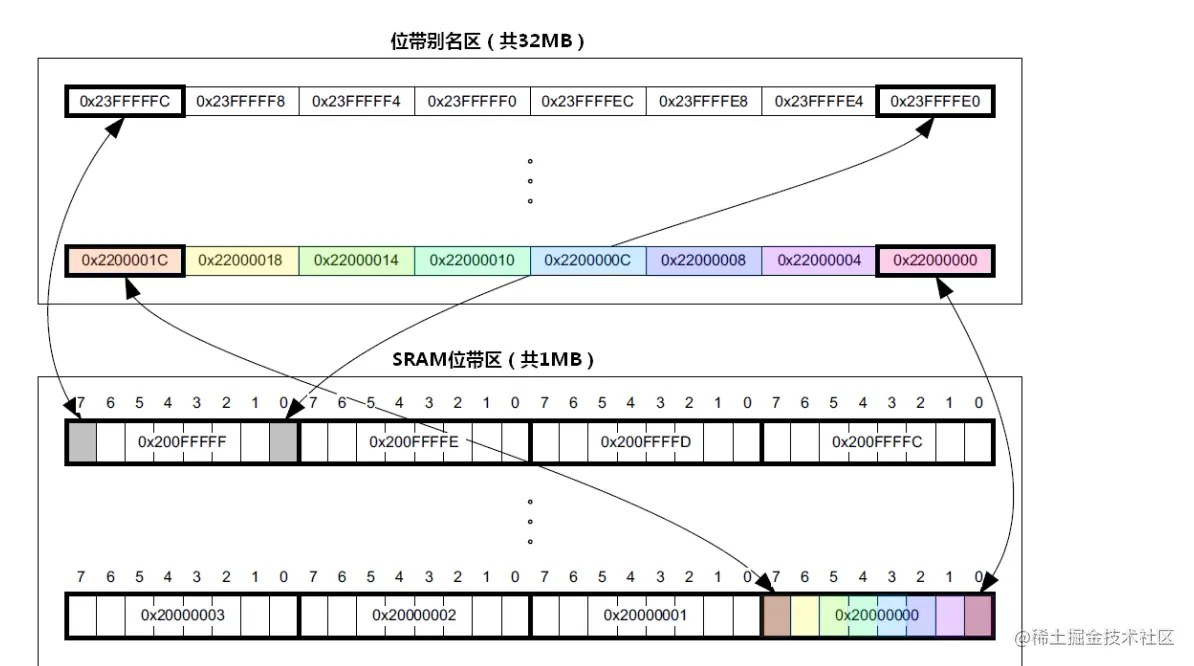

其实就是映射到偏移(距离自身)0x0200 0000外的32MB空间(位带别名区),如下图SRAM区映射关系:

提示:看图中的有颜色的8Bit,它是映射到偏移0x0200 0000外的32Bit(4Byte)空间上。我们读写0x2200 0000这个地址,其实就是操作0x2000 0000中的Bit0位。

这就是所谓的“比特的膨胀对应关系”,1Bit膨胀到32Bit(4字节)。4字节对应的就是那1Bit位的地址,而这个地址中的数据只有最低一位才有效(LSB)。

解释上面多处出现的关键词:位带区:支持位带操作的地址区;位带别名:对别名地址的访问最终作用到位带区的访问上;

3、位带区->别名区计算公式

位带操作的主要目的:通过Bit位地址(A)计算得到别名区地址(AliasAddr)。

1.SARM区计算公式

AliasAddr= 0x22000000 + ((A‐0x20000000)*8+n)*4 =0x22000000+(A-0x20000000)*32 + n*4

2.片上外设区计算公式

AliasAddr= 0x42000000 + ((A-0x40000000)*8+n)*4 =0x42000000+(A-0x40000000)*32 + n*4

由于映射关系一样,所以公式原理也一样,只是地址不一样。计算公式需要结合上图比特的膨胀对应关系来理解。

*8:1个字4个字节;

*4:1个字节8Bit;

4、代码实现

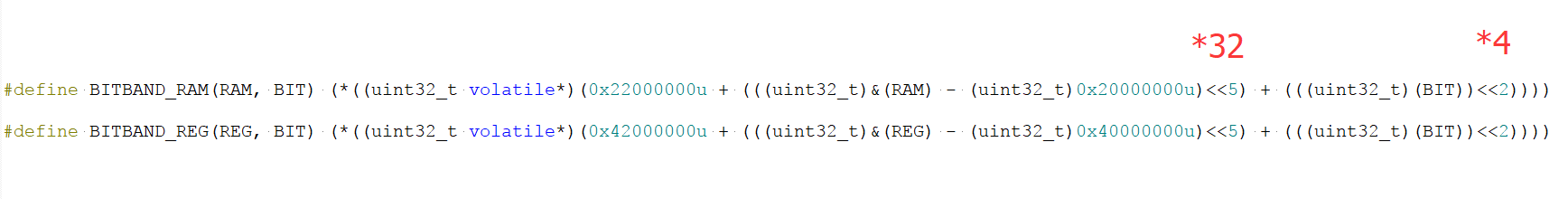

利用上面计算公式,代码实现的过程就很简单,我们的目的就是对“AliasAddr”这个地址进行读写操作。

1.RAM位带操作宏定义

#defineBITBAND_RAM(RAM,BIT)(*((uint32_tvolatile*)(0x22000000u+(((uint32_t) (RAM)-(uint32_t)0x20000000u)<<5) + (((uint32_t)(BIT))<<2))))

2.外设寄存器位带宏定义

#defineBITBAND_REG(REG,BIT)(*((uint32_tvolatile*)(0x42000000u+(((uint32_t) (REG)-(uint32_t)0x40000000u)<<5) + (((uint32_t)(BIT))<<2))))

方便大家对比,给一个截图:

A.RAM地址0x20001000的Bit1位写0

BITBAND_RAM(*(uint32_t*)0x20001000,1)=0;

B.读取RAM地址0x20001000的Bit1位

uint8_tVal;Val=BITBAND_RAM(*(uint32_t*)0x20001000,1);

C.对PA1数据输出寄存器输出1

BITBAND_REG(GPIOA->ODR,1)=1;

D.读取PA1数据输出寄存器

uint8_tVal;Val=BITBAND_REG(GPIOA->ODR,1);

这里就是操作某一个地址,类似于操作指针一样;

5、位带操作优缺点

1.优点

相比直接操作寄存器代码更简洁,运行效率更高。避免在多任务,或中断时出现紊乱等。

2.缺点

操作不当(传入地址参数不对),容易出现总线Fault。

6、最后

关于Cortex-M3的位带操作,更多详情可以参看Cortex-M3技术参考手册(权威指南)。

这后面的Cortex-M处理器已经不再支持位带操作了,从兼容未来软件的角度来说,不是很建议大家再继续使用了。

只是位带操作是一种经典,这里分享给大家了解一下,希望对你们有帮助。

来源:嵌入式专栏

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理

审核编辑 黄宇

-

mcu

+关注

关注

146文章

17559浏览量

355886 -

Cortex-M

+关注

关注

2文章

229浏览量

30026

发布评论请先 登录

相关推荐

如何选择正确的Cortex-M处理器?

米尔科技Cortex-M Prototyping System +介绍

快速理解STM32位带操作原理

Cortex-M跑Linux操作系统能行吗

Cortex‐M3内核学习笔记(二):位带操作

STM32学习笔记:位带操作(Bit_band Operations)

STM32位带操作-详解-计算过程

Cortex-M位带操作的原理

Cortex-M位带操作的原理

评论