1、IAR IDE

IAR一直是Renesas强有力的合作伙伴,IAR IDE支持Renesas全系列MCU的开发和调试。IAR Embedded Workbench是一个完整的开发工具链,在易于使用的集成开发环境中提供了强大的代码优化和全面的调试功能。

2、Renesas RL78系列MCU

Renesas RL78系列MCU是Renesas 16-bit低功耗产品线,专为超低功耗设计,可以为客户提供以较低的成本建立高集成度和高效节能的应用平台。

RL78系列MCU有三大主要特点:

1)低功耗:最低46uA/MHz

2)可扩展性:1KB~512KB Flash

3)高效:最高1.39DMIPS/MHz

此外,RL78系列MCU具有超级全面的产品线,同时也在不断地推进新产品的开发,以满足客户未来的产品升级需求。

3、使用IAR IDE仿真RL78内置硬件乘法器 除法器注意事项

在使用IAR IDE进行RL78系列MCU仿真调试时,可执行硬件仿真或软件仿真(Simulator),但是,如果需要应用硬件乘法器/除法器,则必须使用硬件仿真,不能使用软件仿真(Simulator),软件仿真(Simulator)不支持MCU内部的硬件乘法器/除法器。

当执行硬件仿真时,如果不勾选“Disable Hardware Multiplier/Divider Unit”:

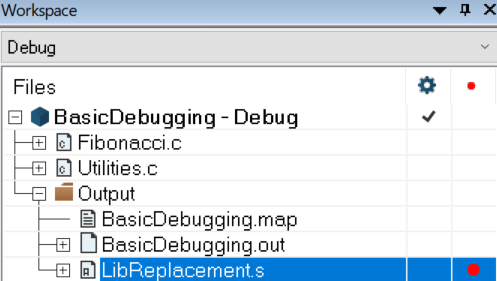

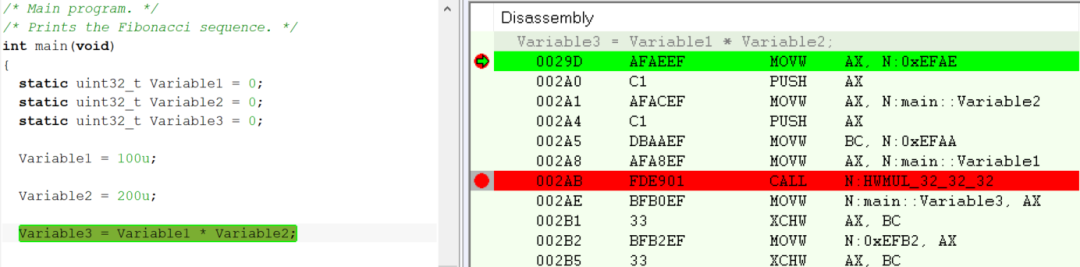

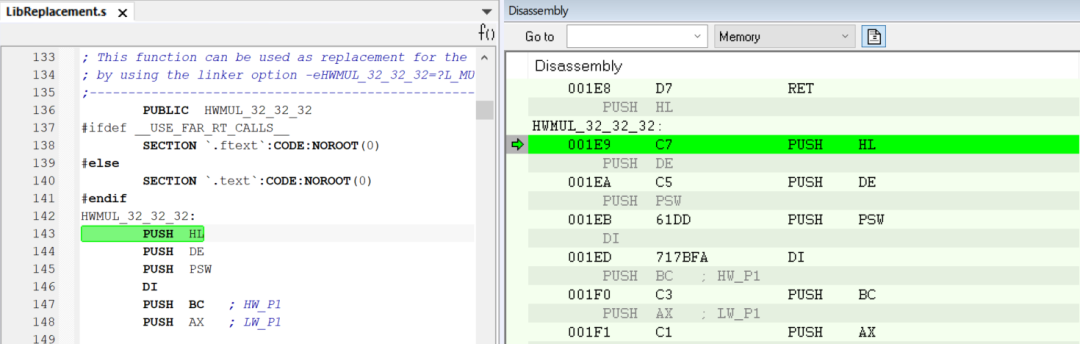

对应的乘法操作会调用函数HWMUL_32_32_32,(HWMUL_32_32_32存在于工具自动生成的文件LibReplacement.s中,当不勾选“Disable Hardware Multiplier/Divider Unit”时,会自动在Output文件夹生成LibReplacement.s文件),例如:

在程序中可以看到:

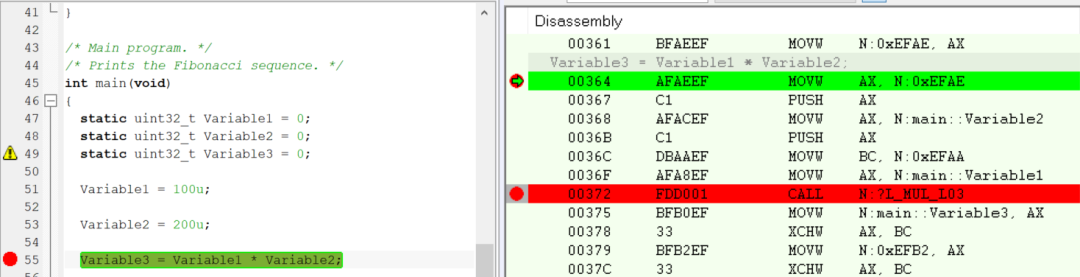

当勾选“Disable Hardware Multiplier/Divider Unit”时,编译器会选择对应的软件乘法库函数L_MUL_L03来实现乘法操作:

需要注意的是,软件乘法库函数L_MUL_L03相对于HWMUL_32_32_32函数会需要更多的资源及运行时间。

来源:瑞萨MCU小百科

审核编辑:汤梓红

-

mcu

+关注

关注

146文章

17316浏览量

352555 -

仿真

+关注

关注

50文章

4124浏览量

133955 -

IAR

+关注

关注

5文章

354浏览量

36768 -

IDE

+关注

关注

0文章

341浏览量

46865 -

除法器

+关注

关注

2文章

14浏览量

13912

发布评论请先 登录

相关推荐

硬件乘法器的相关资料分享

并行除法器 ,并行除法器结构原理是什么?

进位保留Barrett模乘法器设计

使用verilogHDL实现乘法器

乘法器原理_乘法器的作用

使用IAR IDE仿真RL78内置硬件乘法器和除法器注意事项

使用IAR IDE仿真RL78内置硬件乘法器和除法器注意事项

评论