01亚稳态理论

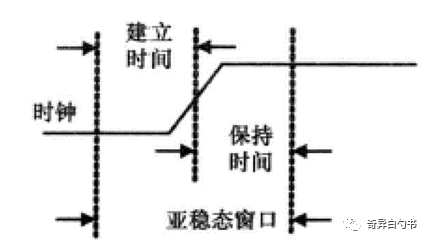

亚稳态(Metastability)是由于输入信号违反了触发器的建立时间(Setup time)或保持时间(Hold time)而产生的。建立时间是指在时钟上升沿到来前的一段时间,数据信号就要提前准备好并稳定,保持时间是指时钟上升沿到来后的一段时间,数据信号需要保持住。建立时间和保持时间是触发器的固有属性,由工艺决定。

如果数据信号在亚稳态窗口内发生变化,那么触发器的输出就会变成一段时间的“未知态”。这种状态对于电路而言是有害的,且需要一段时间才能回到稳定状态。

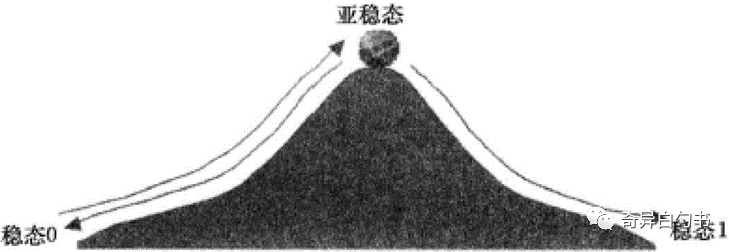

众所周知,数字电路中的稳定状态“0”或“1”一般是由TTL电平决定,所谓的亚稳态就是当触发器电平工作在低电平与高电平之间的状态,这个状态一般会在1到2个时钟周期恢复到“0”或“1”的稳定状态,但是无法确定到底回到哪个稳态。

如同在一个小土坡上滚一个球,当产生亚稳态时,可能“推力”较大,球翻过了山坡,最后回到了稳态“1”;也可能“推力”不足,球又回滚到稳态“0”,这种情况下,输出就可能产生毛刺。

02如何减少亚稳态

实际设计中,可能产生亚稳态的原因有:

- 输入信号是异步信号;

- 时钟偏移、摆动(上升/下降时间)高于容限值;

- 信号在两个没有固定相位关系的时钟域进行跨时钟域工作;

- 组合延迟使得触发器的数据输入在亚稳态窗口发生。

一个最简单粗暴的解决办法就是确保时钟周期足够长来避免亚稳态,这个时钟周期要大于准稳态的解析时间,也要大于通往下一级触发器路径上的任何逻辑延迟,不过这样做与性能要求相悖,实用性不大。因此实际工作中往往通过解决时序上的问题来降低亚稳态发生的概率:

- 跨时钟域传输可以采用同步器、握手协议等;

- 采用响应更快的触发器(缩短亚稳态窗口);

- 异步信号的采集可以采用异步FIFO对跨时钟域数据进行缓冲设计;

- 降低工作频率(就是增加时钟周期,不是优选方案)

-

TTL

+关注

关注

7文章

507浏览量

70494 -

fifo

+关注

关注

3文章

390浏览量

43930 -

数字电路

+关注

关注

193文章

1630浏览量

80895 -

触发器

+关注

关注

14文章

2019浏览量

61397 -

亚稳态

+关注

关注

0文章

47浏览量

13342

发布评论请先 登录

相关推荐

亚稳态理论知识 如何减少亚稳态

亚稳态理论知识 如何减少亚稳态

评论