前言

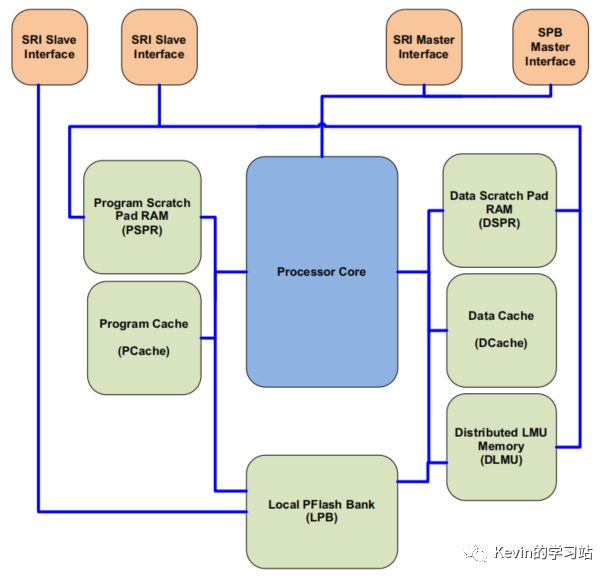

在前面的<>文章文章中我们介绍了RH850-U2A的内存保护单元(MPU),了解了MPU的概念以及在RH850-U2A上的具体使用流程,但是对于TC3xx系列芯片的的MPU功能不甚了解。本文就来详细介绍下TC3xx芯片的MPU功能。

缩略词

| 简写 | 全称 |

| MPU | MemoryProtecionUnit |

| PS | ProtectionSet |

| PSW | ProgramStateWord |

参考文档:

1. TriCoreTM TC1.6.2 core architecture manual

2. AURIXTC3XX_um_part1_v2.0.pdf

3.MPU功能详解-以RH850U2A为例

4.TC3xx芯片的Trap详解

注:本公众号文章中使用了一些第三方工具和文档,若有侵权,请联系作者删除!

正文

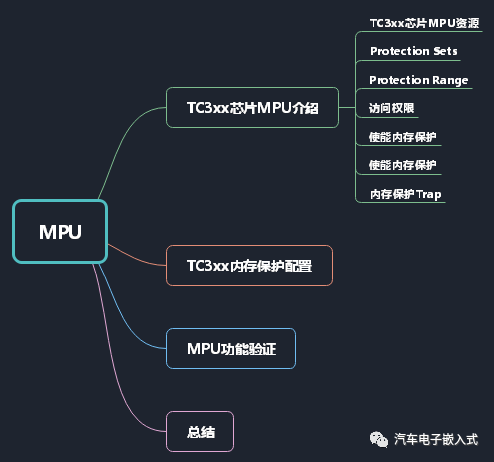

1.TC3xx芯片MPU介绍

MPU内存保护是芯片的硬件的机制,可保护用户指定的内存范围免受未经授权的读取,写入或指令提取访问的影响。通过MPU配置,把芯片的Memory划分为位若干(有大小限制)区域,每个区域可以配置读(DataRead)、写(DataWrite)、执行(CodeFetch)权限。配置MPU且使能MPU后,如果访问某个内存区域但是改内存区域没有配置对应的权限,就会产生MPUTrap。

1.1TC3xx芯片MPU资源

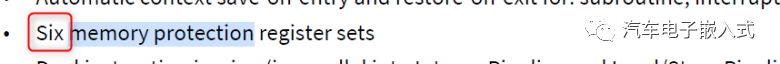

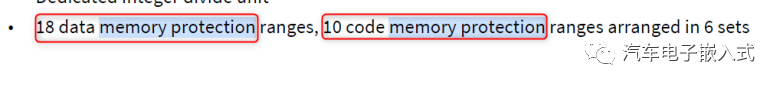

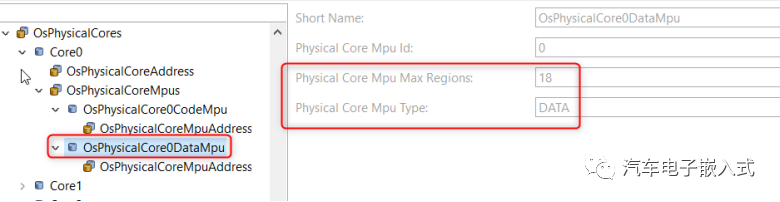

以TC37x(TC1.6.2.P内核)为例,有6个Memory Protection Register Sets;TC37x芯片有3个Core,每个核有18个Data Memory Protection Ranges,10个Code Protection Ranges。

Note: 后文会介绍什么是Memory Protection Sets,Data/Code Protection Range.

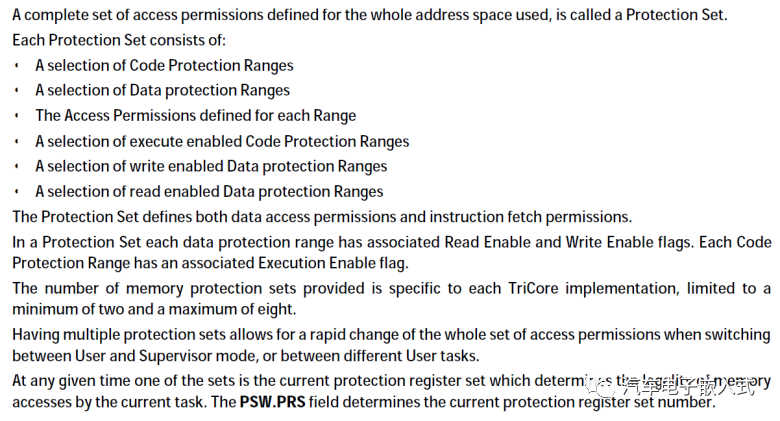

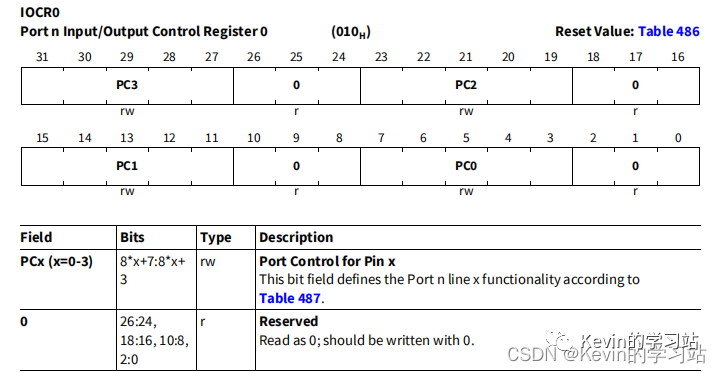

1.2 Protection Sets

官方解释:

作者理解:TC3xx芯片可以配置多种内存保护集(Sets),每种内存保护集的内存划分及其权限可以不一样,这样我们可以通过切换当前的内存保护集实现不一样的内存保护策略。程序状态字寄存器的的PRS位域(PSW.PRS)确定了当前使用内存保护集。

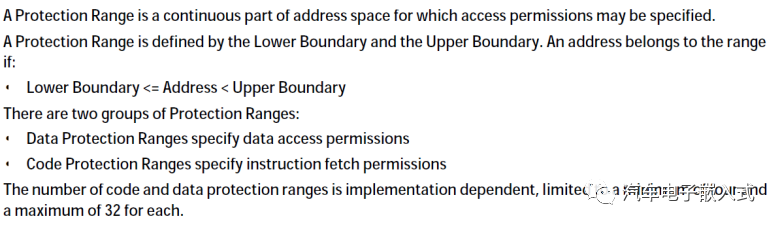

1.3Protection Range

官方解释:

作者理解:TC3xx芯片的内存保护Range的划分和RH850不一样,TC3xx的内存保护Range还区分Data Protection Ranges和CodeProtection Ranges,对于Data Protection Ranges只能Enable读、写的权限,对于Code Protection Range只能Enable可执行(Execute Access)权限。

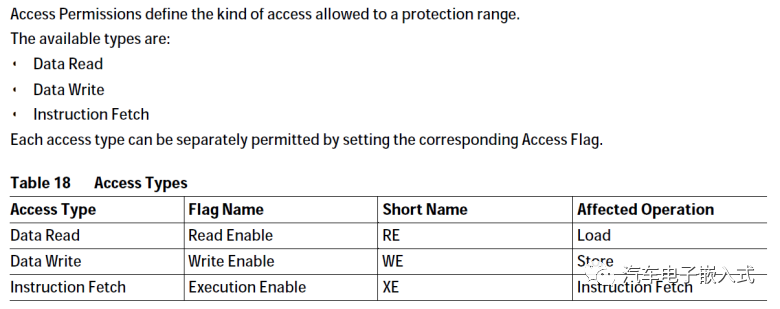

1.4访问权限

每个内存保护区域可以配置它的DataRead, Data Write, Intruction Fectch权限,不过通过1.2章节可知,DataProtection Range只能配置Data Read/Write权限,Code Protection Range只能配置Instruction Fectch权限。

Note1: 两块不同Protection Range的公共区域的访问权限是两块区域访问权限的”或”关系后的访问权限。

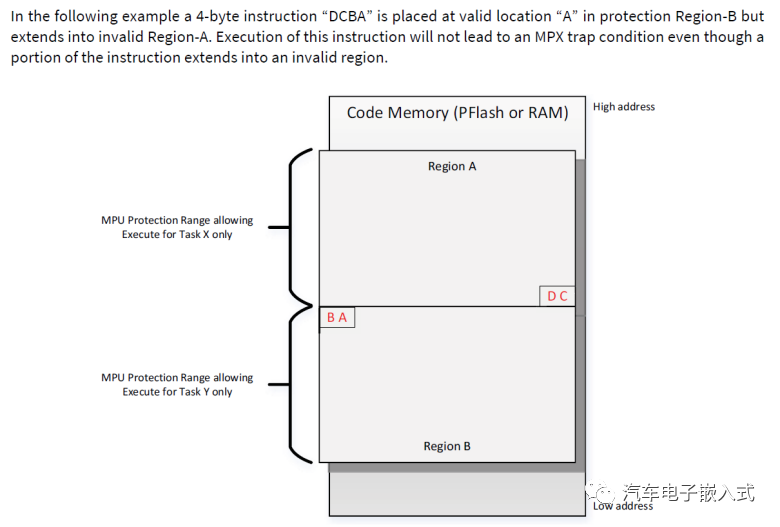

Note2: 跨Protection Range的访问不会产生Trap。

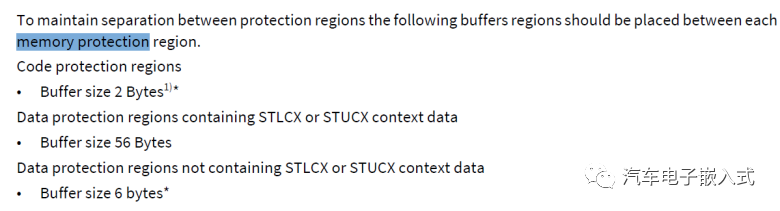

Note3: 为了保持Protection Regions的分离性,Protection Region间应该有空置的区域。

1.5使能内存保护

配置SYSCON.PROTEN == 1即使能内存保护功能。

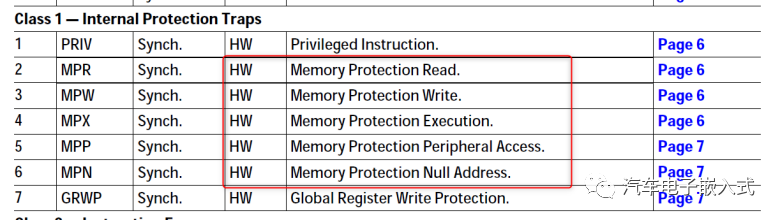

1.6内存保护Trap

使能了内存保护后,如果产生Error,就会触发对应的Trap。可以参考<>一文。

2.TC3xx内存保护配置

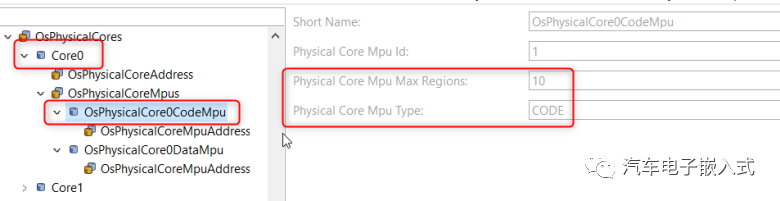

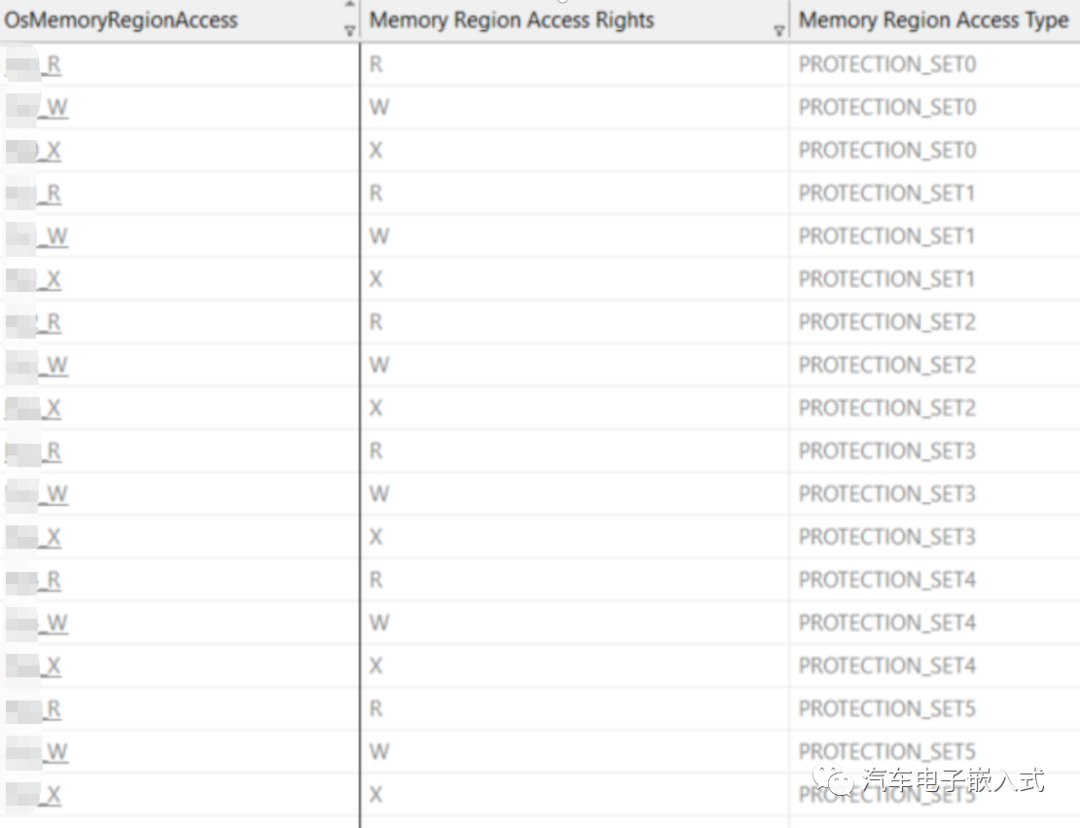

ProtectionsSets和Code/Data Protection Type在DavinciConfigurator的SIP包中根据定制的芯片类型以及预定义好的,只要使用的在配置Protection Range的时候引用就行。

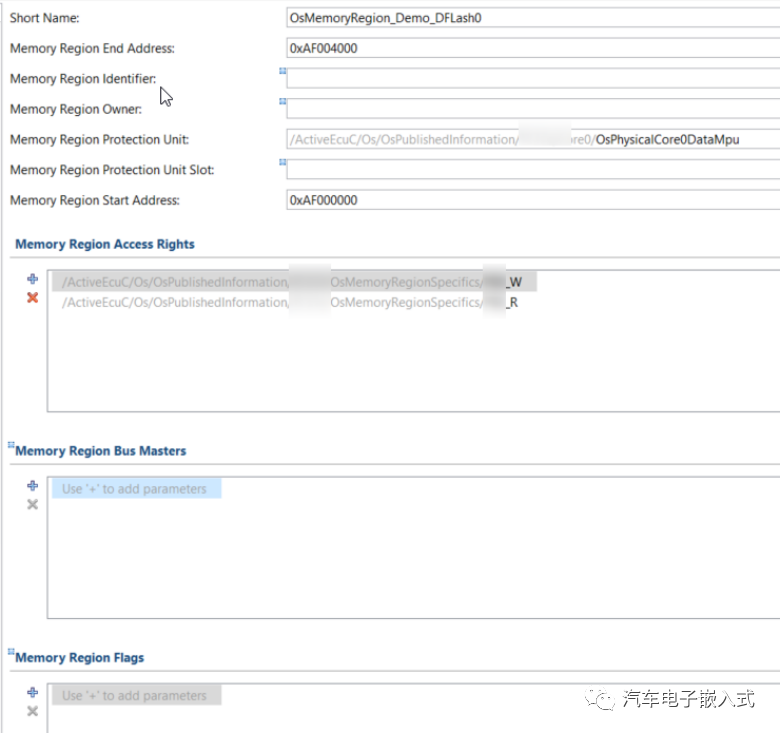

如上图所示,我们配置了一个Data Protection Ranges,给DFlash0配置上MPU权限:

Short Name: Protection Ranges的名字。

Memory Region End Address: Protection Ranges的结束地址,必须是8字节的整数倍,且应该大于等于StartAddress.

Memory Region Identifier: 定义可选的特定于硬件的内存保护区域标识符。不是必须配置项,一般不用配置。

MemoryRegion Owner: 指定内存保护区域是特定于OS-Applicaiton,Task, ISR ,还是全局的。如果引用了Task, ISR后,只有进入到对应的Task,ISR后该Protection Ranges才被激活。如果没有引用,则该Protection一直是被激活的。

Note: 这个配置项需要谨慎配置,如果不是很确定,建议不要配置,也就是Global的。因为,比如,我给该Protection Ranges配置了一个Task,那么该ProtectionRange只有该Task才能读写,如果有其他的Task也读写该Protection Ranges的话,就会产生MPUTrap。

Memory Region Protection Unit: 配置该Protection Range属于哪一个Core的Data/Code MPU Protection Ranges。

Memory Region Protection Unit Slot: 和硬件特性相关,可以不用配置。

Memory Region Start Address: Protection Ranges的起始地址,必须是8字节的整数倍,且应该大于等于EndAddress.

Memory Region Access Rights: 选择预定义好的Protection Set的权限。

3.MPU功能验证

参考:<>

着重理解Trap产生后如何定位发生Trap的位置及产生Trap的原因。

4.总结

使能MPU功能后,MCU的所有内存访问都会被监控,一单出现非预期内的内存访问就会触发MPU的保护,产生MPUTrap。根据使用经验,MPU是把双刃剑,用的好能把一些偶发内存异常访问问题扼杀在开发阶段,也能利用MPU来定位内存非法访问问题。用的不好,就会导致系统经常进入Trap(一般都会走Reset)。如果项目要上MPU,建议提前规划好MPU Protection Ranges及其访问权限,这样经过大量的开发过程验证才能确保MPU达到正向监控的作用,而不是出现反作用。

审核编辑:汤梓红

-

芯片

+关注

关注

459文章

51680浏览量

430584 -

MPU

+关注

关注

0文章

391浏览量

49249 -

内存保护单元

+关注

关注

0文章

6浏览量

1637

原文标题:TC3xx芯片MPU介绍

文章出处:【微信号:汽车电子嵌入式,微信公众号:汽车电子嵌入式】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

英飞凌TC3XX系列多核MCU学习笔记(3)

TC3XX寄存器读写时间过长怎么解决?

TC3xx系列怎么禁用trap?

TC3xx的HSM中有没有单调计数器?

TSIM是否支持TC3xx系列在没有硬件的情况下调试应用程序?

AUTOSAR MCAL-基于Infineon TC3xx芯片的ADC模块

TC3xx芯片DMU介绍

TC3xx芯片的MPU功能详解

TC3xx芯片的MPU功能详解

评论