1、语法说明

在rtl仿真中,有四种状态,分别是0、1、x(unknown values)和z(high-impedance values)。

case 结构体中:0,1,X与Z是四种不同的状态,case条件比较时会检测比较双方每个bit是否完全相等。

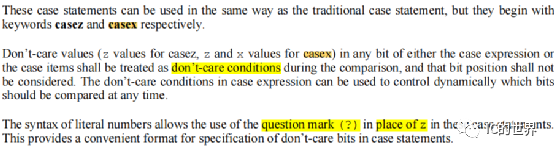

casez 结构体中:把Z当做don’t care conditions,case条件比较时,比较双方存在Z值的bit位不参与比较 ,其他比特位相等则视为条件命中

casex 结构体中:把Z和X当做don’t care conditions,case条件比较时,比较双方存在Z或者X的bit位不参与比较,其他比特位相等则视为条件命中

在SystemVerilog和Verilog中,

case、casex、casez都是可综合的

在casex、casez中推荐使用 ?来替换Z和X

case、casex、casez语句中,如果命中多个case条件,则执行命中的第一个case

2、案例解析

always@(*)

begin

case(sel[1:0])

2'b00: data1 = 3'd0 ;

2'b01: data1 = 3'd1 ;

2'b10: data1 = 3'd2 ;

2'b11: data1 = 3'd3 ;

2'b1z: data1 = 3'd4 ;

2'b1x: data1 = 3'd5 ;

default: data1 = 3'd7 ;

endcase

end

always@(*)

begin

casez(sel[1:0])

2'b00: data2 = 3'd0 ;

2'b01: data2 = 3'd1 ;

2'b10: data2 = 3'd2 ;

2'b11: data2 = 3'd3 ;

2'b1z: data2 = 3'd4 ;

2'b1x: data2 = 3'd5 ;

default: data2 = 3'd7 ;

endcase

end

always@(*)

begin

casex(sel[1:0])

2'b00: data3 = 3'd0 ;

2'b01: data3 = 3'd1 ;

2'b10: data3 = 3'd2 ;

2'b11: data3 = 3'd3 ;

2'b1z: data3 = 3'd4 ;

2'b1x: data3 = 3'd5 ;

default: data3 = 3'd7 ;

endcase

end

always@(*)

begin

casez(sel[1:0])

2'b00: data4 = 3'd0 ;

2'b01: data4 = 3'd1 ;

2'b10: data4 = 3'd2 ;

2'b11: data4 = 3'd3 ;

2'b1?: data4 = 3'd4 ;

2'b1x: data4 = 3'd5 ;

default: data4 = 3'd7 ;

endcase

end

always@(*)

begin

casex(sel[1:0])

2'b00: data5 = 3'd0 ;

2'b01: data5 = 3'd1 ;

2'b10: data5 = 3'd2 ;

2'b11: data5 = 3'd3 ;

2'b1?: data5 = 3'd4 ;

2'b1x: data5 = 3'd5 ;

default: data5 = 3'd7 ;

endcase

end

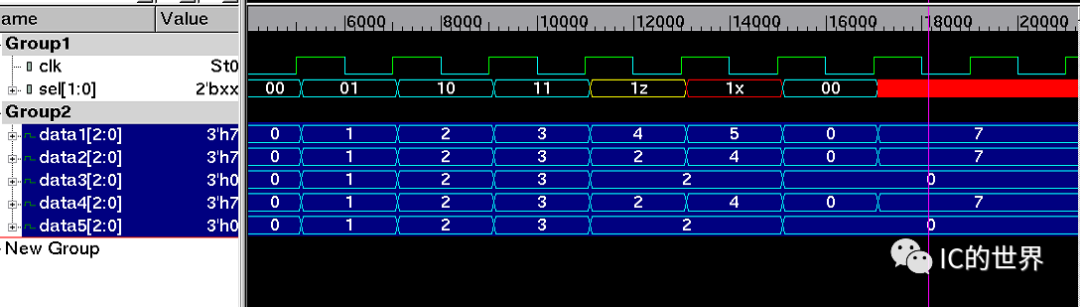

case语句中4种状态都会比较匹配sel[1:0]为1’b1z时,命中了[2'b1z: data2 = 3'd4 ;],data1被赋值3’d4

sel[1:0]为1’b1x时,命中了[2'b1x: data2 = 3'd5 ;],data1被赋值3’d5

casez语句中Z状态会被忽略,不做比较,X依旧进行比较

sel[1:0]为1’b1z时,实际仅比较sel[1],命中了[2'b10: data2 = 3'd2 ;]和[2'b1z: data2 = 3'd4; ],根据优先级原则, data2被赋值3’d2

sel[1:0]为1’b1x时,依旧比较sel[1:0],命中了[2'b1x: data2 = 3'd5 ;], data2被赋值3’d5

casex语句中Z和X状态会被忽略,不做比较

sel[1:0]为1’b1z时,实际仅比较sel[1],命中了[2'b10: data2 = 3'd2 ;], data3被赋值3’d2

sel[1:0]为1’b1x时,实际仅比较sel[1],命中了[2'b10: data2 = 3'd2 ;], data3被赋值3’d2

casez语句中采用?替换Z状态

sel[1:0]为1’b1z时,实际仅比较sel[1],命中了[2'b10: data2 = 3'd2 ;], data4被赋值3’d2

sel[1:0]为1’b1x时,同时命中了[2'b1?: data4 = 3'd4 ;]和[2'b1x: data4 = 3'd5 ;],根据优先级原则,data4被赋值3’d4

casex语句中采用?替换Z状态

sel[1:0]为1’b1z时,实际仅比较sel[1],命中了[2'b10: data2 = 3'd2 ;]、[2'b1?: data5 = 3'd4 ;]、[2'b1x: data5 = 3'd5 ;],根据优先级原则,data5被赋值3’d2

sel[1:0]为1’b1x时,实际仅比较sel[1],命中了[2'b10: data2 = 3'd2 ;]、[2'b1?: data5 = 3'd4 ;]、[2'b1x: data5 = 3'd5 ;],根据优先级原则,data5被赋值3’d2

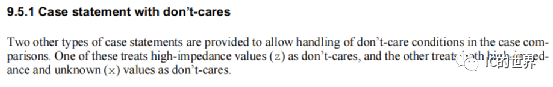

3、Do-not-care values 参考说明

SystemVerilog(IEEE Std 1800-2017)和verilog(IEEE P1364-2005)标准关于casez、casex的描述是一致的:截图如下:

审核编辑:汤梓红

-

仿真

+关注

关注

50文章

4080浏览量

133586 -

Verilog

+关注

关注

28文章

1351浏览量

110091 -

RTL

+关注

关注

1文章

385浏览量

59772 -

语法

+关注

关注

0文章

44浏览量

9810 -

结构体

+关注

关注

1文章

130浏览量

10841

原文标题:verilog语法-浅谈case casez casex

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

零基础学FPGA(四)Verilog语法基基础基础(中)

新人求教关于case的语法问题:case里2个端口是什么意思?

在SpinalHDL中关于casez的使用

verilog中if与case语句不完整产生锁存器的原因分析

关于verilog的学习经验简单分享

一文浅析case、casex、casez区别

Verilog语法之generate for、generate if、generate case

Verilog中的If语句和case语句介绍

CASE:创建多路分支

verilog语法说明之case casez case

verilog语法说明之case casez case

评论