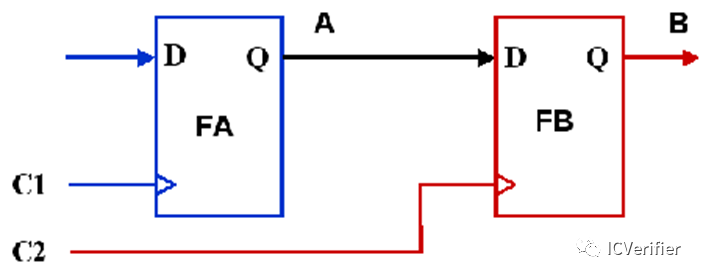

跨时钟域( Clock Domain Crossing,CDC )通俗地讲,就是 模块之间数据交互时用的不是同一个时钟进行驱动 ,如下图所示:左边的模块FA由C1驱动,属于C1时钟域;右边的模块FB由C2驱动,属于C2时钟域。

跨时钟域信号处理问题,首先要考虑的就是亚稳态问题。

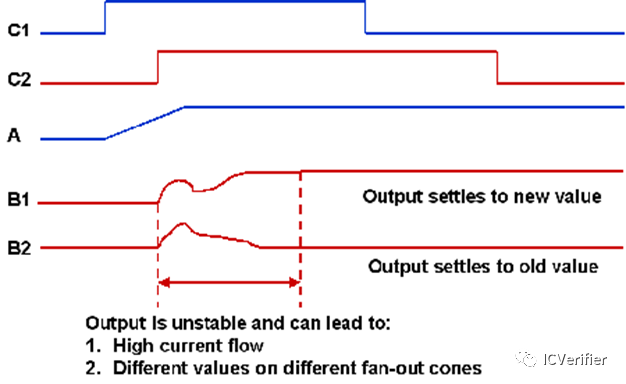

为了使触发器正常工作,输入信号和时钟必须满足触发器的建立和保持时间要求。在上面的图2中,信号A与目标时钟域C2是异步的,因为C1和C2属于不同时钟域。一旦遇到异步信号进入时钟域,就不太可能满足建立和保持时序约束,因此触发器可能以进入亚稳态。在下图中,FA的输出信号A变化非常接近C2的时钟边缘,因此违反了FB的建立时间要求, 它可能导致目标触发器FB违反setup或hold时间。输出信号B可能会振荡不确定时长。因此输出是不稳定的,也可能会在C2的下一个时钟边缘到达之前稳定到某个值,这种现象被称为亚稳态。

如果输入信号A变化非常接近时钟C2的上升沿,那么目标触发器的输出是亚稳态的。因此,可能最终稳定到信号B1和B2所描述的1或0。

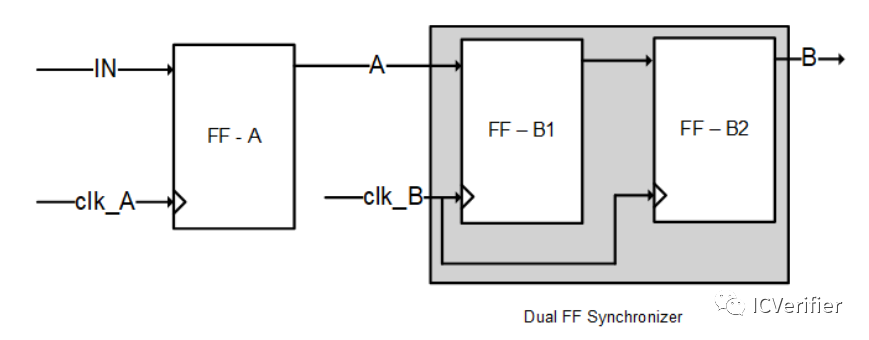

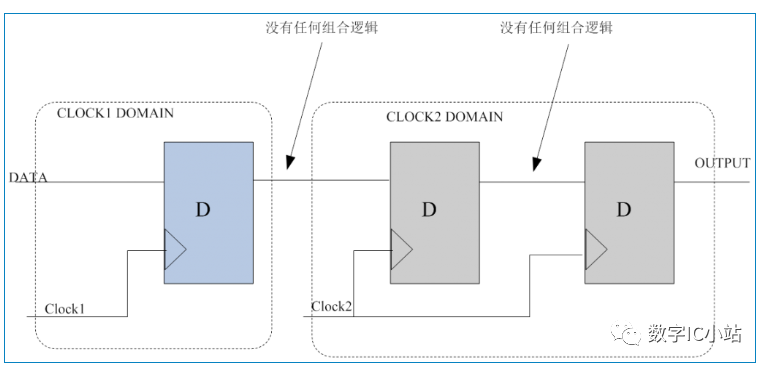

处理跨时钟域**(CDC)信号同步**的最常见方法之一是使用同步器电路。同步器电路的目的是通过最小化亚稳态的可能性和增加MTBF来保护下游逻辑。其中一个基本的同步器电路是 两级触发器同步器 (也称为2-FF同步器)。

2-** FF同步器处理跨时钟域信号同步**

两级触发器同步器是一种电路,其中两个触发器在目标时钟域中背靠背连接。如果第一个触发器由于建立/保持冲突而进入亚稳态,则第二个触发器会提供足够的时间让第一个触发器脱离亚稳态。从理论上讲,当第二个FF对值进行采样时,第一个FF可能仍处于亚稳态,因此可以对不正确的值进行采样,使用超过2级FF作为同步器(3或4级FF),可以增加MTBF。

2-FF同步器电路非常适合单比特控制信号的同步 ,其中输入切换速率小于目标时钟频率,换句话说,如果目标时钟频率超过源时钟频率的1.5倍,则不会丢失数据 。但是,如果源和目标时钟频率几乎相同或目标时钟频率较慢,则源必须保持其值稳定,以便目标捕获它,然后再更改为下一个值。这可以通过 握手时钟域交叉 (CDC)技术来处理。

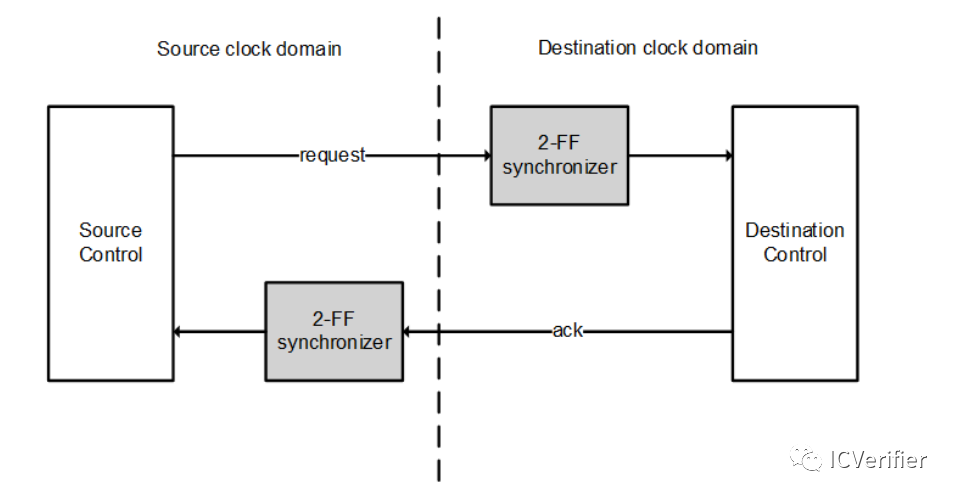

握手机制处理跨时钟域信号同步

在握手技术中,源时钟域将**“请求”信号**发送到使用 2-FF同步器的目标域。一旦目标域收到请求,它就会向源域发送“ack”信号,该源域使用 2-FF 同步器进行同步。ack 信号向源时钟域指示目标已收到该值,源时钟域可以更新其值。握手机制有许多实现版本,但原理保持不变: 同步request和ack信号 。request信号将在总线上指示一个新值即将发送,ack信号将指示可以更新数据总线。

上述机制在接口的带宽使用方面确实有一个缺点。对于握手机制,数据总线在接收ack信号时无法更新,存在瓶颈,可以使用双时钟异步FIFO来解决这个问题。正确设计的FIFO可以增加整个接口的带宽,同时仍然保持跨时钟域的可靠通信。

异步FIFO可以被视为数据容器,其中发送方以源时钟速率将数据写入,接收器以目标时钟速率弹出数据。FIFO的深度应该足够,以便它不能溢出或下溢数据。

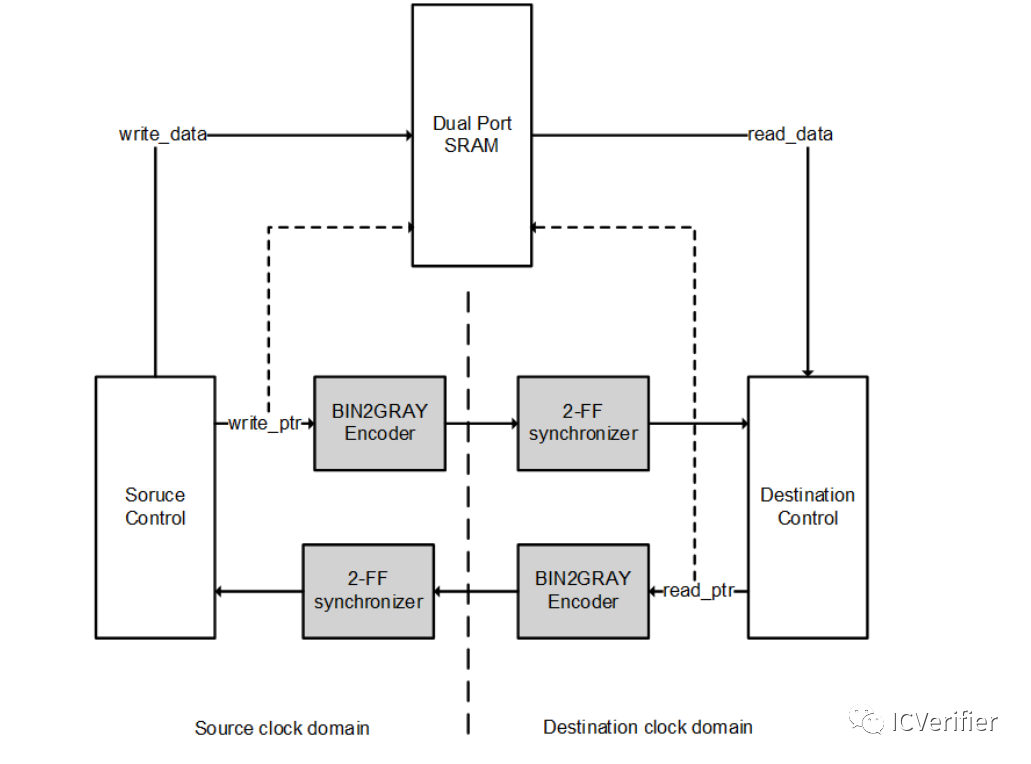

异步FIFO处理跨时钟域信号同步

时钟异步FIFO需要用到双端口SRAM,一个控制写入指针(数据应在SRAM中写入的地址)的源代码控制块,一个生成读取指针(应在SRAM中读取数据的地址)的目标控制块和二进制到格雷码编码器块以及2-FF同步器电路。指针由各自的控制块作为循环缓冲区进行管理。但是,要知道何时写入(FIFO 未满)和何时读取(FIFO 不为空),源时钟、目标时钟控制块需要分别具有读取和写入指针信号。将指针传输到另一个时钟域并非易事。由于指针是多位信号,因此直接使用2-FF同步器不是一个好的选择。因此,两个指针都通过二进制到格雷码编码块传递。这确保了在传输值时,只有矢量的一个位从一个时钟更新到另一个时钟,从而消除了在时钟边沿上同步多位总线的问题。

-

触发器

+关注

关注

14文章

2000浏览量

61229 -

同步器

+关注

关注

1文章

98浏览量

14656 -

FIFO存储

+关注

关注

0文章

103浏览量

6018 -

时钟驱动器

+关注

关注

0文章

33浏览量

13862 -

SRAM存储器

+关注

关注

0文章

88浏览量

13349

发布评论请先 登录

相关推荐

处理跨时钟域(CDC)信号同步的最常见方法

处理跨时钟域(CDC)信号同步的最常见方法

评论