1.基本原理

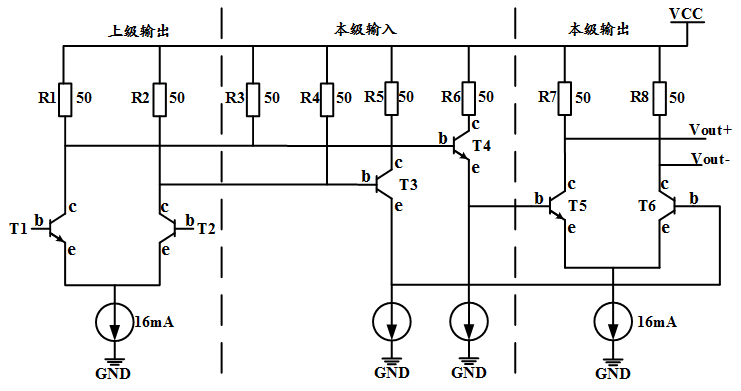

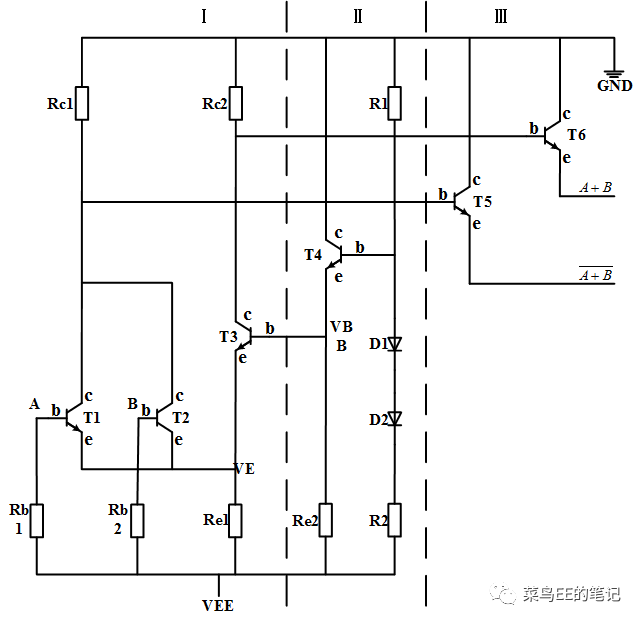

CML电路如图1 所示,输入部分为一射随器,假设T3管为N端,T4管为P端,当P大于N时即输入为高电平,反之为低电平。由于输入部分为射随器,输出端接收到高低电平的相位与输入端一致,当接收为高电平时,T5导通,其射极电位被钳位,导致T6截止,16mA电流均从T5流过,此时输出为低电平。输入为低时情况类似。可见,CML输入输出存在倒相的关系。

图1

2.为什么CML电路差分输出需要一个16mA的电流源?

差分放大电路使用一个电流源进行偏置,可以提高其共模抑制比,并且提供一个稳定的静态工作点(差分放大电路的具体分析另起一文)。电流源的大小影响的是输出电平的摆幅,而摆幅会影响传输的速率、距离以及电路的功耗,16mA应为综合考虑以上因素得到的一个标准(具体未考证)。

- 相关计算

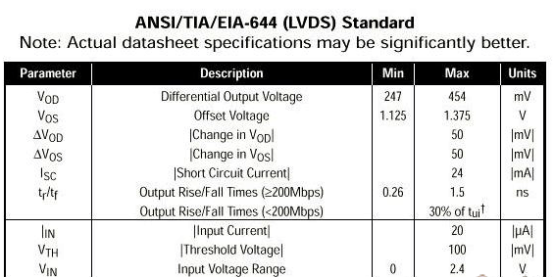

一般资料中对CML电平输入输出相关参数的描述如下:假定CML 输出负载为一50Ω上拉电阻,直流耦合时,单端CML 输出信号的摆幅为Vcc ~ Vcc-0.4V。在这种情况下,差分输出信号摆幅为800mV,共模电压为Vcc-0.2V。若CML输出采用交流耦合至50Ω负载,CML 输出共模电压变为Vcc-0.4V,单端CML 输出信号的摆幅为Vcc-0.2~Vcc-0.6V,差分信号摆幅仍为800mV。那么,以上数据是怎么来的呢?

直流耦合:

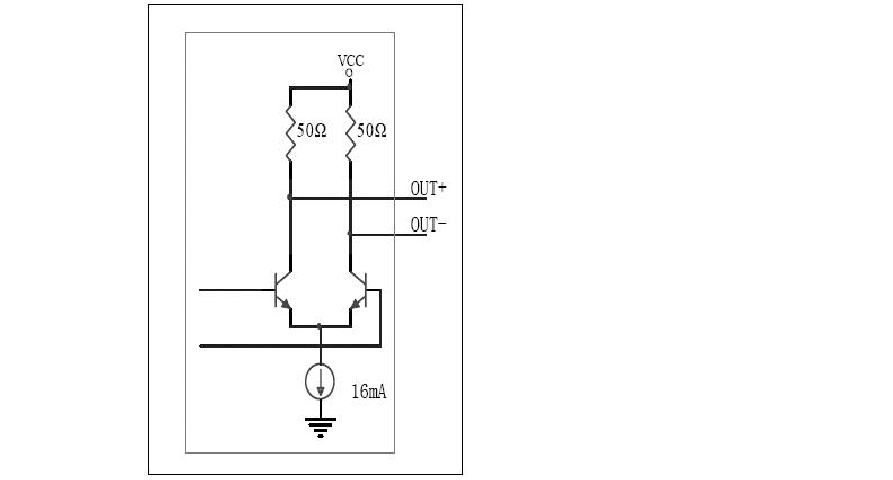

直流耦合时,差分对的电流回路如图2所示。输出差分对的直流、交流回路是一致的。首先对其进行静态分析,由于T1、T2参数对称,故16mA电流平均流过T1、T2,每个管流过8mA的电流,分到R1~R4四个电阻上,每个电阻流过的电流为4mA,所以直流耦合时的共模电压为:

当有差模电压输入时,T1、T2只会导通一个(以T1导通为例),16mA电流由R1、R3一起提供,每个电阻提供8mA电流,因此单端摆幅为:

图2

由共模电压定义:

设单端输出电压高电平为x,低电平为x-0.4,差分输出时一端为高另一端为低,则有:

解得,x为VCC,单端电压变化范围为VCC~VCC-0.4。

那么,为什么差分摆幅为800mV呢?

当T1导通、T2截止时,VOUT-为VCC,VOUT+为VCC-0.4V,两者压差为400mv;当T2导通、T1截止时,VOUT+为VCC,VOUT-为VCC-0.4V,两者压差也为400mv,似乎差分摆幅也应该为400mv,实则不然。分析如下:

当T1导通、T2截止时,VOUT-为VCC,VOUT+为VCC-0.4V,此时为输出差分电压的低电平,其值为:

当T2导通、T1截止时,VOUT+为VCC,VOUT-为VCC-0.4V,此时为输出差分电压的高电平,其值为:

故差分摆幅为:

交流耦合:

交流耦合时,T1、T2的电流回路如图3所示。首先进行静态分析,由于电容的隔直作用,R3、R4不能向T1、T2提供直流分量,所以16mA电流由R1、R2提供,流过每个电阻的电流为8mA,可得共模电压为:

图3

当有差模电压输入时,T1、T2只会导通一个(以T1导通为例),由于电容通交流,16mA电流由R1、R3一起提供,每个电阻提供8mA电流,因此单端摆幅为:

单端电压的输出范围为VCC-0.2~VCC-0.6V,差分摆幅为800mV交流耦合时(以T1导通为例),16mA电流均流过T1一个管,但是输出电压最大为VCC-0.2,表示即使在T2截止,R2上也有电流流过,且流向只能时通过电容、R4、形成回路,这个电流应为应为电容放电过程产生的电流。

根据CML的电路分析,其输入输出电平为固定的,因此电平门限无需讨论。

-

电平

+关注

关注

5文章

361浏览量

40037 -

差分放大电路

+关注

关注

18文章

161浏览量

50069 -

CML

+关注

关注

0文章

32浏览量

19460 -

差模电压

+关注

关注

0文章

24浏览量

8519 -

射随器

+关注

关注

0文章

8浏览量

8975

发布评论请先 登录

相关推荐

LVDS、CML、LVPECL不同逻辑电平之间的互连(二)

浅谈LVDS、CML、LVPECL三种差分逻辑电平之间的互连

hdmi是什么电平?hdmi信号里有几对差分还有几个单端的,差分的信号是不是cml电平?

比较器ADCMP606的CML输出只想用到CML的正极作为输出,负极接地可以吗?

差分逻辑电平,LVDS、xECL、CML、HCSL/LPHCSL、TMDS等

ADCMP606是CML差分电平输出,用到CML的正极作为输出,负极接地可以吗?

SN65CML100 1.5Gbps LVDS/LVPECL/CML 至 CML 转换器/中继器

LVDS和CML与LVPECL的同种差分逻辑电平之间的互连教程

详解信号逻辑电平标准:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML资料下载

CML电平学习笔记

CML电平学习笔记

评论