点击上方蓝字关注我们

随着网络技术的不断发展,数据交换、数据传输流量越来越大。尤其像雷达,气象、航天等领域,不仅数据运算率巨大,计算处理复杂,而且需要实时高速远程传输,需要长期稳定有效的信号加以支持,以便能够获得更加精准的数据收发信息,更好的为工程项目服务。传统的并行传输方式由于走线多、信号间串扰大等缺陷,无法突破自身的速度瓶颈。而串行传输拥有更高的传输速率但只需要少量的信号线,降低了板开发成本和复杂度,满足高频率远距离的数据通信需求,被广泛应用到各种高速数据通信系统设计中。

目前,高速串行接口取代并行拓扑结构已经是大势所趋。当今很多公用互连标准(如USB,PCI-Express)都是基于串行连接来实现高速传输的。相比于并行总线,串行连接的物理紧密度和链路韧性具有很多优势。因此,很多传输领域都转向了串行传输,如笔记本电脑显示互连、高速背板互连和存储器内部互连。该系统涉及到的技术主要包括:光纤传输、PCIE(PCI-Express)传输和DDR缓存技术,以及这几种技术在FPGA中融合为一个完整的串行传输链路,并实现了在两台服务器之间的高速数据传输测试,这对于实际工程应用具有重要的现实意义。

1 系统结构

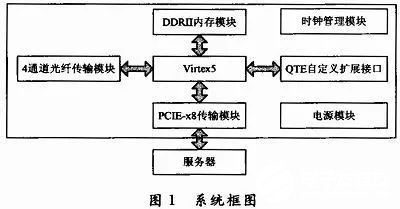

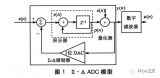

高速串行传输系统作为数据采集、传输、存储中的一部分,对传输性能指标有着严格的要求。该系统要完成光信号到PCI-Express接口信号的相互转换,并在转换过程中完成数据的高速传输。信号一般可达4.25Gb/s,处理如此高的数据对硬件设计提出了很大的挑战。其中所包含的硬件有:高速光电转换电路,FPGA数据处理电路、DDRⅡ数据缓存电路、时钟管理电路、PCIE传输模块电路、电源模块电路、自定义扩展接口电路。系统框图如图1所示。

技术要求主要有以下几点:首先,传输卡中的4个光纤通道,每通道要达到2 Gb/s以上。其次,PCIE传输速率不小于6 Gb/s,支持DMA传输。再有,光纤和PCI-E传输误码率要小于1×10-10,连续传输相对稳定。

图1中各个模块的功能如下:Virtex5作为传输卡的核心,用来实现数据从光纤接口到PCIE接口的高速转换。光纤传输模块的作用是将内部数据经过编码后,通过光缆传输给接收系统,以及接收外来光数据,并将光数据传送给FPGA处理电路DDR缓存模块的作用,就是将传输过程中的高速数据,进行缓存,以保持数据的完整性。PCI-Express传输模块的作用,就是与PC之间实现PCI-Express传输协议,与PC实现串行数据传输,同时与外部扩展接口,DDR缓存,光纤传输模块实现内部并行数据的交换。QTE自定义接口模块的作用,就是进行外部功能扩展。比如,可以扩展高速数据采集板卡、存储硬盘卡、图像采集卡等。时钟管理模块的作用,是给光纤传输模块提供参考时钟。时钟频率由FPGA的时钟控制模块控制。根据光模块的性能,给出指定的时钟。PCI-Express的参考时钟,是通过芯片从PC主板上提取的。电源管理模块的作用,是给整个系统提供各种不同的电压。

2 系统模块设计与实现

为了实现所要求的系统配置,更好地发挥各模块自身及相互之间的作用,必须对模块间进行系统的协议分析。该系统的数据传输是双向的,既可以传输数据,也可以接收数据。它主要由电源管理模块,时钟管理模块,PCI-Express传输模块,DDR缓存模块,光纤传输模块和外部扩展接口组成。其中,时钟控制模块和AURORA发送模块、Aurora接收模块是整个设计的重点。

2.1 时钟控制模块

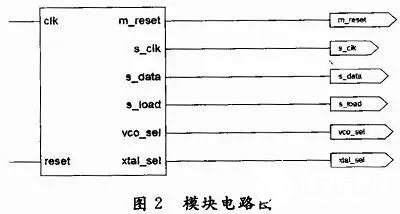

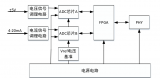

时钟控制模块主要用来控制FPGA外围的时钟芯片ICS8442来产生所需要的高信噪比、低抖动的差分时钟。其模块电路如图2所示:输出其中的信号用来完成对ICS8442的编程,使其能够产生所需要的时钟信号。

ICS8442的性能参数如下:输出信号频率范围为31.25~700 MHz;晶振频率范围为10~25 MHz;VCO频率范围为250~700 MHz;ICS8442是LVDS逻辑电平,具有极低的相位噪声,这种特性使它非常适合用来为吉比特以太网或同步光纤网提供时钟信号。

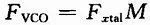

ICS8442的内部结构图3所示。ICS8442内部有一个完整的PLL锁相环,其VCO的输出频率范围在250~700MHz之间,倍频系数是由M决定的,M的取值范围在10~28之间。VCO的输出频率为:

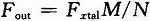

ICS8442最终的输出结果还要经过一个分频器N,最终输出结果的频率和晶振输入频率的关系式为:

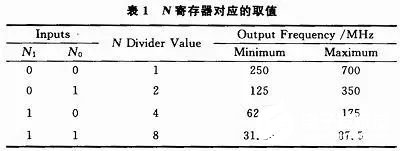

其中:N是一个2位的寄存器,其对应的取值如表1所示。

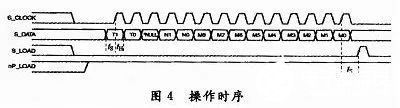

对ICS8442时钟芯片的操作主要是对寄存器M,N的写操作。ICS8442支持并行写操作和串行写操作,根据硬件电路的设计,程序采用串行的写操作时序。当ICS8442的nP_LOAD置为高电平和S_LOAD置为低电平时,芯片实现串行操作。操作时序如图4所示。

当S_LOAD置为低且nP_LOAD置为高之后,数据在S_CLOCK的上升沿处寄存在缓冲器中,在S_LOAD的下降沿处将数据锁存到寄存器M,N中。

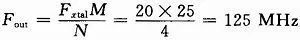

由于AURORA光纤通信的输出时钟频率设定的是125 MHz,结合硬件电路的设计,硬件晶振的频率为20 MHz,因此选择M值为000011001(25),N的值为10(4),故时钟芯片的时钟输出频率为:

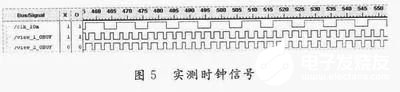

时钟控制模块的实测时钟信号如图5所示。

图5是用Chipscope在线逻辑分析仪得到的波形,由于Chipscope在线逻辑分析仪的触发时钟是100 MHz,因此在抓取125 MHz的时钟信号时,在图上显示的时钟信号占空比不定,若将时钟芯片产生的时钟频率降低,则此现象消失。

2.2 AURORA发送模块

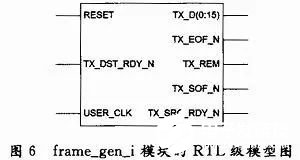

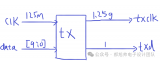

在生成AURORA IP CORE时,同时生成了一个基于AURORA协议的例示程序。因此,要实现基于AURORA协议的光纤通信,在发送端只需要在frame_gen_i模块将要发送的数据打包,然后通过AURORA模块发送出去。因此该模块着重介绍如何将上一级传送过来的数据进行打包压缩,形成适合AURORA协议的数据帧,通过AURORA协议发送到接收端。图6为frame_gen_i模块的RTL级模型图。

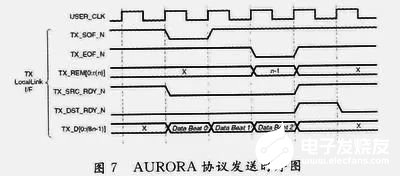

考虑到上一级传输数据速率可能会与AURORA传输的时钟频率不同,因此在发送端建立一个FIFO来做缓冲器。并且AURORA协议的发送时序图如图7所示。可以看出,TX_SOF_N为数据包帧的开始标志,TX_EOF_N为数据包帧的结束.标志,TX_REM[0:r(n)]记录最后的传输数据的线程,TX_SRC_RDY_N为低代表数据有效,TX_DST_RDY_N为低代表准备好接受数据,TX_D[0:(8n-1)]是此模块的输出数据。以上信息是AURORA协议的发送时序,在使用FIFO做缓冲时也应该遵循这样的协议。

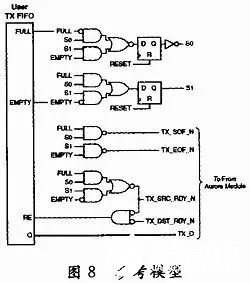

发送端的FIFO模块分别包括FIFO的复位信号、FIFO空、FIFO满、以及读/写时钟、使能和数据信号线。因此应该根据FIFO的标志位empty和full来产生AURORA的发送时序,参考模型如图8所示:当RESET信号到来之时,首先将S0置为高电平,将S1置为低电平,同时根据FULL和EM-PTY的状态确定接下来的S0和S1的状态,进而根据以上逻辑关系得到TX_SOF_N,TX_EOF_N,TX_SRC_RDY_N等逻辑信号,并且根据数据X_DST_RDY_N和TX_SRC_RDY_N生成FIFO的读使能。由以上逻辑可以看出,只有在FULL为1,EMPTY为0时,FIFO的读使能才能被打开。TX_SOF_N为数据包的帧头标志,TX_EOF_N为数据包的帧尾标志,TX_STC_RDY_N为低时代表数据有效,TX_DST_RDY_N为输入信号,根据此输入信号确定FIFO的读写时序。

对FIFO时序操作需要根据上述电路图所产生。在上述电路图中,有一个D触发器,其RESET信号是复位信号,复位既是将触发器输出端口清零,即将S0置1,将S1置0。在之前的程序中误将这里写反,即RESET信号到来之后,将S0置0,S1置1。这样导致的结果是在最开始输入的一段数据丢失,之后的结果输出正常。经过仿真分析之后检查出问题并已改正。

2.3 AURORA接收模块

同样在AURORA协议模块中,要实现对数据的接收,只需在frame_check模块中对接收的代码加以修改,增加自己所需要的内容,完成对数据的解码提取,剔除冗余信息,并完成数据的缓存。

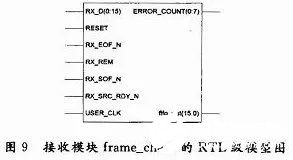

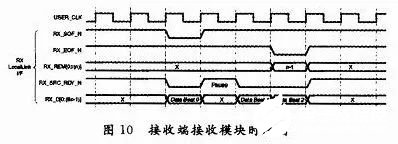

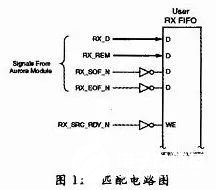

接收模块frame_check的RTL级模型图如图9所示:其中,RX_D为接收端接收的缓存于FIFO的数据,REsET为复位信号,RX_EOF_N为数据包帧尾的标志,RX_SOF_N为数据包帧头的标志,TX_SRC_RDY_N为低时代表数据有效,USER_CLK为系统时钟。fifo_out为数据缓存的输出,ERROR _COUNT为系统检错输出结果。因此在接收端接收模块的时序图如图10所示。根据该时序图可以确定接收时序,同样,在AURORA协议末端,由于与下一级系统的速率可能不匹配,因此需要在接收末端加上一个FIFO做缓存,同样其电路图如图11所示:根据RX_SRC_RDY_N生成FIFO的写使能信号,该发送模块设计完毕。

3 测试分析

3.1 功能测试

在基本功能测试中,主要测试光纤模块传输是否正确。由于光纤模块共有A,B,C,D四个通道,对每个通道都要进行读/写测试。将通道A作为数据发送端,通道B作为数据接收端,应用光纤将A,B两端进行联通,然后将应用程序数据写入A通道FIFO中,当FPGA接收到到数据后,将A通道数据通过光纤传输到通道B接收缓存中,然后通道B将数据发送到上位机,从而形成一个环路。比较发送和接受端的数据,可以验证数据传输的正确性。同理可以将此方法应用于四个通道中的任意两个作为发送端和接收端,从而验证并测试传输功能。

3.2 性能测试

性能主要对其传输速度和传输误码率进行测试。就传输速度而言,主要由FPGA控制,在其内部设置了两个初始值为0的计数器,在PCI-Express开始传输数据时,FPGA开始计数读/写数据包和发送数据包的个数,然后每隔一段时间将计数值写入两个计数寄存器中,并将原有值替换,为了精确速率,可以缩短计数时间,并多次测试取平均值,就可得到传输瞬时速度。经测试:PCI-Express接口的传输速度在600MB/ s,光纤传输在850 MB/s,满足设计要求。对于误码率的测试,主要使用误码分析软件对其误码性能进行测量,设计由上位机和PCI-Express接口,光纤通道组成数据传输环路,通过不同的指令和要求验证传输正确性,当数据包大小在4 Kb,8 Kb,16 Kb,32 Kb,测试数据长度分别为1 000 Kb,1 000 000 Kb,100000 000 Kb时,错误率都为0 b,误码率满足设计要求。

4 结语

该设计系统以Virtex-5为核心构建的平台,对AURORA协议下串行传输系统进行了设计与实现。通过对核心问题的解决,将计算机与外部扩展很好的结合,达到信号传输的高速、稳定的目的。实验证明,板卡设计的整体思路和核心方法的解决是完备的,并使得板卡的传输速率和稳定性的到了较大的提高。

有你想看的精彩 至芯科技FPGA就业培训班——助你步入成功之路、9月23号北京中心开课、欢迎咨询! CMOS图像传感器的FPGA逻辑设计解析 FPGA学习-数字分频器设计

扫码加微信邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:基于FPGA的高速串行传输系统设计

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1629文章

21738浏览量

603464

原文标题:基于FPGA的高速串行传输系统设计

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

深度解析高速串行信号的误码测试|线上讲堂

高速串行通信协议都有哪些

FPGA的sata接口设计时需要注意哪些问题

FPGA的高速接口应用注意事项

高速串行总线有哪些

高速串行收发器原理及芯片设计

高速串行通信协议详解

基于FPGA的内部LVDS接收器设计

基于FPGA的高速串行传输系统设计

基于FPGA的高速串行传输系统设计

评论