原理图设计是产品设计的理论基础,设计一份规范的原理图对设计PCB、跟机、做客户资料具有指导性意义,是做好一款产品的基础。原理图设计基本要求: 规范、清晰、准确、易读。

因此制定《原理图设计规范》的目的和出发点是为了培养硬件开发人员严谨、务实的工作作风和严肃、认真的工作态度,增强硬件开发人员的责任感和使命感,提高工作效率和开发成功率,保证产品质量。

原理图设计基本原则:

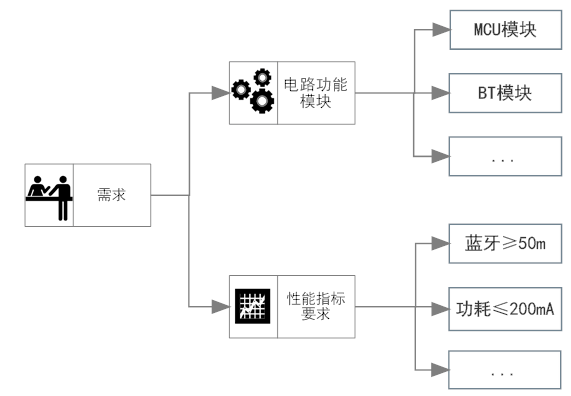

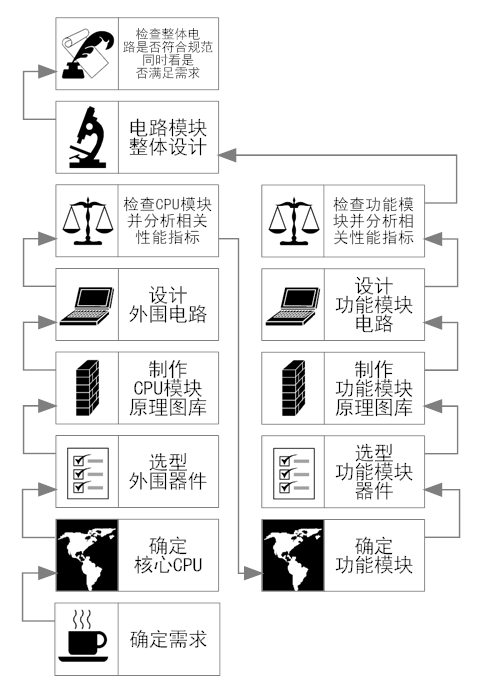

1、确定需求:

详细理解设计需求,从需求中整理出电路功能模块和性能指标要求等。

2、确定核心CPU:

根据功能和性能需求制定总体设计方案,对CPU进行选型,CPU选型有以下几点要求:

性价比高;

容易开发:硬件调试工具种类多,参考设计多,软件资源丰富,成功案例多;

可扩展性好。

3、参考成功案例:

针对已经选定的CPU芯片,选择一个与我们需求比较接近的成功参考设计,一般CPU生产商或他们的合作方都会对每款CPU芯片做若干开发板进行验证,厂家公开给用户的参考设计图虽说不是产品级的东西,也应该是经过严格验证的,否则也会影响到他们的芯片推广应用,纵然参考他们设计的外围电路有可推敲的地方,CPU本身的管脚连接使用方法也绝对是值得我们信赖的,当然如果万一出现多个参考设计某些管脚连接方式不同,可以细读CPU芯片手册和勘误表,或者找厂商确认。

另外在设计之前,最好我们能外借或者购买一块选定的参考板进行软件验证,如果没问题那么硬件参考设计也是可以信赖的,但要注意一点,现在很多CPU都有若干种启动模式,我们要选一种最适合的启动模式,或者做成兼容设计。

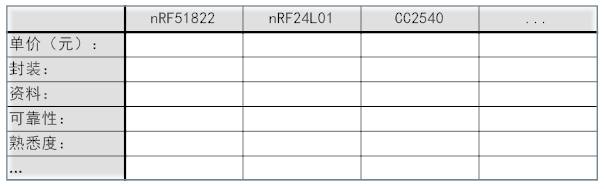

4、对外围器件选型:

根据需求对外设功能模块进行元器件选型,元器件选型应该遵守以下原则:

普遍性原则:所选的元器件要被广泛使用验证过的尽量少使用冷偏芯片,减少风险;

高性价比原则:在功能、性能、使用率都相近的情况下,尽量选择价格比较好的元器件,减少成本;

采购方便原则:尽量选择容易买到,供货周期短的元器件;

持续发展原则:尽量选择在可预见的时间内不会停产的元器件;

可替代原则:尽量选择pin to pin兼容种类比较多的元器件;

向上兼容原则:尽量选择以前老产品用过的元器件;

资源节约原则:尽量用上元器件的全部功能和管脚。

5、设计外围电路

对选定的CPU参考设计原理图外围电路进行修改,修改时对于每个功能模块都要找至少3个相同外围芯片的成功参考设计,如果找到的参考设计连接方法都是完全一样的,那么基本可以放心参照设计,但即使只有一个参考设计与其他的不一样,也不能简单地少数服从多数,而是要细读芯片数据手册,深入理解那些管脚含义,多方讨论,联系芯片厂技术支持,最终确定科学、正确的连接方式,如果仍有疑义,可以做兼容设计。这是整个原理图设计过程中最关键的部分,我们必须做到以下几点:

对于每个功能模块要尽量找到更多的成功参考设计,越难的应该越多,成功参考设计是“前人”的经验和财富,我们理当借鉴吸收,站在“前人”的肩膀上,也就提高了自己的起点;

要多向权威请教、学习,但不能迷信权威,因为人人都有认知误差,很难保证对哪怕是最了解的事物总能做出最科学的理解和判断,开发人员一定要在广泛调查、学习和讨论的基础上做出最科学正确的决定;

如果是参考已有的老产品设计,设计中要留意老产品有哪些遗留问题,这些遗留问题与硬件哪些功能模块相关,在设计这些相关模块时要更加注意推敲,不能机械照抄原来设计。

6、原理图设计时遵循的基本原则

硬件原理图设计还应该遵守一些基本原则,这些基本原则要贯彻到整个设计过程,虽然成功的参考设计中也体现了这些原则,但因为我们可能是“拼”出来的原理图,所以我们还是要随时根据这些原则来设计审查我们的原理图,这些原则包括:

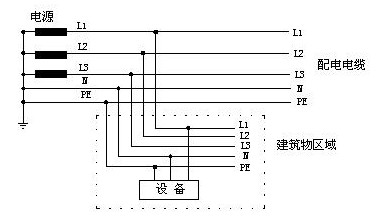

数字地和模拟地分割,单点接地,数字地可以直接接机壳地(大地),机壳必须接大地;

各功能块布局要合理, 整份原理图需布局均衡. 避免有些地方很挤,而有些地方又很松, 同PCB 设计同等道理;

可调元件(如电位器), 切换开关等对应的功能需标识清楚;

重要的控制或信号线需标明流向及用文字标明功能;

元件参数/数值务求准确标识. 特别留意功率电阻一定需标明功率值, 高耐压的滤波电容需标明耐压值;

保证系统各模块资源不能冲突,例如:同一I2C总线上的设备地址不能相同,等等;

阅读系统中所有芯片的手册(一般是设计参考手册),看它们的未用输入管脚是否需要做外部处理,如果需要一定要做相应处理,否则可能引起芯片内部振荡,导致芯片不能正常工作;

在不增加硬件设计难度的情况下尽量保证软件开发方便,或者以小的硬件设计难度来换取更多方便、可靠、高效的软件设计,这点需要硬件设计人员懂得底层软件开发调试,要求较高;

功耗问题;

产品散热问题,可以在功耗和发热较大的芯片增加散热片或风扇,产品机箱也要考虑这个问题,不能把机箱做成保温盒,电路板对“温室”是感冒的;还要考虑产品的安放位置,最好是放在空间比较大,空气流动畅通的位置,有利于热量散发出去。

7、原理图审核

硬件原理图设计完成之后,设计人员应该按照以上步骤和要求首先进行自审,自审后要达到有95%以上把握和信心,然后再提交他人审核,其他审核人员同样按照以上要求对原理图进行严格审查,如发现问题要及时进行讨论分析,分析解决过程同样遵循以上原则、步骤。

8、原理图设计基本要求

只要开发和审核人员都能够严格按以上要求进行电路设计和审查,我们就有理由相信,所有硬件开发人员设计出的电路板一版成功率都会很高的,所以提出以下几点:

设计人员自身应该保证原理图的正确性和可靠性,要做到设计即是审核,严格自审,不要把希望寄托在审核人员身上,设计出现的任何问题应由设计人员自己承担,其他审核人员不负连带责任;

其他审核人员虽然不承担连带责任,也应该按照以上要求进行严格审查,一旦设计出现问题,同样反映了审核人员的水平、作风和态度;

普通原理图设计,包括老产品升级修改,原则上要求原理图一版成功,最多两版封板,超过两版将进行绩效处罚;

对于功能复杂,疑点较多的全新设计,原则上要求原理图两版内成功,最多三版封板,超过三版要进行绩效处罚;

原理图封板标准为:电路板没有任何原理性飞线和其他处理点;

每张原理图都需有公司的标准图框,并标明对应图纸的功能,文件名,制图人名/确认人名, 日期, 版本号;

对于重点设计的相关模拟电路产品,没有主用芯片、外围芯片以及芯片与芯片之间的连接方面的问题。所以,元器件的选项尤为重要,对于硬件设计的一些基本原则一定要注意。

9、原理图设计规范Checklist

| 1 | 检视规则 | 原理图需要进行检视,提交集体检视是需要完成自检,确保没有低级问题。 |

| 2 | 检视规则 | 原理图要和公司团队和可以邀请的专家一起进行检视。 |

| 3 | 检视规则 | 第一次原理图发出进行集体检视后所有的修改点都需要进行记录。 |

| 4 | 检视规则 | 正式版本的原理图在投板前需要经过经理的审判。 |

| 5 | 差分网络 | 原理图中差分线的网络,芯片管脚处的P和N与网络命令的P和N应该一一对应。 |

| 6 | 单网络 | 原理图中所有单网络需要做一一确认。 |

| 7 | 空网络 | 原理图中所有空网络需要做一一确认。 |

| 8 | 网格 | 1、原理图绘制中要确认网格设置是否一致。2、原理图中没有网格最小值设置不一致造成网络未连接的情况。 |

| 9 | 网络属性 | 确认网络是全局属性还是本地属性 |

| 10 | 封装库 | 1、原理图中器件的封装与手册一致。2、原理图器件是否是标准库的symbol。 |

| 11 | 绘制要求 | 原理图中器件的封装与手册一致。 |

| 12 | 指示灯 | 设计默认由电源点亮的指示灯和由MCU点灭的指示灯,便于故障时直观判断电源问题还是MCU问题 |

| 13 | 网口连接器 | 确认网口连接器的开口方向、是否带指示灯以及是否带PoE |

| 14 | 网口变压器 | 确认变压器选型是否满足需求,比如带PoE |

| 15 | 按键 | 确认按键型号是直按键还是侧按键 |

| 16 | 电阻上下拉 | 同一网络避免重复上拉或者下拉 |

| 17 | OD门 | 芯片的OD门或者OC门的输出管脚需要上拉 |

| 18 | 匹配 | 高速信号的始端和末端需要预留串阻 |

| 19 | 三极管 | 三极管电路需要考虑通流能力 |

| 20 | 可测试性 | 在单板的关键电路和芯片附近增加地孔,便于测试 |

| 21 | 连接器防呆 | 连接器选型时需要选择有防呆设计的型号 |

| 22 | 仿真 | 低速时钟信号,一驱动总线接口下挂器件的驱动能力、匹配方式、接口时序必须经过仿真确认,例如MDC/MDIO、IIC、PCI、Local bus |

| 23 | 仿真 | 电路中使用电感、电容使用合适Q值,可以通过仿真。 |

| 24 | 时序 | 确认上电时序是否满足芯片手册和推荐电路要求。 |

| 25 | 时序 | 确认下电时序是否满足芯片手册和推荐电路要求。 |

| 26 | 时序 | 确认复位时序是否满足芯片手册和推荐电路要求。 |

| 27 | 复位开关 | 单板按键开关设计,要防止长按按键,单板挂死问题,建议按键开关设计只产生一段短脉宽低电平。 |

| 28 | 复位设计 | 复位信号设计(1)依据芯片要求进行上下拉(2)确认芯片复位的默认状态(3)Peset信号并联几十PF的电容滤波,优化信号质量。(4)复位信号保证型号完整性。 |

| 29 | 复位 | 所有接口和光模块默认处于复位状态。 |

| 30 | 电平匹配 | 不同电平标准互连,关注电压、输入输出门限、匹配方式。 |

| 31 | 功耗 | 详细审查各个芯片的功耗设计,计算出单板各个电压的最大功耗,选择有一定余量的电源。 |

| 32 | 缓启 | 热插拔电路要进行缓启动设计 |

| 33 | 磁珠 | 小电压大电流(安培级)值电源输出端口的磁珠,需要考虑磁珠压降 |

| 34 | 连接器 | 板间电源连接器通流能力及压降留有预量 |

| 35 | 标识 | 扣板与母板插座网络标识是否一致,前后插卡连机器管脚信号要一一对应。 |

| 36 | 电平匹配 | 一驱多信号要根据仿真结果进行阻抗匹配,确定是否加始端或末端匹配电阻 |

| 37 | 匹配电平 | 原理图设计要关注厂家器件资料的说明,输入输出都会有明确的匹配要求。 |

| 38 | 二级管 | 使用在控制、检测、电源合入等电路中的二极管,必须考虑二极管反向漏电流是否满足设计要求。 |

| 39 | MOS | CMOS器件未使用的输入/输出管脚需按照器件手册要求处理,手册未要求的必须与厂家确认处理方式。 |

| 40 | 温感 | 关键器件尤其的温度要进行监控 |

| 41 | 244/245 | 有上、下拉需要的信号在经过没有输出保持功能的总线驱动器后,需要在总线驱动器的输入、输出端加上下拉。 |

| 42 | 244/245 | 244/245如果不带保持功能,则必须将不用的输入管脚上下拉。 |

| 43 | 时钟 | 晶振管脚直接输出的信号禁止直接1驱多,多个负载会影响信号质量,建议采用1对1的方式。 |

| 44 | 时钟 | 晶体的xt-out和时钟驱动器相连需要0402串阻,阻值选择不能影响单板起震。 |

| 45 | 时钟 | 锁相环电路及参数的选取必须经过专项计算。 |

| 46 | 时钟 | 时钟环路滤波陶瓷电容优选NPO介质电容。 |

| 47 | 时钟 | 确认信号摆幅,jitter等是否超出器件要求。 |

| 48 | 时钟 | 确认时钟器件在中心频率、工作电压、输出电平、占空比、相位等各项指标上能完全满足要求。 |

| 49 | DDR | DDR等存储器接口都要有时钟频率降额设计。 |

| 50 | DDR | 对于可靠性要求较高的单板建议在RAM开发中满足ECC设计规则要求。 |

| 51 | DDR | DDR的VTT电源滤波要做到Vtt电阻和绿宝电容的搭配。 |

| 52 | PHY | MDC/MDIO采用一驱多的匹配方式,主器件经过串阻-》上拉电阻-》串阻到从器件,串阻要放置在两端。 |

| 53 | PHY | 1对多的控制,PHY需要预留地址信号,用于控制。 |

| 54 | PHY | CAM等芯片功耗根据访问条件和温度,功耗变化较大,设计时要要仔细查询器件手册,明确功耗和厂家芯片的关系。 |

| 55 | PHY | 设备有光模块接口是,光模块内部串接10nf电容,链路不需要进行重复设计。 |

| 56 | 散热器 | 选择散热器时,要考虑到散热器的重量和与设备的结合方式。 |

| 57 | I2C | 设备通过I2C进行互联时,可以使用芯片内I2C模块,也可以通过I2C模块。 |

| 58 | 电容 | 单板中射频相关部分设计的时候,需要旁路,滤波电容,针对不同的干扰频率要选择不同容值的滤波电容。 |

| 59 | 电容 | 电容并联设计时,要计算或通过仿真分析谐振点,避免可能会出现的谐振问题。 |

| 60 | 电容 | 滤波电容的设计要关注对控制管脚的影响。 |

| 61 | 电容 | 没有使用的管脚如何使用需要参考芯片手册和demo板的设计去关注这些管脚的设计是否合理。 |

| 62 | 特征阻抗 | 对PCB布线的特征阻抗有特殊要求时,需要在原理图或者给互连工程师的需求文档中进行特殊说明。 |

| 63 | 复位设计 | 关键功能器件应该预留独立的复位设计。 |

| 64 | 复位设计 | 很多Flash都有rst的管脚,为满足启动阶段的软件功能实现要求,在 |

| 65 | 射频滤波 | 视频放大器的电源设计时要添加合适的滤波电容,防止电源噪声对射频信号质量造成本良影响。 |

| 66 | 射频滤波 | 电源、功率电路设计是应用电需要考虑电阻的功率特性的选择。 |

| 67 | 可测试性 | 部分功能模块要保持可以长工状态,利于进行硬件测试。 |

| 68 | 射频电路 | 直流偏置电路是否需要使能控制,控制电压精度是否满足放大器的要求。 |

| 69 | 射频电路 | 保证前级可能输出的最大RF峰值功率小于后级级联器件的最大极限输入功率3dB左右,需要关注信号峰值和过冲对器件过功率的影响。 |

| 70 | 射频电路 | 射频器件功率放大器的中心散热焊盘在原理图上必须接地。 |

| 71 | 射频电路 | 具备on/off的射频器件功能,在off状态下隔离度有问题,隔离度影响收发的干扰情况,干扰信号需要保持在合理电平内,否则影响套片正常工作。 |

| 72 | 射频电路 | PA的RF发送端链路PA外围电路正价负反馈设计防止烧PA。 |

| 73 | 射频电路 | 射频接收电路,需要在接收机和套片之间预留PI型位置,调试接收灵敏度。 |

| 74 | 电源 | 确保所有的电源转换模块OCP/OVP点(过流保护点和过压保护点)设定正确 |

| 75 | 电源 | 电源的带负载能力是否足够,相数是否足够,能提供足够大的电流、功率給CPU,Chipset等(1相按最大20A计算,保守15A) |

| 76 | 电源 | PWM单相频率范围是200K-600K;集成MOS的可以达到1MHz |

| 77 | 电源 | 输入电容的Ripple current(参考2700mA);电容Ripple Current小会导致电容发热,影响寿命 |

| 78 | 电源 | 输出电容的ESR是否足够小 |

| 79 | 电源 | 电容的耐压是否满足,同时满足降额 |

| 80 | 电源 | H-MOS导通时间短;L-MOS导通时间长 |

| 81 | 电源 | H-Side MOSFET要选择导通速度快的 |

| 82 | 电源 | L-Side MOSFET要选择Rds(on)低的 |

| 83 | 电源 | 线性电源的损耗P=Δvi,一般,1颗LDO可承受的功率损耗PmaxJunction=器件Temp,保证器件temp与环境Temp之和小于MOS的最大工作温度的80%。 |

| 84 | 电源 | 单板上同一电源和地名称要统一 |

| 85 | 电源 | 单相PWM driver 的BOOT Pin与phase端接0.1uF电容.核对BOOT电容,是否耐压值为50V。H-MOS导通之后,BOOT Pin电压达24V,Phase端12V。 |

| 86 | 电源 | H-side Gate上预留0ohm电阻,防止High side MOS因Vgs过大被击穿 |

| 87 | 电源 | Feedback电路设置是否准确;在电路上注释反馈电压计算公式。 |

| 88 | 电源 | GND和AGND电路要分开,但最后要通过一点进行连接。如果是chipset的 AGND电流很大,可直接与GND相连,不需要连接0OHM,否则通流不够。 |

| 89 | 电源 | PWROK的上拉要用对应的电源去上拉。 |

| 90 | 电源 | 有些模块线路copy过来后,需要注意AGND属性要更改,最好能赋予net名字,比如经常会遇到两个P1V1的AGND起的名字一样。 |

| 91 | 电源 | 确认电感封装,核对饱和电流是否满足电路需求。电感封装越大,过电流能力越强,电感的饱和电流应该大于电路的OCP电流。 |

| 92 | 电源 | 确认补偿线路,保证足够的穿越频率,以及相位裕度。 |

| 93 | 电源 | 核对LDO的最大压差是否满足器件的要求(输入的电压范围和输出的电压范围) |

| 94 | FPGA | 确认输入输出的逻辑电平是否正确;电平类型:GTL,OD,LVCMOS33、LVCOM25、LVDS等。确认芯片和CPLD/FPGA之间的逻辑电平是否匹配,避免两边电平不一致。 |

| 95 | FPGA | CPLD的GPIO信号作为输出管脚控制时序时,需要将此Pin通过4.7K至10K电阻做下拉处理 |

| 96 | FPGA | CPLD的JTAG接口需要连至Header上,注意Header的Pin脚定义符合烧录器要求,JTAG信号预留ESD保护电路。 |

| 97 | FPGA | 空余的没有使用的GPIO Pin接到LED上,一般3-4个LED即可。 |

| 98 | FPGA | 对于同一功能的GPIO尽量只选用同一个Pin(Reset信号除外) |

| 99 | FPGA | 不同bank的电平跟这个bank的VCCIO电平有关 |

| 100 | FPGA | FPGA外接ROM时,需在原理图里面标注1,2,3顺序(顺序不对会出现烧录不了的问题)。确保信号连接之间接口电平是否正确,是否需要采用levelshift设计 |

| 101 | FPGA | CPLD core电和IO电时序,一般要求core电要早于IO电,否则,输出信号需要加下拉电阻。(一般情况下core电都早于IO电压,Core起来之后IO状态就可以固定了。具体要求参考厂家器件资料) |

| 102 | FPGA | FPGA的MGT Bank如果不用时,RX信号需要接地处理。 |

| 103 | FPGA | MGT Bank指可配置为高速接口的bank,例如xilinx的GTP,GTX接口bank,不用时要对RX信号处理 |

| 104 | FPGA | 在原理设计期间必须向CPLD编程人员提供规范的CPLD需求文件 |

| 105 | FPGA | 在CPLD需求文件必须指定每个管脚的输入和输出状态。 |

| 106 | FPGA | 对于CPLD尽可能的少用时序逻辑,多使用组合逻辑,尽可能用简单逻辑代替复杂逻辑 |

| 107 | FPGA | 设计人员提供的逻辑需求要避免竞争和冒险,即用CPLD输出的信号做其他逻辑的输入判定 |

| 108 | FPGA | 有支持I2C的设计需求,要事先规划好系统I2C拓扑,在芯片选型时要考虑预留逻辑空间。(BMC如果I2C资源够用,CPLD单独占用一组I2C总线) |

| 109 | 连接器 | 高速连接器的带宽要按照1.5-2倍选择 |

| 110 | 连接器 | 确认connector在PCB上的Pin定义方式 |

| 111 | 连接器 | 两块对插板connector的对应Pin脚信号定义是否一致,对于多块单板互连,需要确认对应连接器的物理位置是否正确。 |

| 112 | 连接器 | 根据板厚来确定是否可以选用焊接件和压接器件 |

| 113 | 连接器 | 一般连接器应注意母端有长短针,因此需母端定义电源和GND |

| 114 | 连接器 | 高速信号连接器,高速信号周围的GND Pin一定接地 |

| 115 | 连接器 | 高速信号连接器,定义信号时,注意TX,RX在连接器上的分布,避免TX/RX混在一起(避免cross talk) |

| 116 | 连接器 | 作为一个由两个连接器拼成的接口,需选择同一厂商,同一类型连接器 |

| 117 | 连接器 | SMD连接器选择时,其上面要有一个平面,便于工程的高速机吸嘴吸取不易脱落。Packing优先选择盘装,不用管状的。 |

| 118 | 连接器 | 尽量能够统一为焊接器件或压接器件 |

| 119 | 连接器 | 注意管脚长度的选择 |

| 120 | 连接器 | 在进入layout布局之前务必提供各连接器位置顺序图 |

| 121 | 连接器 | 连接器选型时尽可能选择通用的物料(两家以上Source的),保证一定的可替代性 |

| 122 | 连接器 | 连接器选型时需要考虑PCB的厚径比(不能超过10:1) |

| 123 | 连接器 | 网口连接器选择时要关注连接器颜色,颜色不同会影响产品的外观感知。 |

| 124 | 连接器 | 对于不同速率、种类的接口,如10GE、GE口、FE口、控制口、调试口的鞥可以通过面膜不同颜色进行区分。 |

| 125 | 连接器 | 连接器选择时需要关注是否有定位管脚,没有定位管脚生产加工时可能会出现偏位。 |

| 126 | 连接器 | 连接器选择时需要关注引脚长度和PCB板厚的关系,引脚过长在单板生产加工完成时需要减脚处理,引脚过短(如定位管脚)在单板加工时会出现上翘等现象。 |

| 127 | 时钟 | clock signal(除differential Signal外),要预留可调节EMI 的电容位置,一般为10pF. |

| 128 | 时钟 | PCI-E2.0 slot的clock signal 建议与控制芯片同源。 |

| 129 | 时钟 | 当Clockgen或Clock Buffer使用SYS供电时,应注意网卡、CPLD等芯片的时钟信号是否需要单独的时钟源 |

| 130 | 时钟 | 所有Clockgen和Clock Buffer的SMbus接口上拉的电压应与IC的供电一致 |

| 131 | 时钟 | 当晶振或clock buffer输出的电平和IC需要的电平不一致时需要加AC耦合和阻抗匹配电路,同时要注意SWING和CROSSPOINT设置是否正确。 |

| 132 | 时钟 | 注意Ossilater的clock信号输出电平,如果是LVPECL,外部需要加对地150ohm电阻。对于发射级耦合逻辑电路,需要在外围提供地回流路径。 |

| 133 | 时钟 | CPU的晶振应尽量排布在晶振输入引脚附近。无源晶振要加几十皮法的电容;有源晶振可直接将信号引至CPU的晶振输入脚。 |

| No. | 类别 | 描述 |

|---|

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50832浏览量

423811 -

原理图

+关注

关注

1298文章

6344浏览量

234136 -

pcb

+关注

关注

4319文章

23102浏览量

398023 -

模拟电路

+关注

关注

125文章

1557浏览量

102750

原文标题:原理图设计规范133条checklist

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

原理图设计基本原则

原理图设计基本原则

评论