1.SI问题根源

信号的上升时间越短,信号包含的高频成分就越多,高频分量和通道之间的相互作用就越可能导致信号畸变,从而产生SI问题。

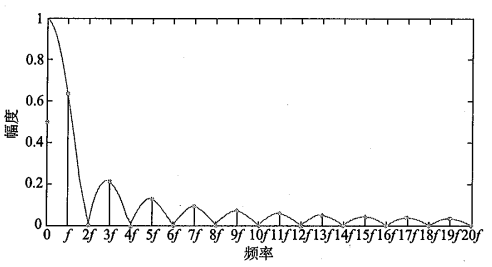

占空比位50%的理想方波,其频谱只包含奇次谐波,所有偶次谐波的幅值均为0,并且随着频率增大趋于无穷大时,频谱幅值会以-20dB/decade的速度衰减,幅值为1的方波,其频谱示意如图1所示。

图1 幅值为1的理想方波频谱

实际电路中传输的信号不可能是理想方波,更像是梯形波。梯形波频谱随着频率分量的增大,频谱幅值衰减速度更快。因此,如果某个频率分量的幅值小到可以对其影响忽略不计,那么就定义为该信号带宽。信号带宽越大,包含的频率分量越多,合成后的信号波形上升时间就越小。根据带宽定义的不同,带宽一般有两个表达式, ,Tr为信号的10%~90%上升时间。

,Tr为信号的10%~90%上升时间。

2.传输线理论

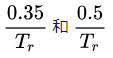

低速电路设计时是将互联结构当成集总元件来对待,不考虑信号在驱动端、互联通道和接收端的传输过程,认为信号一直是理想的。而高速电路信号由于包含很多高频分量,互联结构中的各种寄生参数对信号的影响也越来越明显。因此,必须将信号从驱动端传输到接收端的整个过程看做是动态过程进行分析,即把互联结构当做传输线进行研究,信号以电磁波的形式进行传播。

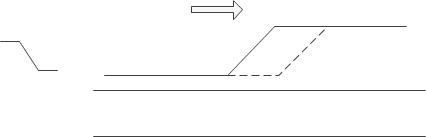

传输线包含一个信号路径和一个参考路径。需要注意的是,传输线中的参考路径并不一定是接地GND的,其与电气极性没有任何关系。当驱动器输出变化的电压或者电流信号加载到传输线时,变化的电压或电流信号形成变化的电场和磁场(电磁波)向前传播,而在传输过程中,变化的电场和磁场又会产生变化的电压或电流,传输速度即为电磁波在传输线介质中的光速,示意如图2所示。

图2 传输线

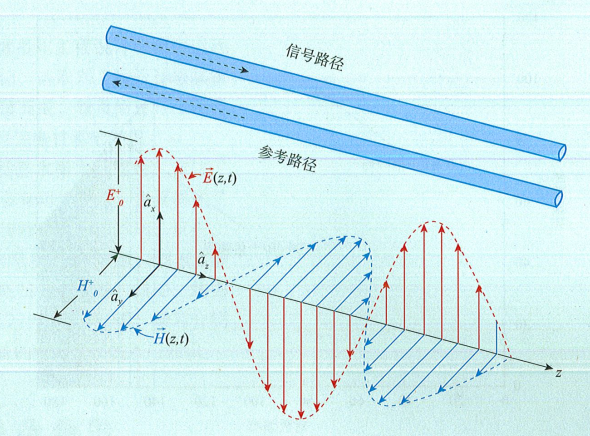

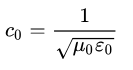

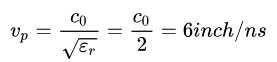

信号在传输线上的传输是个动态过程,假设驱动器发出一个上升沿信号,该信号电压是随着时间逐渐上升的一个过程,因此,信号在向前传输过程中,传输线的电压类似浪头一样向前推进,如图3所示,速度为介质中的光速。如果驱动器发出一个下降沿信号,则如图4所示。

图3 上升沿传输

图4 下降沿传输

由于传输线上的信号传输是个动态过程,每个时刻信号浪头电压所处位置不同,并向前推进,因此传输线上的任何局部变化都会影响信号波形。

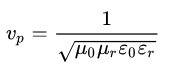

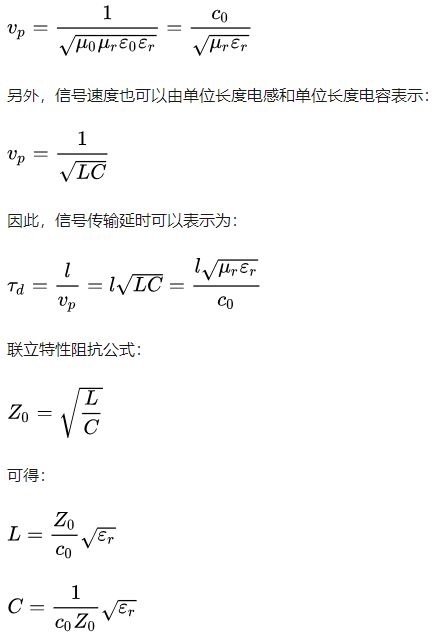

信号在介质中的传播速度为:

真空中的光速为:

常用PCB板材FR4的介电常数为4左右,相对磁导率为1,因此PCB上的信号传播速度为:

2.1 分布电容

如前所述,由于信号在传输线上的传输是动态过程,只有浪头电压所占据的传输线长度上的电压是变化的,其他长度空间上的传输线电压是不变的。因此传输线上的电容经常用单位长度电容来衡量,对于FR4板材,6mil线宽,50欧姆阻抗的表层走线单位长度电容为3pF/inch,内层走线为3.5pF/inch。

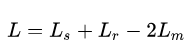

2.2 回路电感

同分布电容类似,分布电感也采用单位长度电感来衡量,只是由于传输线需要把信号路径和返回路径作为一个整体来研究,因此,使用的是回路电感,其由信号路径和返回路径的自感之和,减去两者的互感,

由此可见,互感Lm越大,回路电感L越小;而组成传输线的两个导体之间距离越小,互感Lm越大,距离越大,互感Lm越小。因此,若要减小回路电感,需要让信号路径和返回路径越近越好,相应地回路面积也会越小。看到这个,是不是有点类似电源PCB设计时的注意事项啊,很多知识点是类似的。

50欧姆阻抗的表层走线单位长度电感为7.5nH/inch,内层走线为9nH/inch。

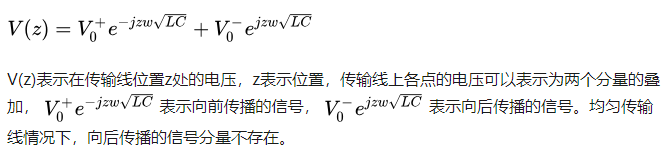

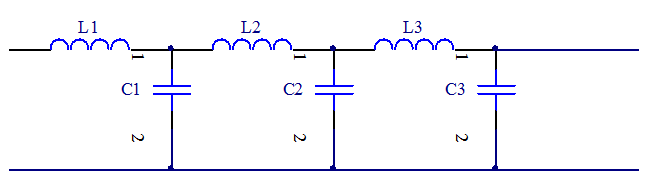

2.3 理想传输线

理想传输线表示信号沿着传输线传播时没有损耗衰减,其等效模型如图5所示,任意长度的一段传输线可以用一个电感和一个电容来表示,通过求解麦克斯韦方程组可以得到信号电压的电报方程:

图5

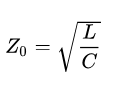

2.3 特性阻抗

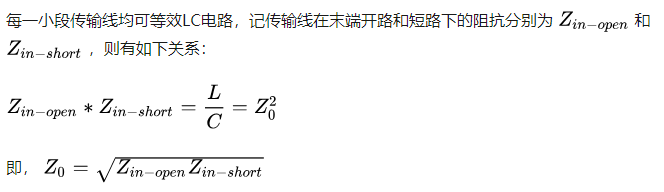

传输线上的信号在传播过程中,每到一个位置,都会感受到一个瞬态阻抗。如果传输线是均匀无损的,则信号在传播过程中无论什么位置,感受到的阻抗都是相同的,称为特性阻抗,记为Z0:

根据特性阻抗表达式可知,任何影响传输线单位长度电感和单位长度电容的因素都会影响特性阻抗,影响因素主要有4个:线宽、介质厚度、介电常数和走线的铜箔厚度。

线宽:线宽越大,电流越分散,电感越小;线宽越大,电容 越大;因此,线宽越大,特性阻抗越小。

越大;因此,线宽越大,特性阻抗越小。

介质厚度:介质厚度越厚,导体间距越大,回路互感越小,回路电感越大;介质厚度越厚,电容越小;因此,介质厚度越厚,特性阻抗越大。

介电常数:单位长度电感和介电常数无关,但是介电常数越大,电容越大,因此,特性阻抗越小。

走线铜箔厚度:铜厚增大,电感减小,电容增大,特性阻抗减小。

这些因素在设计多层的高速电路PCB时就能使用到,涉及如何分配层叠以及阻抗控制。

2.4 参考平面

参考平面是指以平面形式出现的参考路径,参考路径和信号路径一起构成传输线。参考平面一定是返回路径,但是返回路径可能不仅包含参考平面,还有其他和信号路径临近的导体。参考平面的主要作用就是和信号路径构成电磁波传播的传输线结构。

2.6 返回电流分布

对于微带线来说,只有一个参考平面,返回电流集中在走线正下方的参考平面上,越往走线两侧外边,电流越小。

对于带状线来说,有两个参考平面,返回电流集中在走线正上方和正下方的参考平面上,每个参考平面上的返回电流大小和参考平面与走线之间的距离成反比。

当然,如前所述,返回电流不仅仅存在于参考平面,与走线同层临近的走线等导体上也有返回电流,但是电流较小,距离走线越远,电流越小。

2.7 传输线延时

由前述可知,信号速度可以表示为:

由此可见,如果介电常数相同,则所有特性阻抗相同的走线的单位长度电感相同,单位长度电容也相同。

由前述可知,理想传输线是多级LC电路级联在一起,对于很长的传输线,怎样分段才合理呢?一般原则是:分段长度要小于信号中最高感兴趣频率对应的波长。

2.8 传输线耦合模态

当存在多条信号线时,互相之间存在互容和互感,一条信号线上电压和电流的变化会引起其他信号线的变化,这就是耦合传输线。重点关注两条信号线的情况,有3种工作状态:

(1)一条信号线处于静止状态,无信号传输;

另一条线的分布电容增大,分布电感不变;

(2)一条信号线上信号正跳变,另一条信号线上信号同时负跳变;

其中一条线的分布电感减小,分布电容增加;另一条亦如此,称为奇模状态;

(3)两条信号线上同时同向跳变;

其中一条线的分布电感增大,分布电容则不变;另一条亦如此,称为偶模状态。

因此可知,三种模态下的阻抗大小为奇模<静止<偶模。

随着线间距的增大,奇模阻抗和偶模阻抗越来越接近于单根线的阻抗,而静止阻抗变化幅度很小。而且内层走线随着线间距增大,阻抗变化影响衰减更快,因此,内层走线更容易保持传输线阻抗的稳定性。

不同的耦合模态,其串扰影响也不同。

2.9 有损传输线

传输线损耗主要有以下几方面:

(1)阻性损耗:来源于导线电阻,而在交流情况下,电阻会随频率变化,因此阻性损耗也会随频率变化。另一方面,由于趋肤效应,临近效应和导体表面的粗糙度,这会进一步加剧阻性损耗。宽走线可以减小该损耗。

(2)介质损耗:源于介质的极化,且和PCB板材有关。阻性损耗和介质损耗是最主要的损耗,但是可以通过均衡技术进行补偿。由于考虑介质损耗的影响,通常使用复介电常数,其包含了影响电容参数的相对介电常数和损耗角 ,损耗角正切值越大,介质损耗越大。

(3)耦合到临近线:通常指串扰。

(4)阻抗不连续;

(5)对外辐射:该损耗较小。

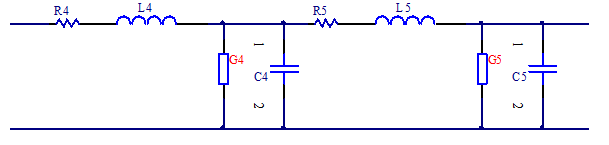

有损传输线模型如图6所示,

图6

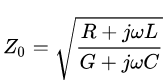

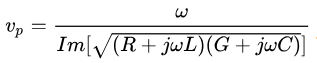

特性阻抗为 ,可见低频时特性阻抗较大,随频率升高特性阻抗减小并很快趋于稳定。

,可见低频时特性阻抗较大,随频率升高特性阻抗减小并很快趋于稳定。

传播速度为 。信号传播的速度与信号的频率有关,不同频率的信号传播速度不同,随频率升高,传播速度增大并很快趋于稳定。因此,不同频率信号传播速度不同导致在经过一段传输线后,不同频率的信号分量在时间上互相错开,类似色散。

。信号传播的速度与信号的频率有关,不同频率的信号传播速度不同,随频率升高,传播速度增大并很快趋于稳定。因此,不同频率信号传播速度不同导致在经过一段传输线后,不同频率的信号分量在时间上互相错开,类似色散。

-

驱动器

+关注

关注

52文章

8228浏览量

146266 -

PCB板

+关注

关注

27文章

1447浏览量

51614 -

电阻器

+关注

关注

21文章

3781浏览量

62115 -

信号完整性

+关注

关注

68文章

1405浏览量

95459 -

GND

+关注

关注

2文章

539浏览量

38697

发布评论请先 登录

相关推荐

信号完整性SI读书笔记

信号完整性SI读书笔记

评论