- 布线分析

开关转换发生在导通(开关闭合)到关断(开关断开)瞬间,其持续时间一般小于100ns,但绝大多数问题都发生在该时段。噪声与变换器的基本开关频率没有很大关系,多数噪声及其他相关问题都发生在转换瞬间。而且开关转换时间越短,产生的问题越多。

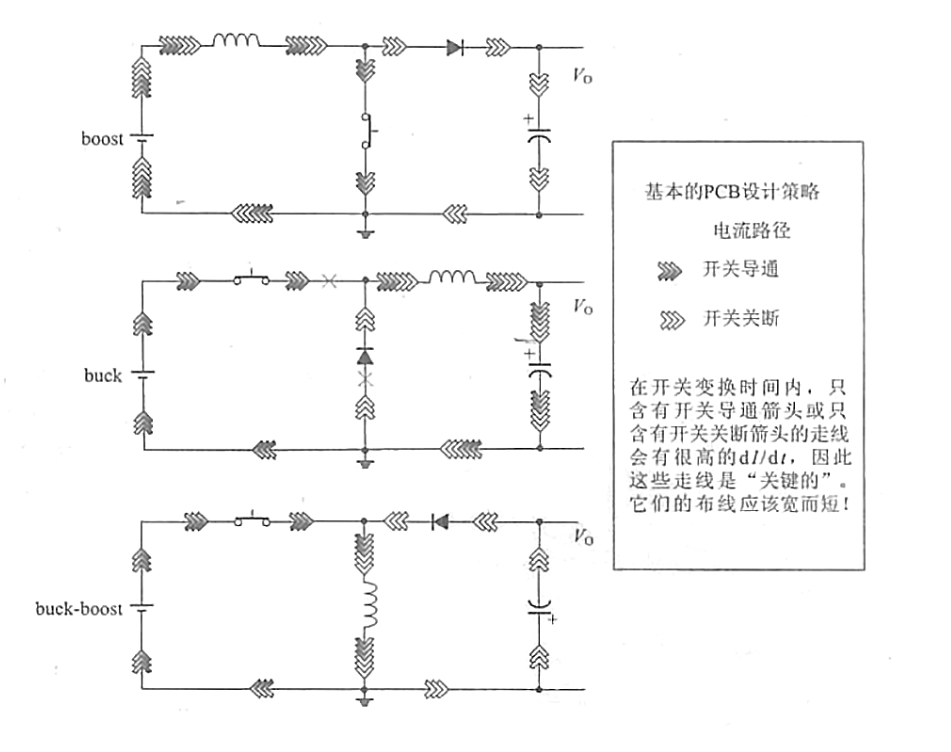

作为设计师首先应了解变换器主电路电流的流向,从而识别出 PCB 中有麻烦的或关键的走线,必须特别注意这些走线的布线。该走线的判定随拓扑结构的不同也不同。因此,不能用设计buck电路PCB的方法来设计 buck-boost 电路PCB。其规律有很大差别。

- 布线要点

1、在开关转换期间某些走线的电流会瞬间停止,而另外一些走线电流同时瞬间导通(均在开关转换时间100ns之内发生)。这些走线被认为是开关调整器PCB布线的“关键走线”。每个开关转换瞬间,这些走线中都产生很高的dl/dt。如图1所示,整个线路混杂着不少的电压尖峰,这是由于寄生电感的存在导致的。根据经验,每英寸走线的寄生电感约为 20nH。

图1

2、噪声尖峰一旦产生,不仅会传递到输入/输出端(影响电源性能),而且会渗透到IC控制单元,使控制功能失稳失常,甚至使控制的限流功能失效,导致开关元件损坏。

3、MOSFET比BJT(俗称三极管)转换速度更高。MOSFET的开关转换时间一般为10ns ~ 50ns,而BJT一般为100ns~150ns。由于它们在其PCB关键走线中产生更高的dI/dt,采用MOSFET开关的变换器将产生更恶劣的“尖峰”。

注意:对1英寸的铜走线开关,在30ns 的开关转换时间流过1A的瞬态电流,将产生0.7V的尖峰电压。若是3A的瞬态电流流过2英寸铜走线,将产生近4V的尖峰电压。

噪声尖峰几乎是观察不到的。首先,各种寄生参数一定程度上帮助吸收尖峰噪声。其次,用示波器探头观察时,探头自身 10pF~20pF的电容也能吸收该类尖峰,从而看不到任何显著信息。另外,探头感应了太多空气传播的开关噪声,使观察者难以确定所看到的到底是什么。

4、所有集成IC的开关均与其控制部分封装在一起。这样虽然应用方便且价格便宜,但是通常这样的IC对走线寄生电感所产生的噪声更敏感。这是因为其功率级开关节点(即连接二极管、开关管和电感的节点)仅是该IC本身的输出引脚,该引脚将开关节点产生的高频噪声直接传递到控制部分,导致控制失常。

5、注意在调试时,如图1所示,不应在关键走线的某处使用一段软线接入电流探头,因为该电流环路将形成一个附加电感,使噪声尖峰急剧增高。因此,单独测出开关电流或者二极管电流几乎是不可能。这种情况下,只能测量出电感电流波形。

6、注意buck和buck-boost电路输入电容也处于关键路径中。这意味着在这些拓扑中,功率级需要有良好的输入去耦装置。因此,除了功率级所需的大容量电容(通常是大容量钽电容或铝电解电容)外,还应在开关的“静默”端(电源侧)与最靠近开关的地端之间接入一小容量陶瓷电容(约0.1μF~1μF)。

7、图1未画出控制部分。控制电路本身需要良好的解耦装置。为此,需在紧临IC的地方接人一个小容量陶瓷电容。

8、有时,控制IC可能需要更有效的解耦装置,用一连接输人电源高端的小电阻(通常10Ω~22Ω)与陶瓷电容串联接于IC的输人与地脚之间,从而构成了IC电源的小型“RC滤波器”。

9、对所有拓扑,电感均不处于关键路径,因此不必过多担心它的布线,但要考虑电感产生的电磁场,它会影响附近的电路及敏感走线。因此一般情况下,若成本允许最好使用“屏蔽电感”以解决上述问题。若条件不允许,应将其置于远离 IC处,特别要远离反馈走线。

10、从图1可见,对boost和buck-boost 电路,输出电容处于关键路径。因此该电容和二极管应尽量靠近控制IC。在该电容两端并联一陶瓷电容是有利的,但要求它不会引起环路不稳定。

对于buck电路,应注意虽然要求输出二极管尽量靠近IC/开关,但对输出电容没有严格要求(由于电感的存在使得该路径电流平滑)。若用一陶瓷电容与输出电容并联则只是为进一步降低输出高频噪声和输出纹波。但该做法不可靠,特别对电压控制模式,当输出电容等效串联电阻(ESR)值变得太小(小于100mΩ)时,可能造成环路严重不稳定。

11、对于所有拓扑,二极管均处于关键路径。二极管连接开关节点,并通过节点直接连接到开关IC内部。对于开关IC,当buck变换器布线造成二极管离IC距离太远时,可通过在开关节点与地之间(跨过二极管,靠近IC)并联一小型 RC缓冲器来进行后级调整。该RC缓冲电路由一个10~100Ω电阻(最好为低感型)与一个约470pF ~ 2.2nF的电容(最好为陶瓷电容)串联组成。注意电阻功耗为CVin^2f。这样不仅电阻瓦数应选合适,电容容值也不能随意增加,以避免效率损失太多。

12、长度为l、直径为d的导线电感值可由以下近似公式计算

l和d单位均为cm。

PCB走线电感计算公式与导线电感公式区别不大,可用下式计算

其中ω为走线宽度。注意PCB走线电感基本与敷铜厚度无关。从以上对数关系可以看出,若 PCB走线长度减少一半,则其电感也减少一半。但走线宽度必须增加10倍才使其电感减少一半。即仅增加走线宽度用处不大,要减少电感应使走线尽量短。

13、“过孔”电感由以下公式计算

式中h为过孔深度,单位为mm(其等于板厚,一般为1.4mm~16mm),d为过孔直径,单位为mm。这样,16mm厚的板,直径为0.4mm的过孔电感为1.2nH。虽然不大,但实际证明它也影响开关IC工作,特别是在使用MOSFET时。因此必须使用一输入陶瓷电容为IC解耦,一定要注意该电容应尽可能靠近IC引脚与PCB连接处,并且在该电容与IC引脚焊点之间不能有过孔连接。

14、增加某些走线宽度对电路工作可能是不利的。例如,对正输入——正输出buck变换器,从开关节点到二极管的走线是“热”(电压变动的)的。任何带有变动电压的导体,不管它流过电流的大小,只要其尺寸足够大就会形成E型天线。因此应该减少开关节点处的走线面积。唯一允许大面积敷铜的电压节点是接地点或外壳接地点。其他走线(包括输人电源母线)都可能因寄生高频噪声而产生严重辐射效应。

15、1oz板是指板敷铜厚度为 1.4mil(或35μm)。类似地2oz是指前面的两倍厚度。对1oz板,在中等温升(低于30℃)电流低于5A的场合最小敷铜宽度为12mil/A。而对2oz板,敷铜宽度至少为7mil/A。这个经验规则仅基于走线的直流电阻。若要减小其感性阻抗和交流电阻,则需要更大的敷铜宽度。

16、已知减小走线电感的最好方法是减小长度,而不是增加宽度。超过某一定限度后再加宽走线并不能显著减小电感。同样,使用1oz或2oz板对电感也无明显影响,也不在于走线是否加“镀层”(给走线镀焊/铜,从而增加有效导线截面)。因此,若由于某些原因,走线长度不能进一步减少,则可以通过将电流前向和返回走线并行的方法来减小电感。

电感之所以出现是因为它们存储了磁能量。该能量存在于磁场中。反过来讲,若磁场消失,则电感也随之消失。通过将两条电流走线平行布置,流过它们的电流大小相等而方向相反,从而使磁场大大削弱。这两条平行走线在PCB的同一面上时,要靠得非常近。若使用双面PCB,最好的办法是将两条平行走线置于板子两面(或相邻层)的相对位置。为加强互耦以消去磁场,这些走线应尽量宽些。

17、对大功率离线反激变换器,二次侧走线的电感会反射到一次侧,从而极大地增加了一次等效漏感,使效率降低。当要应付较大RMS电流,需并联多个输出电容时,上述情况将更严重。但仍可利用消去磁场的方法来减小电感。具体做法如图2所示。在输出二极管布线之后设置两块铜面。其中一块为地,另外一块为输出正端。利用两块并行铜面承载前向和返回电流,基本上可消除通路电感,形成所需的良好的高频续流路径。这种简便的方法对输出电容均流非常有利。

图2

18、对单面板,保证若干并联输出电容均流的常用方法如图3所示。虽然不能使电感减到最小,但它确能保证下游的第一个电容不会由于电流路径过长而不均流。注意右图的布线,所示三条路径从二极管经过每个电容的路径总长基本相等,从而产生更精确的均流。

图3

19、对多层板,通常做法是将全部一层作为地。已知每个信号都有回路,随着谐波增高,其返回电流将不是沿着直流电阻最小的那条路径(直线),而是沿着地对应电感最小的路径甚至是“之”字形路径。因此通过设置一层地,就能给返回电流提供阻抗最小(直流电阻最小还是感抗最小,这取决于谐波频率)的路径。地还能帮助处理一些热问题,如将热量传递到另外一方。地还能容性地吸收其上层走线的噪声,从而一定程度减少噪声和电磁干扰。但若不小心也会造成辐射,这种情况可能在耦合了太多走线噪声时发生。地吸收了噪声就会受到影响,特别是铜皮很薄时情况更严重。

20、通常认为最重要的信号走线是反馈走线。若这条走线吸收了噪声(容性的或感性的),就会使输出电压产生些许偏移——极端情况(较少见)甚至造成不稳定或器件损坏。应使反馈走线尽量短,并远离噪声或磁场源(开关、二极管和电感)干扰。绝不能将反馈走线置于电感、开关或二极管下方(即使是 PCB的另外一面的下方),也不能让它靠近或平行噪声走线超过2mm~3mm,即使PCB的临近层也要这样考虑。

有地处于中间层时,应在层间提供足够的屏蔽保护。有时使反馈走线很短是不现实的,应认识到使走线尽量短并非第一位的要求。事实上,经常会有意识地将它布得长一些,以便使这些走线避开潜在的噪声源。也可小心设计,使部分反馈走线穿过地没有返回电流流过的部分,这将使得它免受干扰。

-

开关电源

+关注

关注

6465文章

8342浏览量

482224 -

变换器

+关注

关注

17文章

2100浏览量

109339 -

布线

+关注

关注

9文章

772浏览量

84345 -

buck电路

+关注

关注

27文章

484浏览量

46472 -

PCB

+关注

关注

1文章

1808浏览量

13204

发布评论请先 登录

相关推荐

开关电源PCB布线要点

开关电源PCB布线要点

评论