9.1 回路自感和回路互感

在实际中,电流总是在完整的回路中流动,我们把该完整电流回路的总电感称为回路电感。回路电感事实上就是整个电流回路的自感,又称 回路自感 。

电流回路的回路自感就是当回路中流过单位安培电流时,环绕在整个回路周围的磁力线匝数。或者说当回路中电流为1A时,从回路的一端开始,沿着导线行走时遇到回路中所有电流产生的磁力线匝总数,其中包括导线中每一段的电流分布对其他各段的贡献。

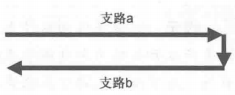

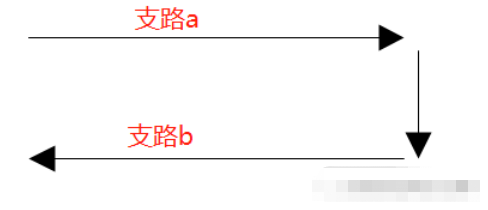

图示有两条直线支路的导线,其中支路a就像信号路径,支路b就像返回路径。当沿支路a并累计其周围的磁力线匝数时,会发现既有源于a自身电流而产生的磁力线圈,即支路a的局部自感,也有源于b的磁力线圈,即支路a和b之间的局部互感。

沿着支路a累计的磁力线总匝数就是支路a的总电感,而沿着支路b累计的就是支路b的总电感,将这两部分相加就是整个回路的回路自感,即

其中,L_loop表示双端回路的回路自感,L_a表示支路a的局部自感,L_b表示支路b的局部自感,L_ab表示支路a和b之间的局部互感。

从式中可以看出,两支路靠得越近,回路电感就越小。其中,各支路的局部自感保持不变而互感增大,互感增大使各支路周围的磁力线匝总数减小,从而使回路自感也减小了。

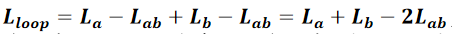

有时说回路自感取决于“回路面积”,这种说法大致是对的,但对于激发我们的直觉却没有多大作用。前面已经看到,面积并非最重要,真正重要的是环绕在每条支路周围的磁力线匝总数。

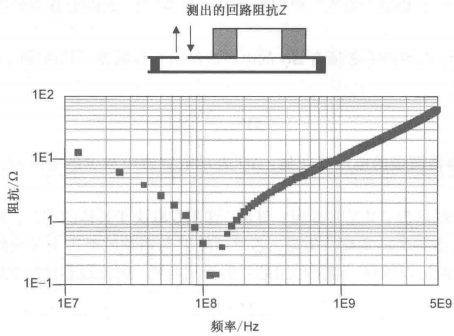

例如,上图示两个形状不同但面积相等的电流回路,局部互感大不一样,两个回路的电感也不相同。一个回路中的两个支路的电流方向相反时,两条支路靠得越近,局部互感就越大,回路电感也就越小。有理由认为回路电感与回路的面积成正比。

当计算回路周围的磁力线总匝数时,必须注意这里的每一条线圈都穿过回路的中心。实际上,计算磁力线总匝数等于在整个回路面积上对磁场强度加以积分。

虽然执行积分的区域明显与面积成比例,但是所积分回路中的磁场强度在很大程度上取决于回路形状和电流分布。

在信号路径和返回路径横截面均匀的特殊情况下,回路电感与长度成比例,并称为互连的单位长度回路电感。在扁平电缆中,信号路径和返回路径的单位长度回路电感是恒定的。任何阻抗可控互连的单位长度回路电感都是恒定的。

9.2 PDN和回路电感

提到“信号完整性”时,通常会想到反射和线网之间的串扰问题。尽管这些问题很重要,但它们所代表的只是信号完整性问题的一部分。另一些问题则与信号路径无关,而是归咎于电源路径和地路径,称为 电源分配网络(PDN) 。

电源分配网络的用途是在每个芯片的电源焊盘和地焊盘之间提供恒定的电压。根据器件工艺的不同,该电压范围一般为0.8~5V,大多数总体方案中分配的噪声波动预算一般不超过5%。在稳压器和芯片之间有许多互连,如过孔、平面、封装引线和键合线等。

如果进入芯片的电流发生突变(如程序的执行引起某些门的同时切换、时钟边沿处的大量的门将同时切换),则当变化的电流流过电源分配网络的互连阻抗时就会引起电压降,称为 轨道下沉或轨道塌陷 。

要使电流变化时引起的这个电压降最小,电源分配网络的串联阻抗就要小于一定的值。这时,尽管电流还在变化,但只要阻抗足够小,阻抗上的电压降就会保持在容许的5%波动范围内。

要使电源分配网络的阻抗比较小,有两条设计原则:低频时,添加具有低回路电感的去耦电容器;高频时,使去耦电容器和芯片焊盘之间的回路电感最小,以保持它们之间的阻抗低于一定的值。

实际电容器的两端和芯片焊盘相连的那段线条会有相应的回路电感。该回路电感与理想电容元件相串联,导致实际电容器的阻抗随频率的升高而增大。

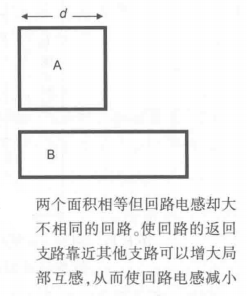

上图是1nF 0603去耦电容器实测的阻抗曲线图。这是从电容器一端经元件下面的平面到另一端的回路阻抗。低频时,正如理想电容器,阻抗随频率的增大而减小。

但是,随着频率的升高,从某一点起,串联的回路电感开始在阻抗中起主导作用。该点的频率称为 自谐振频率 ,此后阻抗开始增大。

当频率大于自谐振频率时,电容器的阻抗与电容量完全无关,只与相应的回路电感有关。所以,频率较高时,如果想减小去耦电容器的阻抗,就要减小相关的回路电感,而不是靠增大电容量。

去耦电容器的一个重要特性是:在频率较高时,阻抗仅与回路电感有关,此电感称为 等效串联电感(ESL) 。所以,频率较高时,减小去耦电容器的阻抗实际上就是设法减小芯片焊盘和去耦电容器引脚之间这一完整路径的回路电感。

减小去耦电容器的回路电感的最好方法有以下几种:

- 使电源平面和地平面靠近电路板表面层,以缩短过孔;

- 使用尺寸较小的电容器;

- 从电容器焊盘到过孔之间的连线要尽量短;

- 将多个电容器并联使用。

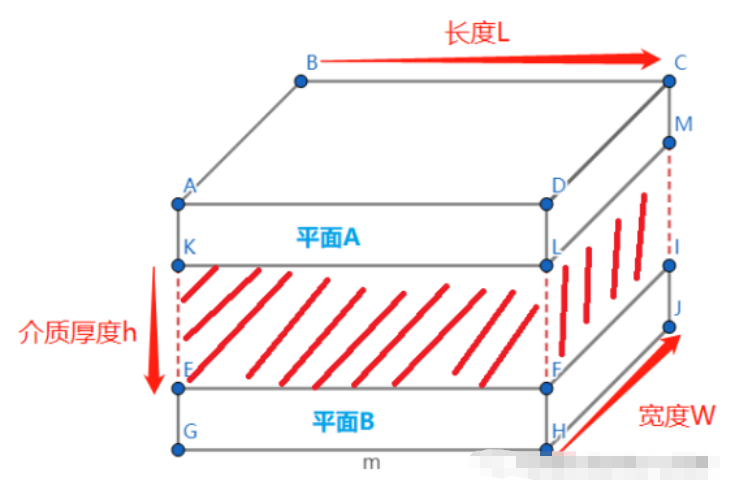

9.3 方块回路电感

由两个平面构成电流路径的回路电感,取决于每个平面路径的局部自感和它们之间的局部互感。平面越宽,电流分布就越扩散开,平面的局部自感就越小,从而回路电感也就越小。平面越长,局部自感就越大,从而回路电感也就越大。平面间距越小,平面之间的互感就越大,从而回路电感也就越小。

假设电流从平面的一边均匀地流向另一边。当该区域为正方形,即长度等于宽度时,无论边长是多少,长和宽之比始终等于1。一对平面上的边长为100 mil的正方形区域和边长为1in的正方形区域的回路电感相同。平面对上的任一正方形区域的回路电感都相同,这就是为什么使用平面的“方块回路电感”这一术语的原因,或者可以简称为电路板的“方块电感”。需要指出,它实际上是指当平面上的正方形区域的远处两边短接在一起的情况下,在近处两边之间的回路电感。

随着相邻平面间距的增加,局部互感将减小,抵消磁力线匝总数的互磁力线圈也减少了。此时,电介质越厚,回路电感就越大,轨道塌陷噪声也就越大。这使得电源分配网络噪声更加严重,驱动外部电缆中共模电流的地弹噪声也会增加,从而引起电磁干扰问题。

电源平面和地平面尽可能地靠近,就可以减小平面对的回路电感,同时减小轨道塌陷、平面上的地弹和电磁干扰。

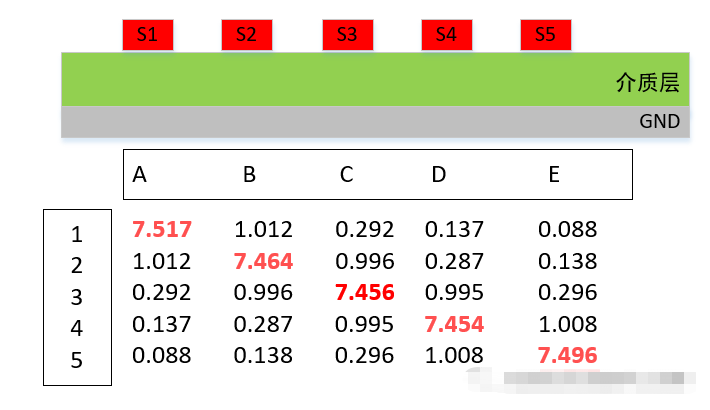

9.4 平面对与过孔回路电感

平面对之间的电流并不是从一边直接流向另一边的。从分立去耦电容器到芯片封装引脚,它们与平面的连接更像是点接触。在前面的分析中,假定电流沿着平面是均匀流动的。然而实际中电流并不是均匀流动的。如果电流由于点接触而受到限制,那么回路电感将会变大。

平面间的回路电感增大是由于过孔限制电流的流过形成了很高的电流密度。对电流流动的限制越大,局部自感和回路电感就越大。这种回路电感的增加常常称为 扩散电感 。如果接触孔面积增大,电流密度就会降低,扩散电感就会减小。

两平面之间的回路电感,即使考虑扩散电感,也与平面间距成正比。电源和地平面之间的介质厚度越薄,方块电感和扩散电感就越小。同理,平面之间的介质越厚,扩散电感也就越大。

接触过孔到电源地平面之间的扩散电感通常要比方块回路电感大,为了准确估计平面的回路电感,必须充分考虑扩散电感。

接有许多电容器和封装引脚的一对平面,许多对过孔的电流都汇集到同一对平面上,此时减小平面间距可以减小由同时电流突变dl/dt产生的压降。

与去耦电容器相关的平面对的回路电感,其值主要取决于扩散电感值,而不是电容器与芯片之间的距离。去耦电容器的总回路电感与它距离芯片远近的关系也比较弱。当然,电容器距离芯片越近,被局限在芯片附近的高频功率和返回电流就越多,从而返回平面上的地弹电压就越低。

让去耦电容器靠近高功耗芯片,可以把返回平面上的高频电流局限在芯片附近,并使之远离电路板上的I/O区域。这样,就可以把驱动外部电缆中的共模电流和引起电磁干扰问题的地弹电压噪声最小化。

-

稳压器

+关注

关注

24文章

4276浏览量

94445 -

信号完整性

+关注

关注

68文章

1418浏览量

95802 -

电磁干扰

+关注

关注

36文章

2347浏览量

105776 -

PDN

+关注

关注

0文章

83浏览量

22814 -

去耦电容器

+关注

关注

0文章

28浏览量

9032

发布评论请先 登录

相关推荐

浅析信号完整性的回路自感和回路互感

浅析信号完整性的回路自感和回路互感

评论