新思科技一直致力于打造“人人都能懂”的行业科普视频,传播更多芯片相关小知识,解答各类科技小问题。每周3分钟,多一些“芯”知识。

在解释集成电路上晶体管的工作原理之前,我们得先来聊聊最常用的硅(和它元素家族)的特点。

硅原子作为一个大哥,最外层围绕着四个电子。硅原子排列成晶体时,最外层电子正好两两组队,形成稳定的八电子结构,也就是很难游离成为自由电子。缺少了自由电子,纯硅在室温下的导电率就很低,基本就是个绝缘体。

众所周知,集成电路用的硅是半导体,可是纯硅都绝缘了还怎么玩?我们可以在纯净的硅晶体中强行加入比硅活跃的其他原子小弟来增加自由电子,让不纯的硅可以一点点导电但又不怎么导电,这就是半导体。强行加入较活跃原子的过程叫做掺杂,目的就是大幅度提升硅的导电率。掺入容易游离出自由电子的原子,就是N型半导体。掺入电子不容易游离的原子,可以理解为游离出来的自由电荷是缺少电子的空洞正电荷,称为空穴,这种就是P型半导体。

当我们把这两种性质相反的半导体连在一起时,就形成了一个PN结。为什么谈到PN结呢?因为PN结在集成电路中无处不在。不施加外部电压时,PN结无法导电。如果在N这一侧加入巨量的自由电子,让自由电子的浓度高过P型的空穴,这样P型就临时变成了N型,也就能导电了。反向操作的话,只要电压不足够高,PN结没怎么变化,始终不导电,这样还能当作电压保护使用。结构简单的单向导电器件二极管就是利用这个原理。

把两种性质的半导体做成两个PN结的三明治结构,这就是1946年的诺贝尔物理学获奖内容,双极晶体管(简称BJT)。它工作的原理比二极管稍微复杂一点,但依然是通过控制三明治每部分的电压让整个三明治完全导通。BJT导通时电阻比较小,电流比较大。所以在讲究省电的数字集成电路里面,更多使用的是另一种以PN结为基础的晶体管:金属-氧化物-半导体-场效应晶体管,简称MOSFET。

MOSFET的工作原理看起来也是通过控制不同区域的电压让晶体管导通,可是本质上和BTJ有极大的差异。

首先,PN结在MOSFET里的作用不是用来控制导电,相反是让电流无法通过,只让电流在指定区域里经过。控制电流经过的指定区域就比较特别了,是一个与电流通过方向垂直的金属层/绝缘层/半导体的三明治结构(MOS结构)。例如对一个P型半导体,在金属层上接正电压,就会通过绝缘层形成一个垂直方向的电场。在电场作用下,正电荷被推远,负电荷也就是电子被拉向半导体和绝缘层的接触面上。当电压足够高,电场足够强时,P型半导体和绝缘层的接触面上就不再是P型了,而出现了非常非常非常薄的N型半导体层,电子就可以在其中移动了。

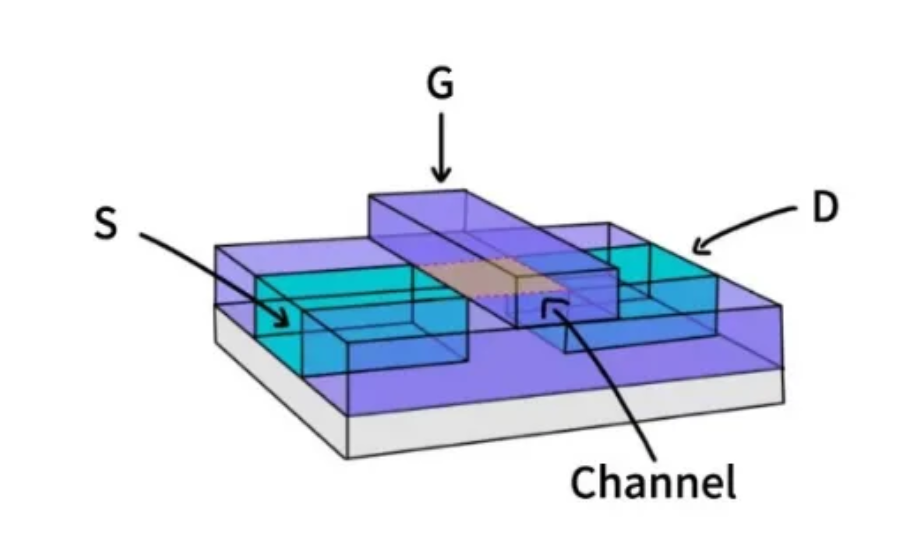

这层受MOS结构控制出现的反类型半导体的电荷通道channel就叫做沟道。金属层就是控制沟道的栅极gate(G极)。我们在半导体制造工艺上常说的xx纳米工艺,本意就是指G极的长度,也可以简单理解为沟道的长度。

在沟道的两端接上和移动电荷同型的半导体,再在它们上加上一个和沟道水平的电场,这些游离电荷(载流子)就能从一端出发到达另一端了。出发端是电荷(载流子)的源头,叫做源极source(S极)。到达端接收到漏过沟道的电荷,叫做漏极drain(D极)。)就能从一端出发到达另一端了。出发端是电荷(载流子)的源头,叫做源极source(S极)。到达端接收到漏过沟道的电荷,叫做漏极drain(D极)。(载流子)就能从一端出发到达另一端了。出发端是电荷(载流子)的源头,叫做源极source(S极)。到达端接收到漏过沟道的电荷,叫做漏极drain(D极)。

在MOS结构中,水平方向的电场决定有没有电流可以流通,而垂直方向的电场控制电流能不能通过。这就是MOS结构的场效应晶体管,所以它叫做MOSFET。当一个MOSFET关断时,几乎没有电流通过。而导通时,电流也仅仅在沟道里流通。所以MOSFET的工作电流相对小,换句话说,有着省电的天然优势。

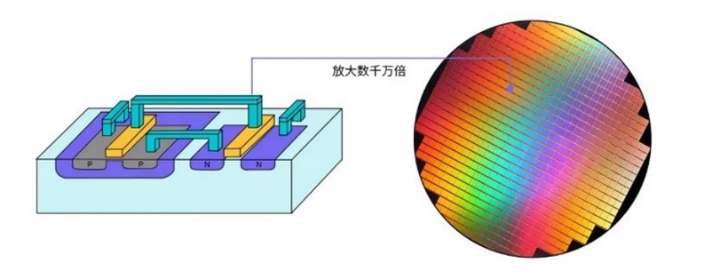

在芯片制造上,MOSFET还有另一个巨大优势。一个完整的CMOS里,一个N型和一个P型MOSFET同步制造一体成型。它们的G极和D极各自连接在一起。当G极上给逻辑状态1的时候,D极就能出现状态0的响应。一个二进制逻辑上的反向器就这么简单而有极其紧凑地做出来了。这个紧凑的结构就是经典的CMOS。

凭借省电和制造上的两大优势,MOSFET自然而然就成了集成电路中的绝对主力老大哥了。

FinFET横空出世

随着芯片制程越来越小,传统平面结构的MOSFET已经难以达到设计指标。因为晶体管尺寸不断缩小,S与D间的沟道就不断变短。当沟道短到一定程度时,即便没有施加电压,S和D也会因为传说中的量子效应变得微弱导电,直接来说就是随时随地都在“漏电”。这就是半导体器件物理中说的“短沟道效应”。

为了极大程度上抵消掉短沟道效应,华裔科学家胡正明教授于1999年发明的3D鳍式场效应晶体管的新型MOSFET构造,简称FinFET。而FinFET也成为了半导体工业中延续摩尔定律的革命性技术。

在FinFET的构造中,首先是沟道的水平宽度大幅缩减,然后增加其高度,呈现出类似鱼鳍的形状,这也正是FinFET名字的由来。一句话解释:FinFET把平面MOSFET的沟道立了起来。因此栅极被设计成了叉状3D架构紧紧包裹住“鱼鳍”状的沟道。如此一来,FinFET的栅极就可以在传统的上方以及垂直的两侧共同控制沟道的导通与关断。这样不仅能够改善电路控制和减少漏电流来抵消掉短沟道效应,同时还能让晶体管整体结构中的长度得以大幅缩减,从而进一步帮助缩小芯片单位面积。

原理听起来很简单是不是,但如何在硅片上制造这些“鱼鳍”却相当困难。单个“鱼鳍”的尺寸是最小栅长的0.67倍。举个具体的例子:对于22nm的工艺,单个“鱼鳍”的宽度仅为14.67nm,这个尺寸远小于最精密浸入式***所能制造的最小尺寸。

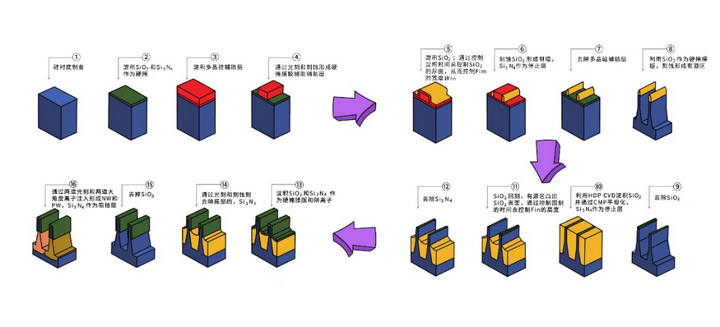

这里是FinFET的工艺流程图,只是简单描述了前段制造流程。大家可以脑补一下完整制造过程的复杂程度。

再说说器件材料上的差异吧。有别与传统平面MOSFET,FinFET的沟道通常较少掺杂甚至不掺杂,比起传统较多掺杂的平面器件,载流子的迁移率得到了大幅度的提高,也就是说单位电流更大。因为有效抵消掉短沟道效应和增强了栅极控制能力,FinFET还可以使用更厚的氧化层来减少栅漏电流。

随着FinFET技术一路从22nm用到5nm芯片,俨然成为了先进芯片市场上的主流,也取得了商业上的巨大成功。但当半导体制造工艺推进到3nm时,静态电流泄露的问题变得越来越严重,棘手的短沟道效应再次出现。

GAA技术:鳍式的“再进化”

既然短沟道效应又出现了,那我们再按照FinFET的思路走一遍试试?如果FinFET三面包住还不够,我们干脆就把它四面全部都包起来!没错,GAA技术就是用的这个方式突破了FinFET的瓶颈。

GAAFET,全称Gate-All-Around FET是通过堆叠多个水平的纳米片或纳米线,并将MOS结构包裹住纳米片(线)的每一个侧面,让纳米片(线)的每个表面全是沟道的设计理念。

相比FinFET,GAA技术能够让晶体管得以承载更多的电流。在FinFET中,需要通过多个垂直的“鱼鳍”并排放置以增加电流,GAA则通过水平堆叠实现了对FinFET的全面增强。在栅极控制能力方面,四面全包裹也比三面包裹的FinFET更胜一筹,因此GAA技术能够更为精确地控制电流。

毫无疑问在当下,GAA对解决3nm及以下尺寸的半导体制造问题尤为关键。在3nm到2nm的阶段,业界最强的三家晶圆制造企业都不同程度上选择了GAA。

新思科技作为覆盖了从硅的生产制造、芯片设计及制造的全流程EDA和IP解决方案的全球领导者,也与晶圆厂长期紧密合作。通过DTCO (Design Technology Co-optimization)协同优化先进的工艺技术解决方案,积极支持更先进的新型晶体管工艺。

本着延续摩尔定律的目标,以从平面向空间的发展逻辑,许多创新的架构设计如今也在崭露头角:如Forksheet、CFET、Bizen晶体管等等。也许未来的晶体管的主流架构,就在这些创新方案之中,让我们拭目以待吧!

审核编辑:彭菁

-

集成电路

+关注

关注

5469文章

12726浏览量

376143 -

二极管

+关注

关注

149文章

10484浏览量

179953 -

半导体

+关注

关注

339文章

31438浏览量

267423 -

晶体管

+关注

关注

78文章

10458浏览量

148865 -

电压保护

+关注

关注

0文章

44浏览量

17073

原文标题:【了不起的芯片】硅片上打造“鲨鱼鳍”,芯片的世界已经变成这样了吗?

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

MOS晶体管

什么是达林顿晶体管?达林顿晶体管的基本电路

集成电路上晶体管结构的那些事儿

集成电路上晶体管结构的那些事儿

评论