针对I/O需求数目更多的低功耗应用,Actel可以提供IGLOO PLUS系列,规模分别是3万、6万和12.5万门。和相同封装的IGLOO器件相比,可以提供最多多出64%的I/O。其所有的器件都支持4个I/O Bank。在多电压应用环境中比较有利,并且支持热插拔和施密特触发器。Actel在IGLOO系列产品的开发过程中,对静态功耗的主要物理来源——漏电流方面做了改进。同时在生产过程中对产率、速度以及可靠性做了严密的监控。

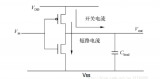

采用IGLOO器件的低功耗优势从哪些方面获得呢?首先来自IGLOO器件本身对漏电流源头的控制,以及器件所提供的各种节省功耗的特性的实现和各种最少功耗数据存储技术的实现。除此之外,设计中采用一些低功耗技巧,也可以降低静态功耗。

IGLOO具有功耗友好的器件架构,能提供静态、睡眠、Flash*Freeze功耗模式,允许采用动态电压和频率调节技术来降低系统整体实际功耗。提供可选择的1.2V和1.5V的I/O和核电压,以方便用户平衡设计的性能和功耗之间的关系。IGLOO的时钟结构可以没有副作用的对全局信号和局部信号进行门控制。另外IGLOO的RAM模块具有LP和F*F端口来控制RAM本身的静态功耗。系统温度及功耗概况

工业、汽车电子、军事, 甚至商业类客户都会对系统的温度和运行模式的概况有规定。这些概况指引我们在设计时要注意哪些地方以及精力该如何分配。IGLOO器件的低功耗工艺和硅片设计由Actel来保证,用户所要关注的是:关心器件的选型、掌握所使用的FPGA的架构、掌握PCB的板级布局(主要是电容及I/O的走线)。

对于同一系列的器件来说,器件的die越小,器件的功耗也会越小。也就是说,在选用器件的时候,应该尽量选择规模小的器件。选定器件后,可以在设计过程中,通过一些技巧尽可能的少占用资源,比如通过时分复用的方式少占用I/O,共享加法、乘法等算法逻辑,共享RAM等,同时也有必要了解所选用的FPGA的架构。

用户需要在功耗和速度之间做平衡,在对速度性能要求不高的时候,尽量使用低的核电压和低电压的I/O接口标准。根据设计工作的实际状况,在某些时候将当前不工作的资源关掉,比如通过控制SRAM的LP或BLK引脚,使其在不工作的时候可以被关断,或者是通过Flash Freeze端口进入Fresh Frezee模式以降低静态功耗。在PLL不需要工作的时候,通过Power Down引脚将其关掉,不过需要注意的是,需要考虑重新开启以后,PLL的锁定时间对系统是不是有影响。关掉没有输入总线的I/O Bank。

注意,不要滥用上拉/下拉电阻。在活动模式下,如果总线被反向模式驱动(如上拉的被“0”驱动,或下拉的被“1”驱动),那么每个I/O上的电流会增加。要预防被驱动的总线进入3态状态。除非FPGA的工作时间确实短,否则建议跟板子设计者沟通以确保对输入进行持续的驱动。

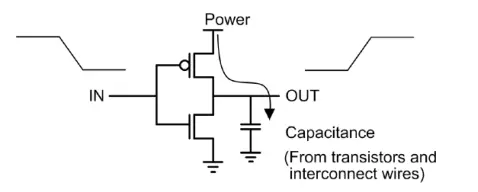

要降低设计的动态功耗,首先要了解影响动态功耗的因素。动态功耗通常和电压、信号翻转频率、容性负载正相关,设计所占用的逻辑资源越多、时钟频率越高、I/O和RAM越多,动态功耗就越大。同时也需要分析设计的动态功耗概况。

确定要降低的动态功耗的目标,如果要降低的动态功耗的目标是目前整个系统动态功耗的20%,那么选用Actel的IGLOO器件或许就可以实现所要达到的目标。如果目标是80%,那么除了选用IGLOO器件外,还需要从系统和架构上去考虑。

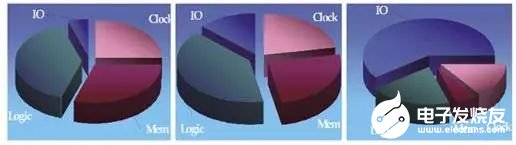

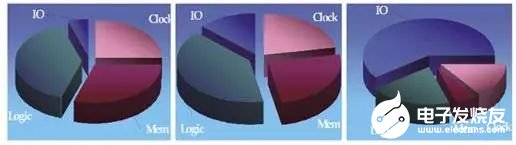

针对不同的系统功耗的概况,梳理动态功耗的重点,见图1。针对Case1中动态功耗的示意图,我们可以看出其功耗主要分布在逻辑、存储和时钟方面,这样我们的精力就不能放在如何降低I/O的功耗上去,而针对Case3这种情况,如果要降低动态功耗,就必须要解决I/O上的功耗问题。

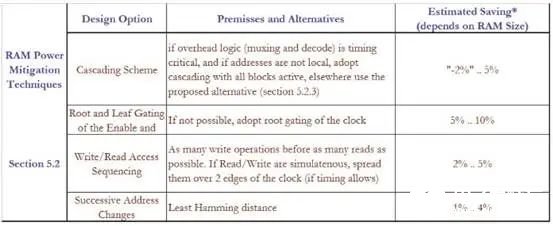

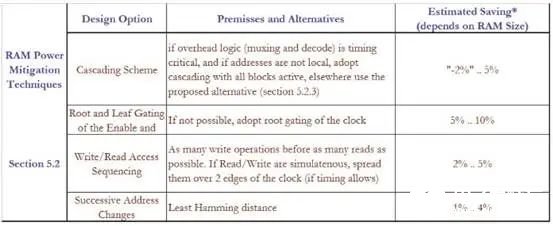

要减少RAM的功耗,除了对RAM的控制和时钟信号进行门控制以外,还需要知道RAM的读和写分别对功耗的影响有多少。地址变化、读写顺序、RAM级联方式对功耗的影响。

对RAM进行读操作涉及到:控制所存地址和控制锁存、行的预译码电路、读的列译码电路、行的最终译码电路、读的列译码控制、传感放大器、数据输出选择和锁存电路、Sense enable logic、读控制电路、Bit-line预充电电路等十个相关电路。而对RAM进行写操作需要涉及到的电路有:地址和控制锁存、行的预译码电路、写的列译码电路、行的最终解码控制、写的列译码控制、写驱动电路和Bit Line预充电电路。因此,相比较而言,读操作会比写操作消耗更多的功耗。

RAM的读写地址改变的方式,也会对功耗有不同的影响。连续操作地址之间的汉明距离越小,产生的功耗也越小。反之亦然。也就是说当前操作的地址和上次操作的地址之间变化的位数越少,所产生的功耗也会越小。

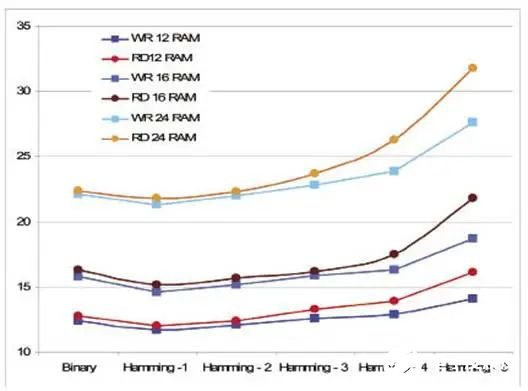

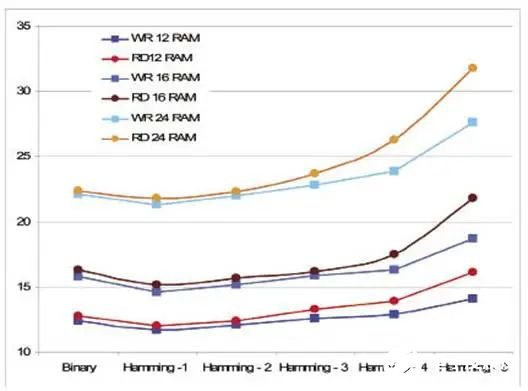

读写间隔操作和连续读、连续写操作相比,要产生多一些的功耗。从图2中分别对12块RAM、16块RAM和24块RAM做的测试结果看,同样的操作条件下,RAM块数越多,连续操作地址之间的汉明距离越长,功耗就越大。同样的块数和连续操作之间的汉明距离,写-读三次会比三次写三次读消耗的功耗要大。

图1 不同系统的动态功耗在线座谈精华

图2 写读操作顺序vs.读序列后跟写序列操作

通过前面所述,我们可以通过调整RAM的访问顺序降低RAM的功耗。可能的话,对RAM少进行读操作,尽可能一次多读一些数据或者多写一些数据,少一些读写操作之间的切换。如果在连续相同操作的地址之间,汉明距离能保持最小的话更好。也可以考虑在反向时钟沿上对RAM进行读写操作,以降低RAM的峰值功耗。

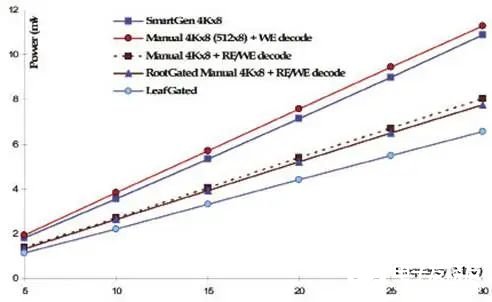

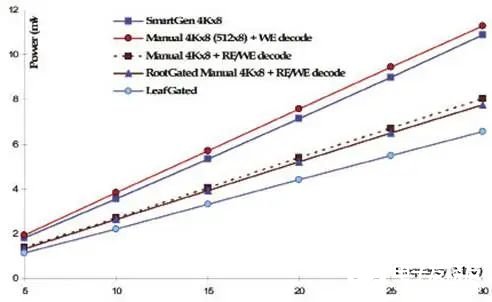

不同的RAM级联架构所产生的功耗也不同。如果想获得一个4K×4的RAM,有许多不同的实现方式。从图3中可以看出,根据这些不同的实现方式,对每块RAM的读写时钟控制,进行门控制所产生的功耗是最低的。

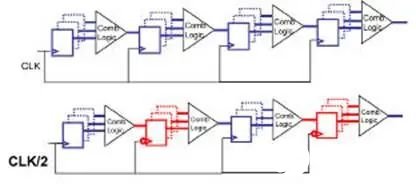

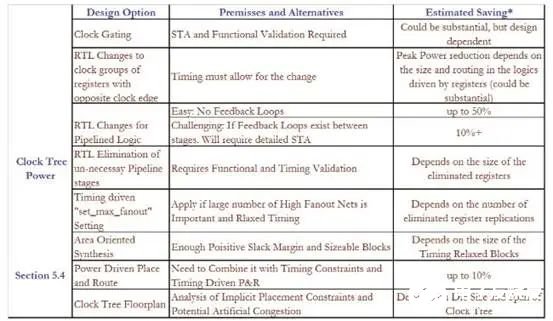

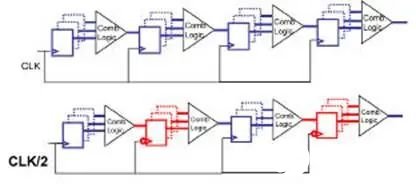

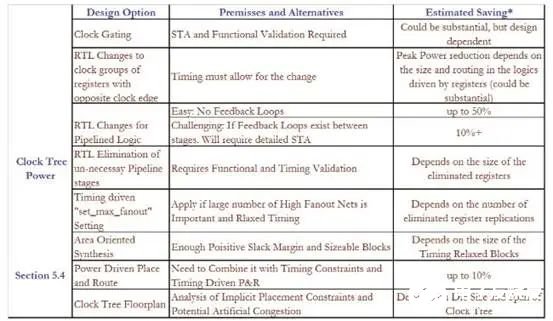

在降低时钟树的功耗方面,常用的方法有使用门控时钟,对常用的流水线时钟结构进行修改,尽量使用FPGA内部的全局时钟资源等。通过对常用的流水线时钟结构在RTL级进行修改,就像在图4中所看到的,做正反时钟沿间隔,这样时钟频率可以减慢一半,可以节省该时钟路径一半的功耗。同样可以通过人工对时钟域进行平面布局,来降低时钟树产生的功耗。这种方式对工程师的要求相对较高。Actel的设计师提供基于功耗驱动的布局布线策略。选择该策略,布局布线工具自动会在满足时序要求的情况下,尽可能的降低布局功耗。

图3 根时钟vs.叶时钟vs.门控允许

图4 对常用的流水线时钟结构在RTL级做修改

要降低逻辑和走线的功耗,需要调整综合选项、了解算法/功能块的架构和功耗概况,通过减少信号的翻转来降低功耗。不同的综合选项和策略会对动态功耗有影响,基本上需要注意的是全局时序的设定以及set_max_fanout选项,以及是选用面积优先还是时序优先的综合策略。

通过对DesignWare和一些私有的加法器和不同频率下的功耗的评估,DesignWare下面的BK加法器在功耗方面是最友好的。针对同样5%到10%的速度降级,BK加法器和其他的私有加法器的核相比,可以减少10%到15%的面积和功耗。在选择乘法器的时候,必须要考虑乘法器的面积、功耗和速度。

计数器在设计中有不同的用法,有的用于计算事件发生的顺序或者用掉的时间,有的用于驱动类似于RAM的地址总线、数据总线、状态机的下一跳状态或者输出逻辑,有的用于当输出的值达到不同的解码值时做不同的设定的处理。根据不同的用途可以考虑用二进制顺序计数、格雷码计数、环形计数的实现方法。如果计数器只是用于产生一些标记,建议采用二进制的实现方式;如果计数器用于驱动一个大的负载总线,建议用格雷码计数器;如果多个计数器的值需要被解码,环形计数器是最佳选择(译码逻辑是最小的)。

通过降低逻辑的翻转率来降低动态功耗

首先在设计中,需要尽量避免不必要的翻转,可以通过下面几个步骤来实现这一目标:首先分析哪些逻辑的翻转是不必要的,随后对不必要的逻辑翻转的传播进行限制,展开逻辑翻转的时间。

减少逻辑可能产生的毛刺,先标识出翻转率高的网络以及它们的驱动,然后对驱动单元输入的最坏时序情况做评估,随后将毛刺的源往前调或往后调,然后对驱动单元的输入的最坏时序情况做评估,最后在驱动的逻辑后面插入一级触发器,根据先前的评估情况来决定用路径上其他时序元件的相同时钟沿或者相反的时钟沿来驱动触发器。即使是在单周期路径上面,如果有足够的slack来增加一个与门以及相关走线,那么就可以用与门的另外一个输入(毛刺源驱动寄存器)的反相时钟沿,从而减少毛刺。在某些情况下,可以通过伸展反转时间来降低毛刺的峰值功耗。

建议设计者要了解最终系统的运行模式,以及每种模式下系统的功耗概况。如果系统处于睡眠模式或者关闭模式的时间较长,需要观察浪涌电流和编程电流的影响,并处理好静态功耗。需要检查设计的动态功耗概况,找出功耗的主要瓶颈,根据概括表(图5~图8)找出最好的解决方法。

图5 RAM 动态功耗概括表

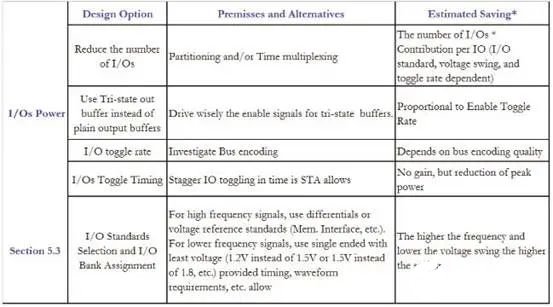

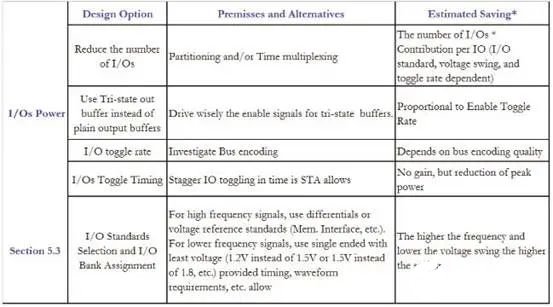

图6 I/O功耗概括表

图7 时钟树功耗概括表

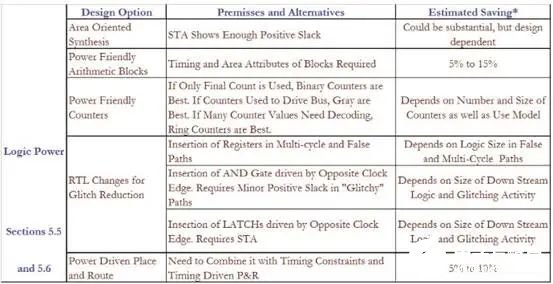

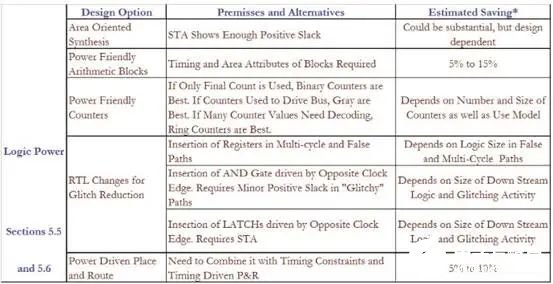

图8 逻辑功耗概括表在对照概括表之前,只要时序允许,可以修改RTL代码;保证修改以后的功能和时序有效性;也可以尝试调整综合选项以及使用基于功耗优先的策略来进行布局布线。

采用IGLOO器件的低功耗优势从哪些方面获得呢?首先来自IGLOO器件本身对漏电流源头的控制,以及器件所提供的各种节省功耗的特性的实现和各种最少功耗数据存储技术的实现。除此之外,设计中采用一些低功耗技巧,也可以降低静态功耗。

IGLOO具有功耗友好的器件架构,能提供静态、睡眠、Flash*Freeze功耗模式,允许采用动态电压和频率调节技术来降低系统整体实际功耗。提供可选择的1.2V和1.5V的I/O和核电压,以方便用户平衡设计的性能和功耗之间的关系。IGLOO的时钟结构可以没有副作用的对全局信号和局部信号进行门控制。另外IGLOO的RAM模块具有LP和F*F端口来控制RAM本身的静态功耗。系统温度及功耗概况

工业、汽车电子、军事, 甚至商业类客户都会对系统的温度和运行模式的概况有规定。这些概况指引我们在设计时要注意哪些地方以及精力该如何分配。IGLOO器件的低功耗工艺和硅片设计由Actel来保证,用户所要关注的是:关心器件的选型、掌握所使用的FPGA的架构、掌握PCB的板级布局(主要是电容及I/O的走线)。

对于同一系列的器件来说,器件的die越小,器件的功耗也会越小。也就是说,在选用器件的时候,应该尽量选择规模小的器件。选定器件后,可以在设计过程中,通过一些技巧尽可能的少占用资源,比如通过时分复用的方式少占用I/O,共享加法、乘法等算法逻辑,共享RAM等,同时也有必要了解所选用的FPGA的架构。

用户需要在功耗和速度之间做平衡,在对速度性能要求不高的时候,尽量使用低的核电压和低电压的I/O接口标准。根据设计工作的实际状况,在某些时候将当前不工作的资源关掉,比如通过控制SRAM的LP或BLK引脚,使其在不工作的时候可以被关断,或者是通过Flash Freeze端口进入Fresh Frezee模式以降低静态功耗。在PLL不需要工作的时候,通过Power Down引脚将其关掉,不过需要注意的是,需要考虑重新开启以后,PLL的锁定时间对系统是不是有影响。关掉没有输入总线的I/O Bank。

注意,不要滥用上拉/下拉电阻。在活动模式下,如果总线被反向模式驱动(如上拉的被“0”驱动,或下拉的被“1”驱动),那么每个I/O上的电流会增加。要预防被驱动的总线进入3态状态。除非FPGA的工作时间确实短,否则建议跟板子设计者沟通以确保对输入进行持续的驱动。

要降低设计的动态功耗,首先要了解影响动态功耗的因素。动态功耗通常和电压、信号翻转频率、容性负载正相关,设计所占用的逻辑资源越多、时钟频率越高、I/O和RAM越多,动态功耗就越大。同时也需要分析设计的动态功耗概况。

确定要降低的动态功耗的目标,如果要降低的动态功耗的目标是目前整个系统动态功耗的20%,那么选用Actel的IGLOO器件或许就可以实现所要达到的目标。如果目标是80%,那么除了选用IGLOO器件外,还需要从系统和架构上去考虑。

针对不同的系统功耗的概况,梳理动态功耗的重点,见图1。针对Case1中动态功耗的示意图,我们可以看出其功耗主要分布在逻辑、存储和时钟方面,这样我们的精力就不能放在如何降低I/O的功耗上去,而针对Case3这种情况,如果要降低动态功耗,就必须要解决I/O上的功耗问题。

要减少RAM的功耗,除了对RAM的控制和时钟信号进行门控制以外,还需要知道RAM的读和写分别对功耗的影响有多少。地址变化、读写顺序、RAM级联方式对功耗的影响。

对RAM进行读操作涉及到:控制所存地址和控制锁存、行的预译码电路、读的列译码电路、行的最终译码电路、读的列译码控制、传感放大器、数据输出选择和锁存电路、Sense enable logic、读控制电路、Bit-line预充电电路等十个相关电路。而对RAM进行写操作需要涉及到的电路有:地址和控制锁存、行的预译码电路、写的列译码电路、行的最终解码控制、写的列译码控制、写驱动电路和Bit Line预充电电路。因此,相比较而言,读操作会比写操作消耗更多的功耗。

RAM的读写地址改变的方式,也会对功耗有不同的影响。连续操作地址之间的汉明距离越小,产生的功耗也越小。反之亦然。也就是说当前操作的地址和上次操作的地址之间变化的位数越少,所产生的功耗也会越小。

读写间隔操作和连续读、连续写操作相比,要产生多一些的功耗。从图2中分别对12块RAM、16块RAM和24块RAM做的测试结果看,同样的操作条件下,RAM块数越多,连续操作地址之间的汉明距离越长,功耗就越大。同样的块数和连续操作之间的汉明距离,写-读三次会比三次写三次读消耗的功耗要大。

图1 不同系统的动态功耗在线座谈精华

图2 写读操作顺序vs.读序列后跟写序列操作

通过前面所述,我们可以通过调整RAM的访问顺序降低RAM的功耗。可能的话,对RAM少进行读操作,尽可能一次多读一些数据或者多写一些数据,少一些读写操作之间的切换。如果在连续相同操作的地址之间,汉明距离能保持最小的话更好。也可以考虑在反向时钟沿上对RAM进行读写操作,以降低RAM的峰值功耗。

不同的RAM级联架构所产生的功耗也不同。如果想获得一个4K×4的RAM,有许多不同的实现方式。从图3中可以看出,根据这些不同的实现方式,对每块RAM的读写时钟控制,进行门控制所产生的功耗是最低的。

在降低时钟树的功耗方面,常用的方法有使用门控时钟,对常用的流水线时钟结构进行修改,尽量使用FPGA内部的全局时钟资源等。通过对常用的流水线时钟结构在RTL级进行修改,就像在图4中所看到的,做正反时钟沿间隔,这样时钟频率可以减慢一半,可以节省该时钟路径一半的功耗。同样可以通过人工对时钟域进行平面布局,来降低时钟树产生的功耗。这种方式对工程师的要求相对较高。Actel的设计师提供基于功耗驱动的布局布线策略。选择该策略,布局布线工具自动会在满足时序要求的情况下,尽可能的降低布局功耗。

图3 根时钟vs.叶时钟vs.门控允许

图4 对常用的流水线时钟结构在RTL级做修改

要降低逻辑和走线的功耗,需要调整综合选项、了解算法/功能块的架构和功耗概况,通过减少信号的翻转来降低功耗。不同的综合选项和策略会对动态功耗有影响,基本上需要注意的是全局时序的设定以及set_max_fanout选项,以及是选用面积优先还是时序优先的综合策略。

通过对DesignWare和一些私有的加法器和不同频率下的功耗的评估,DesignWare下面的BK加法器在功耗方面是最友好的。针对同样5%到10%的速度降级,BK加法器和其他的私有加法器的核相比,可以减少10%到15%的面积和功耗。在选择乘法器的时候,必须要考虑乘法器的面积、功耗和速度。

计数器在设计中有不同的用法,有的用于计算事件发生的顺序或者用掉的时间,有的用于驱动类似于RAM的地址总线、数据总线、状态机的下一跳状态或者输出逻辑,有的用于当输出的值达到不同的解码值时做不同的设定的处理。根据不同的用途可以考虑用二进制顺序计数、格雷码计数、环形计数的实现方法。如果计数器只是用于产生一些标记,建议采用二进制的实现方式;如果计数器用于驱动一个大的负载总线,建议用格雷码计数器;如果多个计数器的值需要被解码,环形计数器是最佳选择(译码逻辑是最小的)。

通过降低逻辑的翻转率来降低动态功耗

首先在设计中,需要尽量避免不必要的翻转,可以通过下面几个步骤来实现这一目标:首先分析哪些逻辑的翻转是不必要的,随后对不必要的逻辑翻转的传播进行限制,展开逻辑翻转的时间。

减少逻辑可能产生的毛刺,先标识出翻转率高的网络以及它们的驱动,然后对驱动单元输入的最坏时序情况做评估,随后将毛刺的源往前调或往后调,然后对驱动单元的输入的最坏时序情况做评估,最后在驱动的逻辑后面插入一级触发器,根据先前的评估情况来决定用路径上其他时序元件的相同时钟沿或者相反的时钟沿来驱动触发器。即使是在单周期路径上面,如果有足够的slack来增加一个与门以及相关走线,那么就可以用与门的另外一个输入(毛刺源驱动寄存器)的反相时钟沿,从而减少毛刺。在某些情况下,可以通过伸展反转时间来降低毛刺的峰值功耗。

建议设计者要了解最终系统的运行模式,以及每种模式下系统的功耗概况。如果系统处于睡眠模式或者关闭模式的时间较长,需要观察浪涌电流和编程电流的影响,并处理好静态功耗。需要检查设计的动态功耗概况,找出功耗的主要瓶颈,根据概括表(图5~图8)找出最好的解决方法。

图5 RAM 动态功耗概括表

图6 I/O功耗概括表

图7 时钟树功耗概括表

图8 逻辑功耗概括表在对照概括表之前,只要时序允许,可以修改RTL代码;保证修改以后的功能和时序有效性;也可以尝试调整综合选项以及使用基于功耗优先的策略来进行布局布线。

有你想看的精彩 至芯科技FPGA就业培训班——助你步入成功之路、9月23号北京中心开课、欢迎咨询! 基于FPGA的摄像机传感器接口 为什么研究浮点加法运算,对FPGA实现方法很有必要?

扫码加微信邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA设计技巧,如何能有效降低静态功耗?

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1629文章

21729浏览量

603037

原文标题:FPGA设计技巧,如何能有效降低静态功耗?

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

TPA3116静态功耗静态电流比较大是什么原因导致的?

关于TPA3116静态功耗大,在TI的论坛里面发现几乎所有的电感发热都是说是因为输出LC电路导致

1,想问一下这个静态功耗静态电流比较大

发表于 10-12 08:35

如何测试TPA3118和TPA3116的静态电流和静态功耗?

1.如何测试TPA3118和TPA3116的静态电流和静态功耗?

2.测试时候需要带负载嘛?(是否需要接喇叭)

3.如果用万用表测试应该怎么测?

发表于 10-12 06:54

物联网系统中TCP低功耗产品长连接状态下降低功耗功能的实现方案

01 概述 TCP相关内容参考文章《物联网行业中TCP通信协议介绍以及如何实现》 02 功耗的组成 低功耗技术就是一系列的降低功耗的技术。 在了解低功耗技术之前,我们必须先了解

谈一谈FPGA设计中的功率计算

和动态功率。 尽管FPGA厂商承诺将提供切实可用的低功耗器件,但由于工艺技术从130纳米缩小到90纳米、65纳米或更加小的线条,晶体管固有的漏电加剧了,静态功耗也增加了。此外,使用

发表于 07-31 22:37

工业物联网系统如何有效降低储能设备运维成本

在现代工业发展的浪潮中,储能设备作为能源体系的重要组成部分,扮演着不可或缺的角色。储能系统不仅可以提高电网的安全性和稳定性,还能有效利用电力峰谷电价差异,降低电力系统的成本。

OPA454如何降低功耗?

opa454 供电+60V/-15V,输出空载悬空,放大倍数5倍,同向放大,输入0~10V正弦波100hz,输出为50v正弦波,发现功耗很大,有降低功耗措施?

发表于 07-29 06:32

wifi smartconfig时功耗比较大,如何降低?

现在wifi 的smartconfig 时候功耗比较大,现在达不到要求,需要在配网时降低10mA。

1,如何通过编程的手段进行降低?

2,这个需要考虑配网时跟路由器之间的距离吗?

发表于 07-10 08:09

FSMC读写NAND后,如何能够拉高NCE片选信号,以求降低功耗?

请教大家问题:

FSMC读写NAND后,如何能够拉高NCE片选信号,以求降低功耗!

手册和实际测试结果只能通过bank切换才能实现!bank2和bank3可以单独切换,释放NCE,但如何同时释放NC呢?

不知道大家有没有遇到这样的问题!

谢谢大家

发表于 04-28 08:36

Synopsys推出一款低功耗静态规则检查工具—VCLP

VCLP(VC Low Power)是Synopsys提供的一款低功耗静态规则检查工具,它能够帮助验证和清洁IEEE 1801 Unified Power Format (UPF)低功耗设计意图,并确保UPF中的

如何降低LoRa模块的功耗以延长电池寿命?

我正在开发一个使用 LoRa模块的物联网项目, 但我发现 LoRa 模块的功耗比较高, 这可能会导致电池消耗得很快.我正在寻找一些建议来帮助我降低 LoRa 模块的功耗以延长电池寿命.我已经考虑了

发表于 03-01 07:38

如何能够实现通用FPGA问题?

FPGA 是一种伪通用计算加速器,与 GPGPU(通用 GPU)类似,FPGA 可以很好地卸载特定类型的计算。从编程角度上讲,FPGA 比 CPU 更难,但从工作负载角度上讲 FPGA

发表于 12-29 10:29

•459次阅读

FPGA设计技巧,如何能有效降低静态功耗?

FPGA设计技巧,如何能有效降低静态功耗?

评论