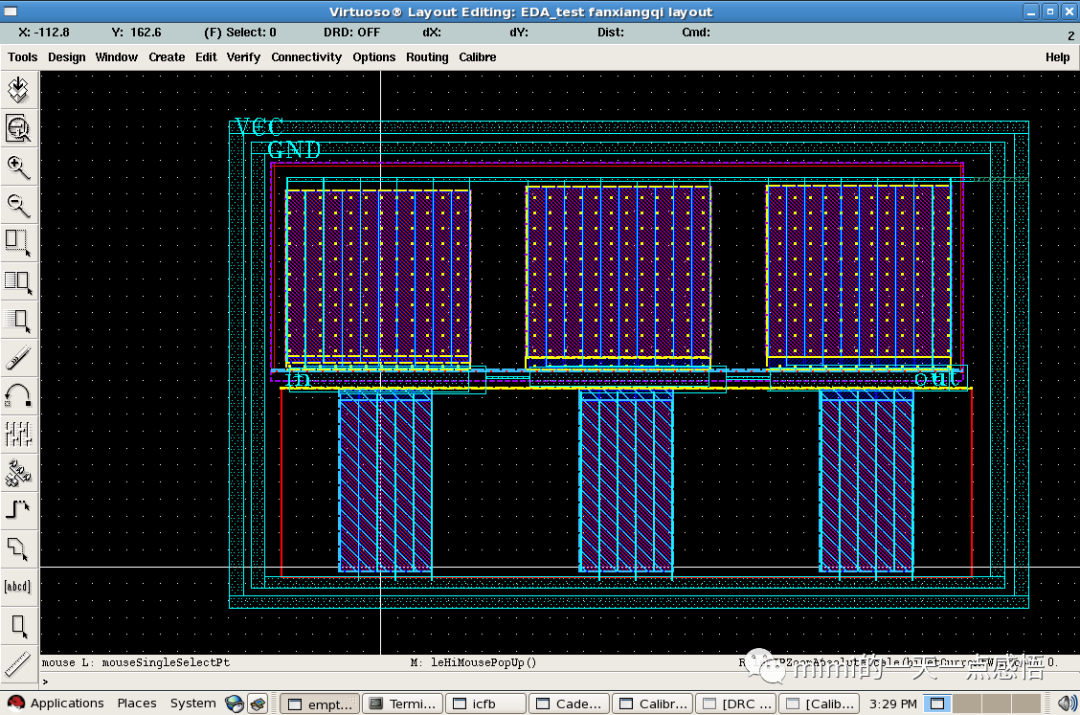

一个版图设计好以后,产生的错误可能是多连了一根铝线造成的Short,或者是少连了几根铝线造成的Open,这样的低级错误对芯片来说都是致命的,因此编辑好的版图要通过LVS(Layout Versus Schematic)与原理图进行核对验证。然后再进行常规的DRC(Design Rule Check)。

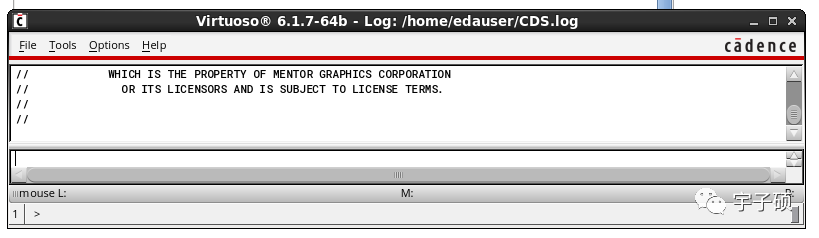

Vertuoso的版图需要通过Mentor公司的Calibre来进行LVS验证和DRC检查(是不是很奇妙?用Cadence公司软件设计的版图,却需要通过Mentor公司的工具来进行验证,原因我也想不通,那就别想了,往下继续看吧!),幸运的是Calibre已经被集成到Vertuoso软件中了,我们不需要再打开另外一个软件界面来操作了。

下面就按照反相器来说明下LVS验证和DRC检查:

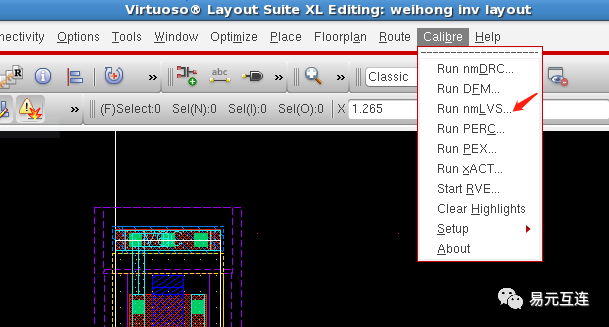

1.打开反相器的PCB,选择Calibre>Run nmLVS...,如下图;

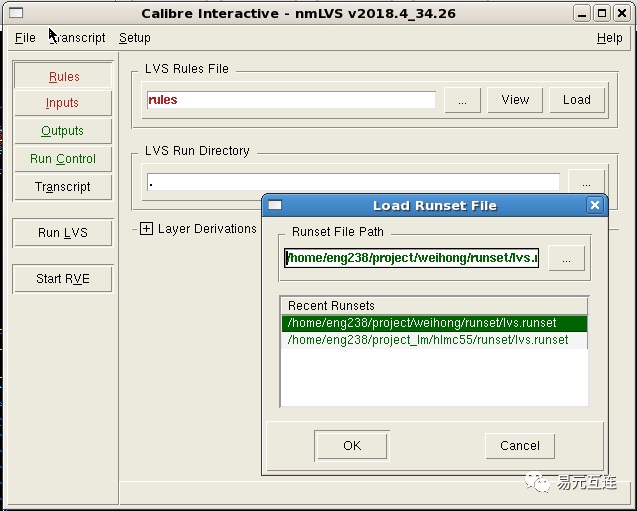

2.然后弹出一个LVS,看到内部还嵌入了一个 Load Runset File文件的对话框,这个是让我们选择保存好的runset文件的,因为要从0开始,就点击"cancel”;

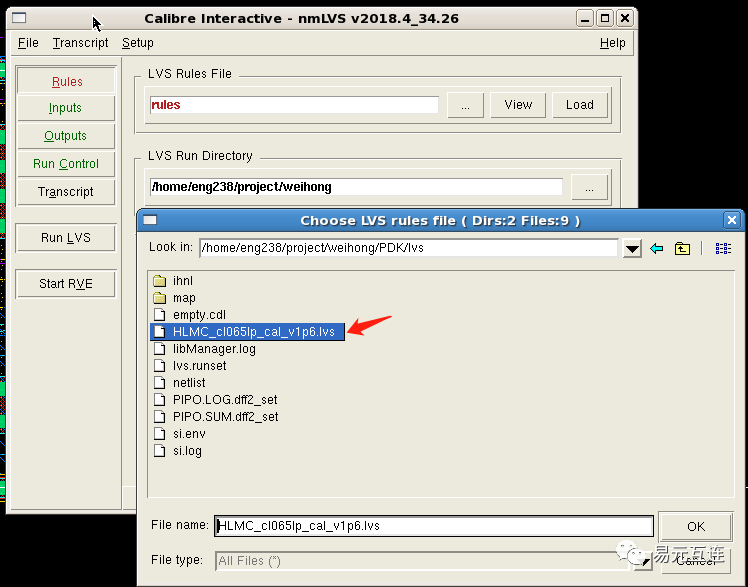

3、点击左侧的Rule标签,在LVS Rule File中选择PDK文件包下的HLMC_cl065lp_al_v1p6.lvs文件,如下图所示;

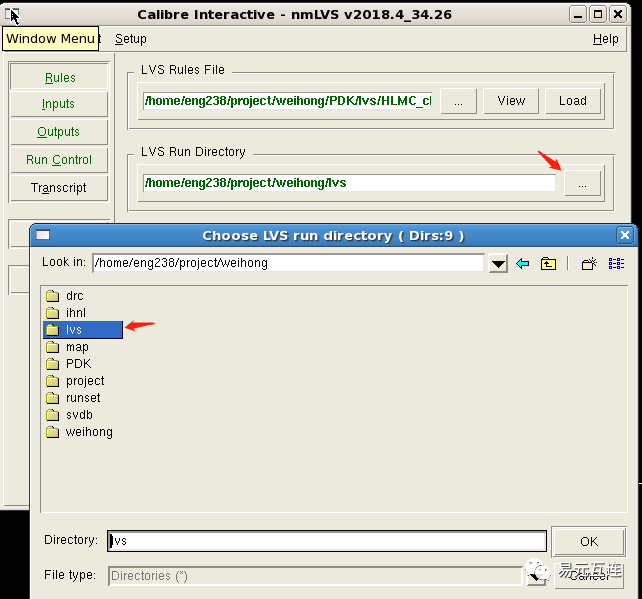

4、在project下新建一个lvs的文件夹(Linix如何新建文件夹,是linix的操作,不属于本章内容,大家可以自行找资料脑补下),然后LVS Run Dire-

ctory的路径选择到该lvs文件内,保留LVS验证时报错的信息;

5、点击左侧Input的标签,选中右侧下的Netlist标签,可以看到Spice Files有一个默认的inv.calibre文件,这个是反相器的Netlist文件,需要添加下其他规则文件,同时选中“Export from layout viewer”(第一次一般颜色不会变红色,需要空运行下LVS后,才能变红);

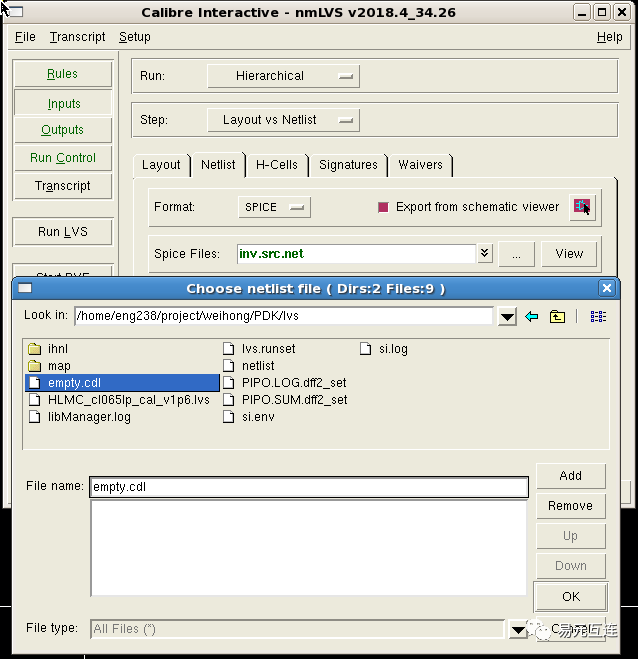

点击Spice Files右侧按钮,选择PDK文件包内的empty.cdl文件后,点击“添加”和“OK”;

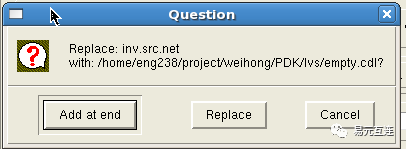

6、在出现的对话框中,选择“Add at end”

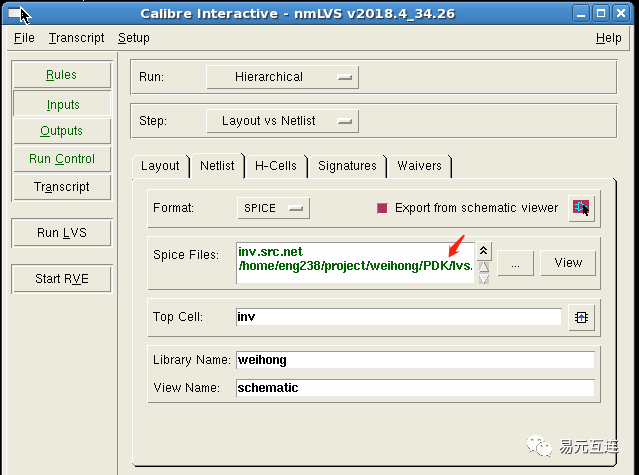

7、可以看到empty.cdl已经被load进Spice Files内了;

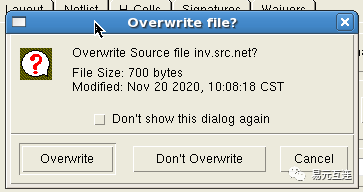

8.然后就可以点击左侧的Run LVS标签,进行LVS验证了,可能会出现要覆盖上次验证结果的确认对话框,直接选择Overwrite覆盖就好了;

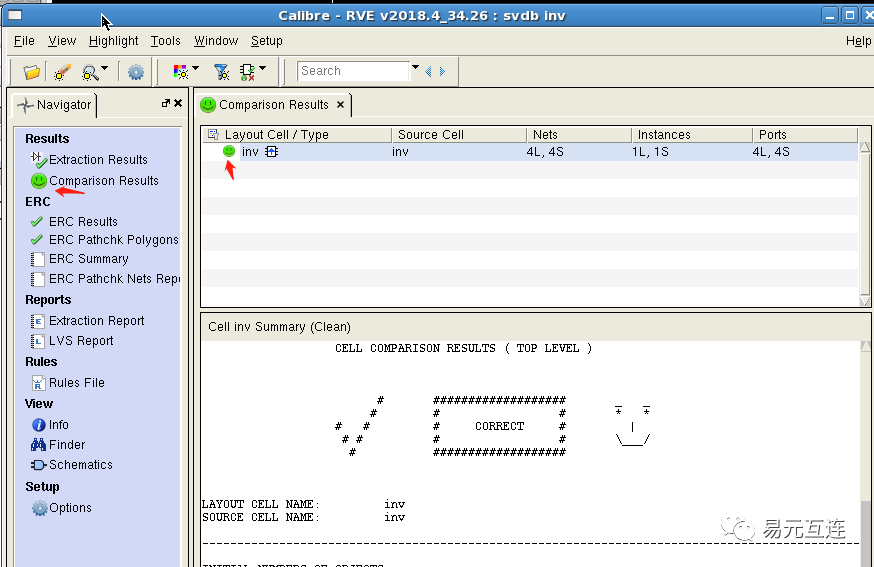

9、最后结果出现了一个绿色的笑脸,这个说明验证是OK的,如果出现黑脸,就是有错误的。

-

反相器

+关注

关注

6文章

311浏览量

43353 -

Cadence

+关注

关注

65文章

923浏览量

142202 -

DRC

+关注

关注

2文章

149浏览量

36202 -

LVS

+关注

关注

1文章

36浏览量

9953

发布评论请先 登录

相关推荐

怎么用Cadence16.5设计集反相器??

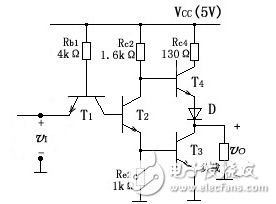

TTL反相器的基本电路(六款TTL反相器的基本电路设计原理图详解)

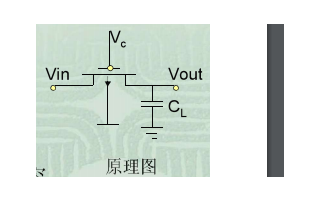

cmos反相器设计电路图

MOS反相器和CMOS反相器的详细资料说明

Candence Virtuoso进行基本的电路设计

Cadence Virtuoso设计的一个反相器LVS验证案例

Cadence Virtuoso设计的一个反相器LVS验证案例

评论