光掩膜版基本上是 IC 设计的“主模板”。掩模版有不同的尺寸。常见尺寸为 6 x 6 英寸一般的掩膜版由石英或玻璃基板组成。光掩膜版涂有不透明薄膜。更复杂的掩模版使用其他材料。

一般来说,术语“photo mask”用于描述与 1X 步进机或光刻系统一起使用的“主模板”。术语“reticle”用于描述 2X、4X 或 5X 缩小步进器中使用的“主模板”。但是,它们基本上是一回事。

掩膜版用在哪里?

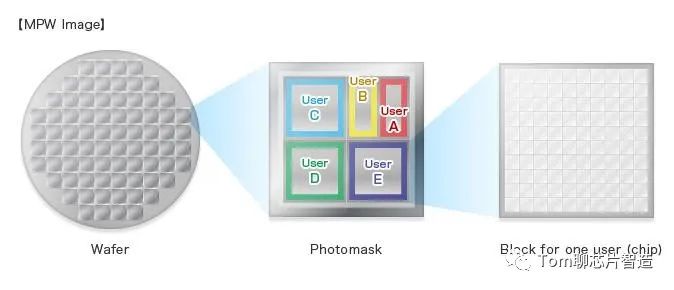

在半导体工艺流程中,芯片制造商首先设计 IC,然后将其转换为文件格式。然后,在光掩模设备中,根据该格式生产光掩膜版。掩膜版是 IC 设计的主模板。它复制了原始的 IC 设计图形。

在晶圆厂中,掩膜版和晶圆被插入***。将光刻胶涂在晶圆上。在操作中,***产生光,光通过光刻系统中的投影光学器件和掩膜版传输到光刻胶表面,即我们所知道的曝光工艺。

怎样制作掩膜版?

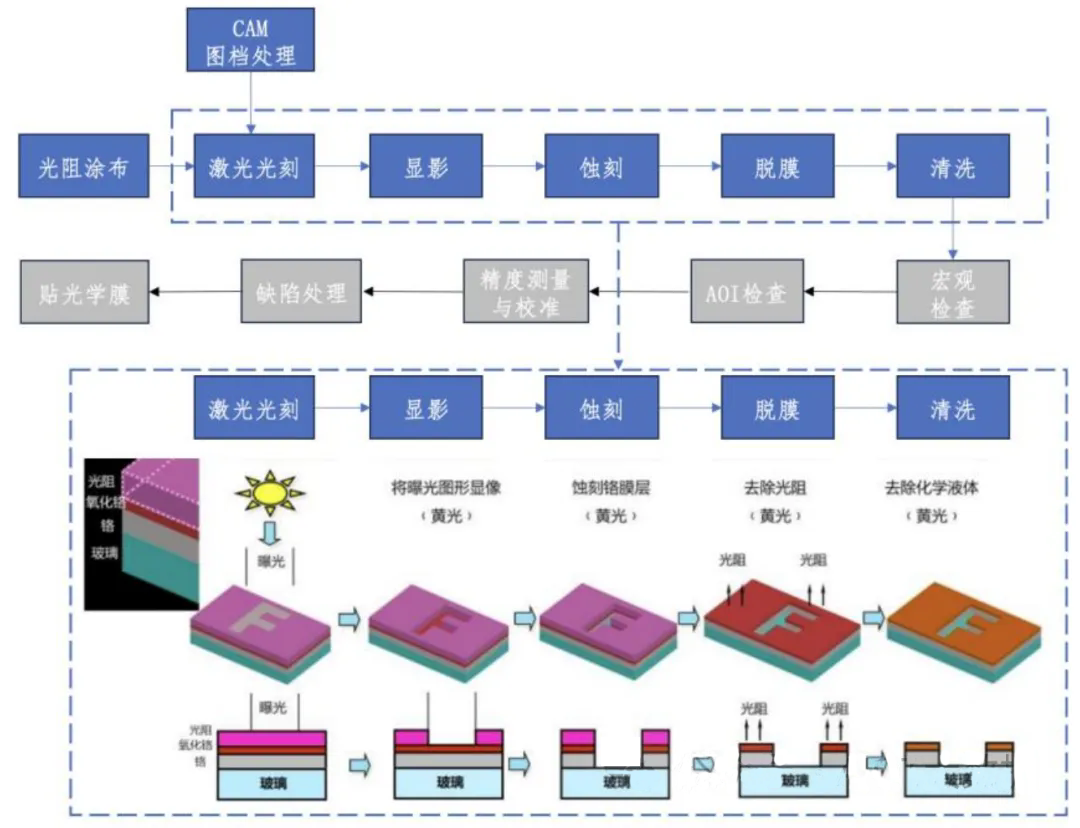

设计与准备:首先需要根据电路设计制作出掩模的版图。这个过程通常使用计算机辅助设计(CAD)软件来实现。设计好后,会生成一个掩模图案的数据文件。

选择基板:选择适当的基板材料是制作光刻掩模的重要环节。常用的基板材料是石英或玻璃。基板应该具有高透明度、低膨胀系数、高抗拉强度等特性。

清洗基板:在制作掩模之前,需要对基板进行清洗。这一步可以通过使用溶剂、酸、超声波或喷射清洗等方法来去除表面的尘埃和杂质。

涂覆光刻胶:在清洗干净的基板上涂覆一层光刻胶。光刻胶是一种光敏材料,可以通过光的照射发生化学变化,从而形成所需的图案。

曝光:将掩模图案数据文件导入曝光设备,如电子束曝光机。设备会将图案转换为光或电子束信号,然后逐点扫描光刻胶表面。在曝光过程中,光刻胶中的光敏分子会因为光或电子束的照射而发生变化。

显影:曝光后,需要将基板放入显影液中以去除光刻胶中未发生变化的部分。经过显影处理后,基板上将形成与掩模图案相符的光刻胶图案。

刻蚀:使用刻蚀工艺(如湿刻蚀或干刻蚀)去除基板上未被光刻胶覆盖的部分。这样,基板上就形成了与掩模图案相符的凹槽。

去除光刻胶:使用溶剂或其他方法去除基板上剩余的光刻胶,暴露出刻蚀后的凹槽图案。

检验与修复:对完成的掩模进行检查,确保其图案与设计一致且没有缺陷。如有缺陷,可以使用修复工艺进行修复

mask set

一个典型的集成电路制造过程可能包括多达数十个不同的掩模,这些掩模分别对应于不同的制程步骤,如活性区域、接触孔、金属互联线、绝缘层等。每个掩模都包含一个特定层次的图案信息,用于将该层次的图案转移到硅片上。

在制造过程中,各个掩模按照特定的顺序依次使用,以逐层构建集成电路的结构。由于每个掩模都有特定的作用,因此mask set中的所有掩模必须精确匹配,以确保最终产生的集成电路符合设计规范。

换句话说,根据单个设备的不同,每台***可能需要 5 到 40 个(或更多)单独的光掩膜版,称为“掩模组” 。复杂的产品需要更多的掩膜版。一个 10nm 的光学掩模可能需要 76 个单独的掩膜版,而 28nm 节点掩膜版大约需要 46 个。

掩膜版原理

目前的光学光刻系统结合了具有不同波长的光源。当今最常见的光刻系统使用 248nm 和 193nm 波长的光源。

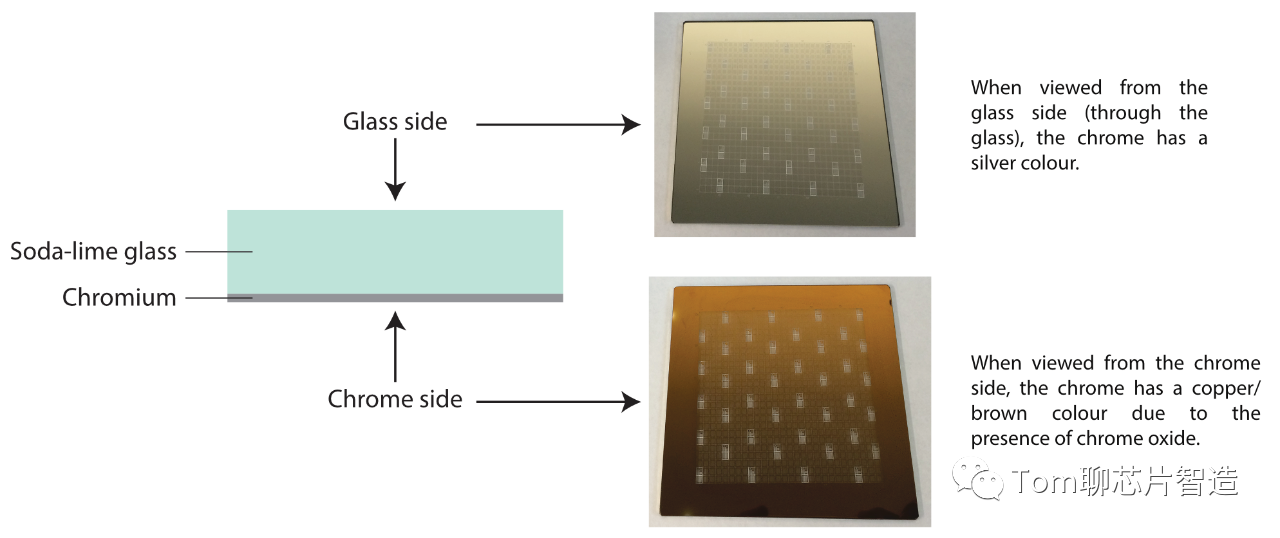

在光刻中,掩膜版由玻璃基板上的不透明铬层组成。光掩膜版制造商在选定的位置蚀刻铬,从而露出玻璃基板。其他地方没有蚀刻铬材料。在操作中,光线照射掩模并穿过玻璃区域,从而使晶圆曝光。由于铬对光线的阻挡作用,光不会穿过镀铬的区域。

EUV 掩模

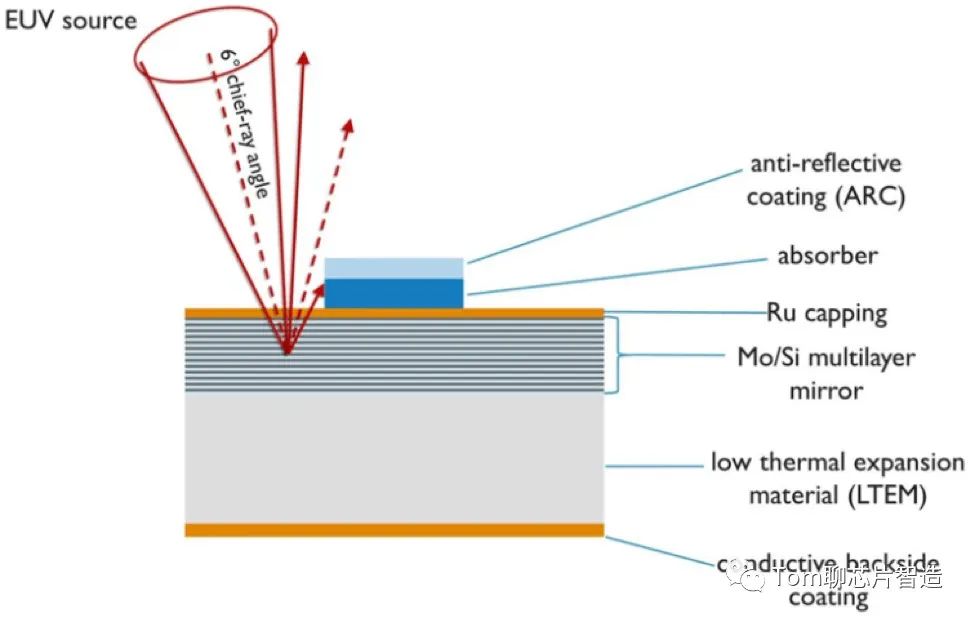

使用 13.5 纳米波长,极紫外 (EUV) 光刻是下一代技术,可在晶圆上图案化微小特征。

EUV 掩膜版不同于光学掩膜版。与普通的光学掩膜版不同, EUV 掩膜版反射 13.5 纳米波长的光。EUV 掩模版由衬底上的 40 到 50 层交替的硅和钼层组成,形成 250 纳米到 350 纳米厚的多层堆叠。钌金属层沉积在多层堆叠上,随后是钽吸收层。

审核编辑:汤梓红

-

集成电路

+关注

关注

5388文章

11563浏览量

362089 -

半导体

+关注

关注

334文章

27442浏览量

219465 -

晶圆

+关注

关注

52文章

4922浏览量

128066 -

IC设计

+关注

关注

38文章

1297浏览量

104037 -

工艺流程

+关注

关注

7文章

106浏览量

16293

原文标题:光刻掩膜版怎么制作的?

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

国内首条G11掩膜板项目开工 成都或成我国最大掩膜版制造基地

掩膜版用在哪里?怎样制作掩膜版?

掩膜版用在哪里?怎样制作掩膜版?

评论