AWorksLP 对外设进行了高度抽象化,为同一类外设提供了相同的接口,应用程序可以轻松跨平台。本文以MR6750平台为例,介绍AWorksLP 双核调试的基本用法。

简介MR6750 双核是集成了两个RISC-V处理器,是两个完全独立的CPU,故HPM双核工程是Core0工程和Core1工程两个独立的工程。因此HPM双核工程编译,其实是两个独立的单核工程的编译。用户只需要建立core0和core1的各自工程编译调试即可。 多核调试

多核调试

1. 修改默认工程配置

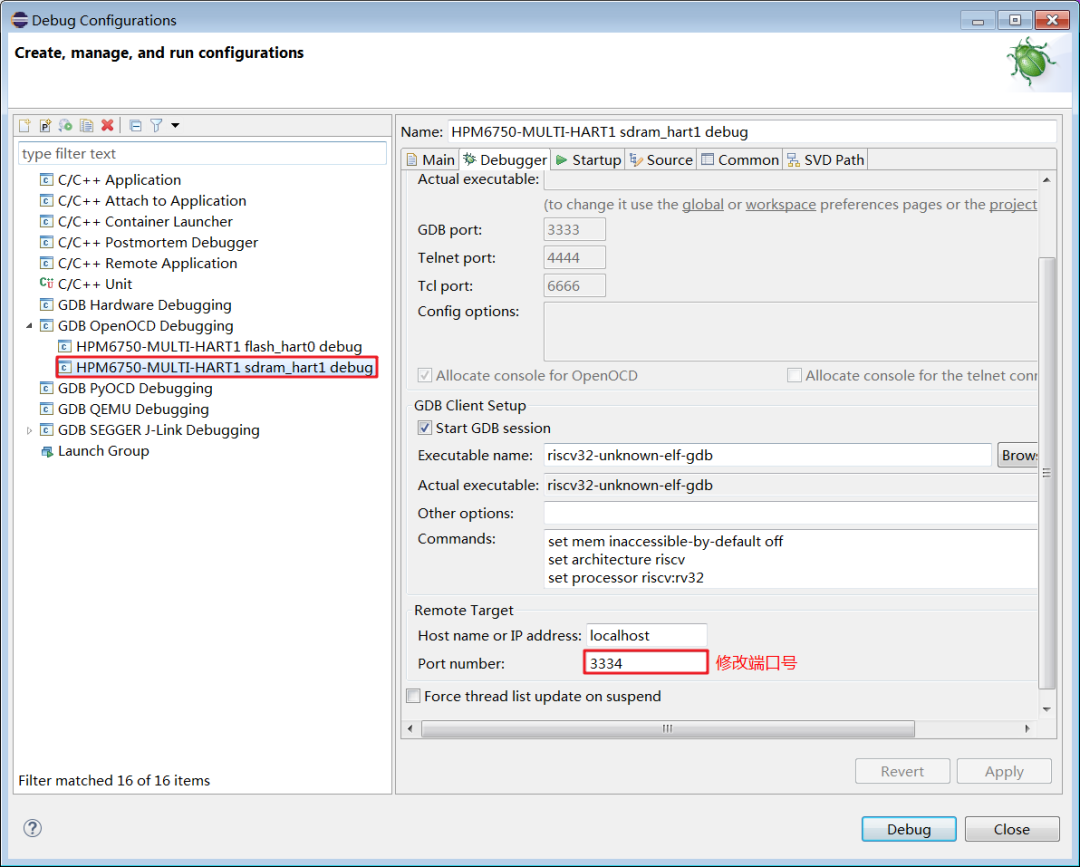

修改hart1工程OpenOCD的调试配置中的端口号。

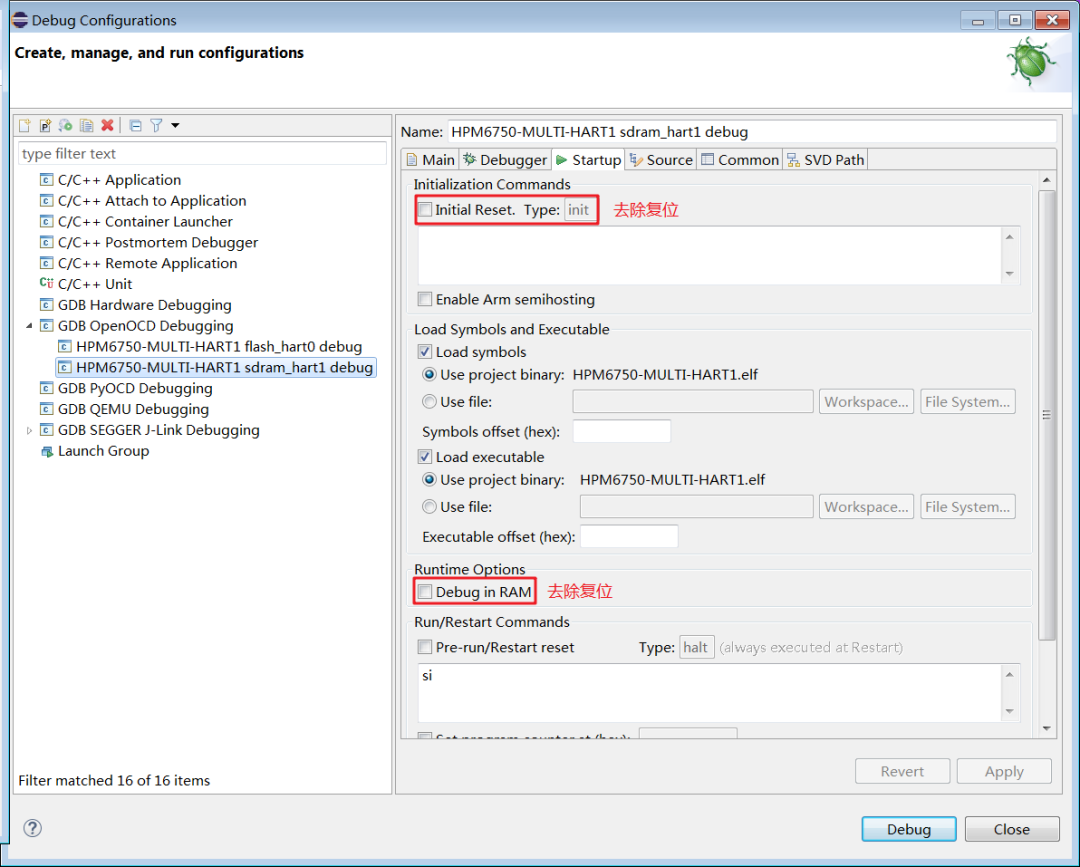

图1修改端口号在Startup配置栏中去除复位选项。

图2去除复位选项2. OpenOCD调试

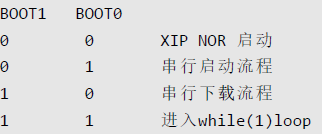

在多核调试前建议将启动方式设置为串行启动流程或者串行下载流程。

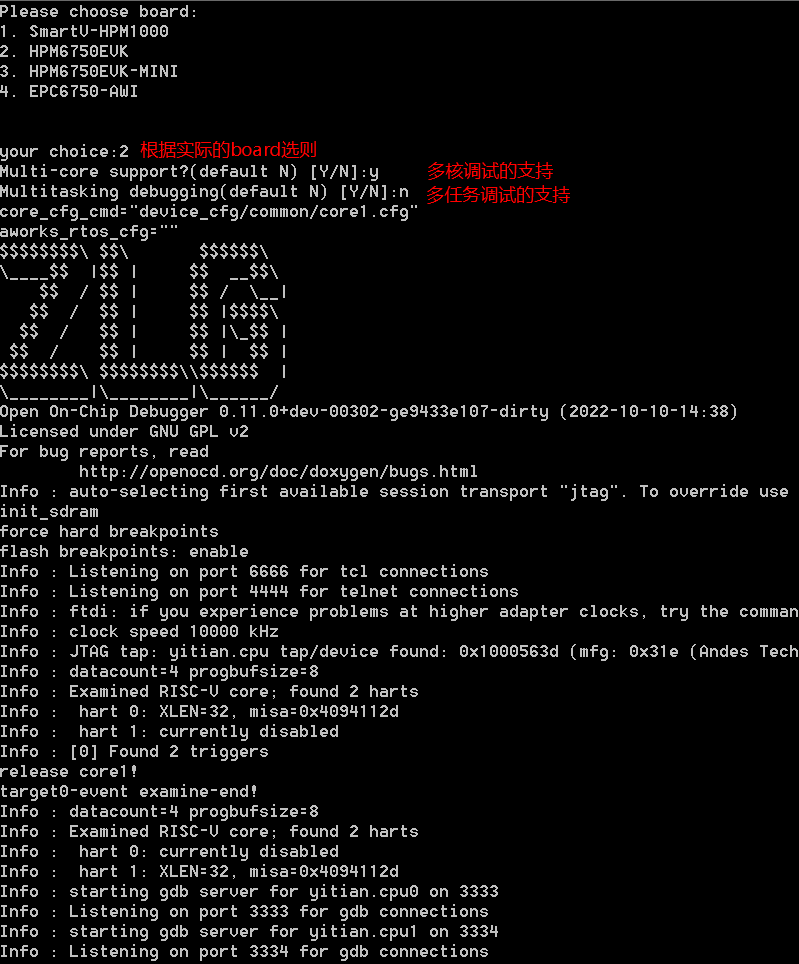

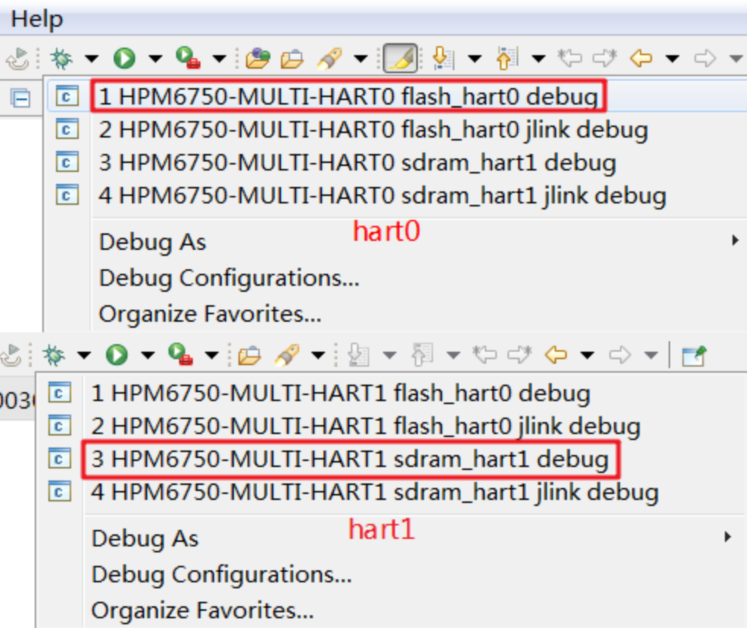

图3启动方式多核调试下会分配两个gdb 端口,分别是3333 与3334 分别对应hart0与hart1 ,端口配置参考4.1小节。

图3启动方式多核调试下会分配两个gdb 端口,分别是3333 与3334 分别对应hart0与hart1 ,端口配置参考4.1小节。 图4 OpenOCD调试

图4 OpenOCD调试

先下载hart0的固件,再下载hart1 的固件。注意顺序不能错。

注: 在调试状态下,hart0 不会将hart1 的固件加载到相应的内存上,所以这里需要分别下载。

图5OpenOCD下载

图5OpenOCD下载

-

处理器

+关注

关注

68文章

19265浏览量

229684 -

cpu

+关注

关注

68文章

10855浏览量

211610 -

调试

+关注

关注

7文章

578浏览量

33924 -

编译

+关注

关注

0文章

657浏览量

32859

发布评论请先 登录

相关推荐

全志T113双核异构处理器的使用基于Tina Linux5.0——异构双核通信验证

在FPGA里面例化了8个jesd204B的ip核同步接收8块AFE芯片的信号,怎么连接设备时钟和sysref到AFE和FPGA?

HPM6750 Bootloader设计

双核cpu和单核cpu的区别

双核dsp和单核dsp的区别

MCUXpresso IDE下在线联合调试双核MCU工程的三种方法

AWorksLP 样例详解(MR6750)——双核调试

AWorksLP 样例详解(MR6750)——双核调试

评论