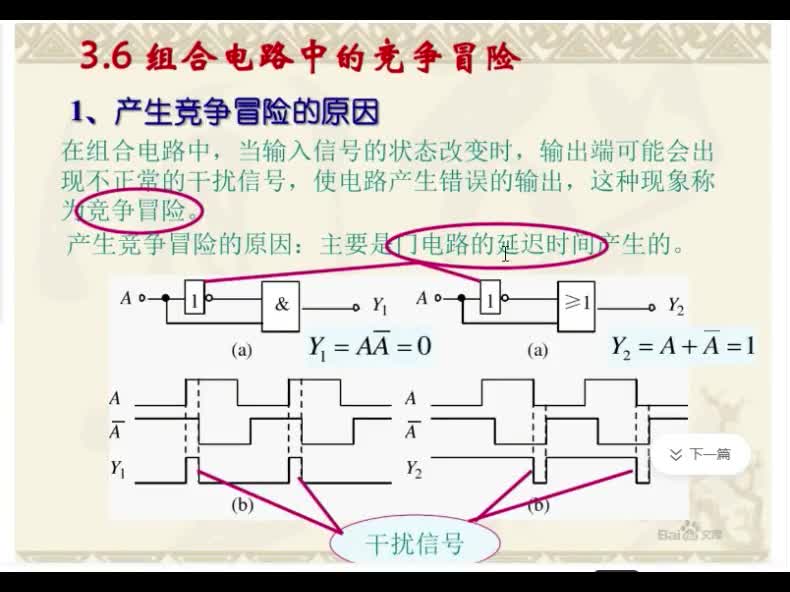

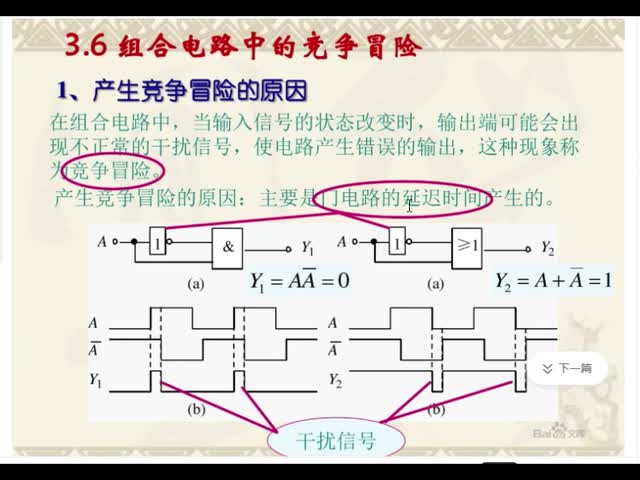

门电路的两个输入信号同时向相反的逻辑电平跳变的现象叫做 竞争 ,这种竞争可能在电路的输出端产生尖峰脉冲,这种现象称为 竞争冒险 。

竞争冒险产生的根本原因是输入信号通过两条或两条以上的路径传输到输出端,每条路径的延时不同,从而导致信号不能同时到达输出端。接下来,我们就通过几个简单的电路了解一下竞争冒险现象。

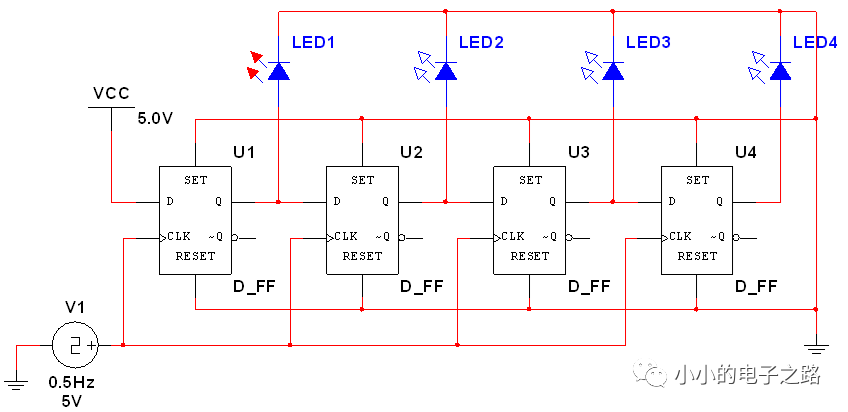

1、移位寄存器

首先来看下面一个电路,这个电路简单描述了移位寄存器的工作原理,当时钟上升沿来临的时候,数据会整体向右移动一位。但是现在的问题是:每次时钟有效时,为什么数据只移动一位?

要想解释上面的问题,就需要具体了解一下构成移位寄存器的最小单元—D触发器的行为。下图是一个D触发器的原理图,当有效时钟边沿到来时,其输入端D的值会存入输出端Q。

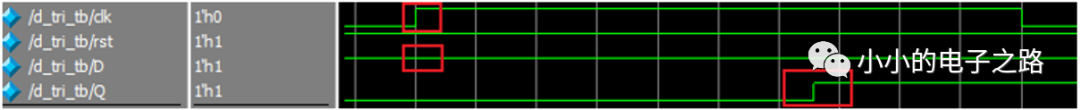

对上述D触发器进行功能仿真,仿真结果如下图所示,可以看出,当时钟上升沿到来时,触发器的输出Q会等于输入D。

接下来,对D触发器进行更接近真实情况的门级仿真,通过仿真结果可以看到,当时钟上升沿到来时,触发器的输出并没有立马发生变化,而是等待一段时间之后其输出Q才会与输入D相等。

这一段延时称为触发器的 Tco时间,即输出延时,指从触发器有效边沿到来到触发器输出有效的时间差 。这也是移位寄存器每次只能移动一位的原因。

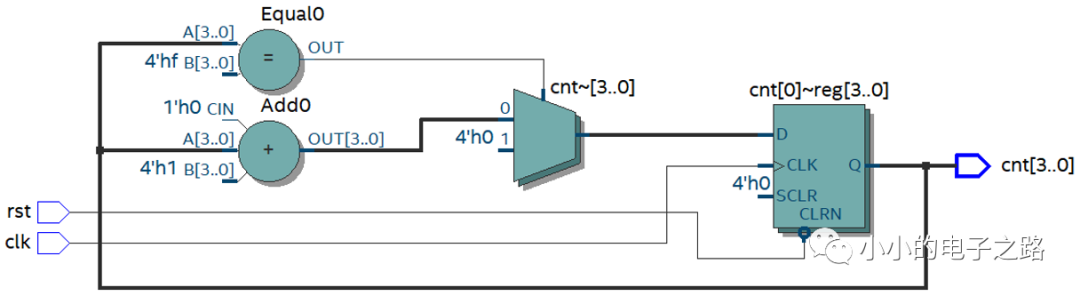

2、计数器

接下来再看另一个电路—计数器电路,该电路由多个逻辑门组合而成,可以实现十六进制计数功能。

对该电路进行功能仿真,可以看出电路功能正常。

同样,对电路进行门级仿真,结果如下,将仿真图放大可以发现,在计数值由0001变为0010的过程中,出现了短暂的0011的计数值。

之所以出现0011这样的计数值,是因为每一位分别由多个不同的逻辑门电路控制,因此,每一位的变化存在一定的延时,这一延时称为 Tpd时间,即传输延时,指****从输入信号有效到输出信号稳定时的时间差 。

但是,不同位的控制电路的延时是不同的,以上面的现象为例,该计数器第三位的控制电路的延时要比第四位短,因此,第三位先变为1,第四位后变为0,两个变化之间的延时差就导致出现了0011这样的现象,这就是竞争冒险现象。

以当前的时钟频率,上面的现象是不会导致系统出现问题的,因为不稳定状态持续的时间非常短,不会被时钟采样到,但是,如果时钟频率太高,该状态就有可能被采样到,导致系统出错,这就是某些代码运行时时钟频率不能太高的原因之一。

以上就是本次分享的全部内容,谢谢大家!

-

寄存器

+关注

关注

31文章

5336浏览量

120230 -

仿真

+关注

关注

50文章

4070浏览量

133552 -

门电路

+关注

关注

7文章

199浏览量

40160 -

数字电路

+关注

关注

193文章

1605浏览量

80578 -

输入信号

+关注

关注

0文章

455浏览量

12547

发布评论请先 登录

相关推荐

FPGA设计中竞争冒险问题的研究

请教一个与数字电路有关比较简单的问题,希望大神可以给个详细的答案

FPGA中的竞争和冒险现象

什么是竞争与冒险现象?怎样判断?如何消除?

简谈FPGA的竞争冒险和毛刺问题

FPGA | 竞争冒险和毛刺问题

FPGA中的冒险现象和如何处理毛刺

数字电路中的竞争冒险现象

数字电路中的竞争冒险现象

评论