主要介绍几种逻辑电路的高速特性包括 ITL 逻辑电路、 CMOS 逻辑电路、 ECL 逻辑电0路,和 LVDS 器件的基本结构、 工作原理和特点,以及逻辑门电路的使用规则 。

1 高速TTL电路

由于TTL电路的基本组成单元为三极管,先复习下三极管的一些知识。

1.1 三极管的动态开关特性

晶体三极管在饱和与截止两种状态转换过程中具有的特性称为三极管的 开关特性 。三极管的内部也存在着电荷的建立与消失过程。

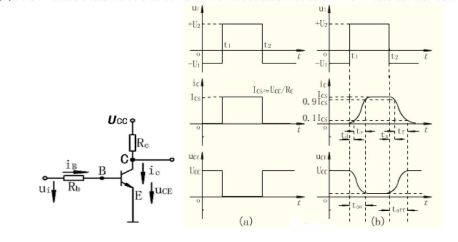

饱和与截止两种状态的转换也需要一定的时间才能完成。假如下图所示电路的输入端输入一个理想的矩形波电压,在想情况下, iC 和 UCE 的波形应该如图 (a)所示 。

但实际转换过程中 iC 和 UCE 的波形如图(b)所示 , 无论从截止转向导通还是从导通转向截止都存在一个逐渐变化的过程。

开通时间: 三极管从截止状态到饱和状态所需要的时间。

三极管处于截止状态时,发射结反偏,空间电荷区比较宽。当输入信号Ui 由-U1 跳变到+U2时,由于发射结空间电荷区仍保持在截止时的宽度,故发射区的电子不能立即穿过发射结到达基区 。这时发射区的电子进入空间电荷区,使空间电荷区变窄,然后发射区开始向基区发射电子,晶体管开始导通。这个过程所需要的时间称为延迟时间句。

经过延迟时间 tct 后,发射区不断向基区注入电子,电子在基区积累,并向集电区扩散,形成集电极电流 ic。随着基区电子浓度的增加,ic 不断增大 。ic 上升到最大值的 90%所需要的时间称为上升时间 tr。则开通时间为 ton=td+tr, 开通时间的长短取决于晶体管的结构和电路工作条件 。

关闭时间: 三极管从饱和状态到截止状态所需要的时间。

进入饱和状态后,集电极收集电子的能力减弱,过剩的电子在基区不断积累起来,称为量存储电荷,当输入电压 ui 由+U2 跳变到-U1 时,存储电荷不能立即消失,而是在反向电压用下产生漂移运动,使集电极电流维持 lcs 不变,直至存储电荷全部消散,晶体管才开始退出饱和状态,ic 开始下降。

在反向的基极电压的作用下,集电极电流 iC 不断减小,并逐渐近于零。集电极电流由 0.9Ics 降至0.1Ics 所需的时间称为下降时间tf。则关闭时间为 toff=ts+tf。 关闭时间的长短取决于三极管的结构和运用情况。ton和toff的大小反映了三极管由截止到饱和与从饱和到截止的开关速度,它们是影响电路工作速度的主要因素。

2 TTL基本电路的工作原理

2.1 TTL的反相器结构域工作原理

反相器TTL典型的电路如下图:由三部分组成,T1 、R1 和 D1组成的输入, T2、R2 和 R3组成的倒相级,T4、T5、D2和R4组成的输出级 。

工作原理:

输入信号 A 的高、低电平分别为:VIH=3.4V , VIL=0.2V 且 Vbc=0.7V, Ec=+5V。

(1) 输入信号 A 为低电平 VIL=0.2V

T1 的发射结导通 ,并将 T 1 的基极电位钳在 VIL+Vbe1=0.9V,因为T1的集电极回路电阻为R2和T2的b-c结反向电阻之和,阻值非常大,所以 T1 工作在深度饱和区,Vces1≈0, Vc1=VIL+Vces1=0.2V 。

显然,T2 的发射结不导通,T2 截止,Vc2 为高电平,Ve2 为低电平,使 T5截止,故 R2上的压降很小,Vc2≈Ec,T4 管导通。因此,输出为高电平 VoH=Ec-Vbe4-VD2=3 .6V。

(2)输入信号 A 为 高电平 VIH=3 .6V

T1导通时其基极电压 Vb1=VIH+0.7=4.3V,集电极电压大于发射极电压,使T1和T5管饱和导通,Vo=VoL=Vces5=0.3V,Vc2=Vces2+Vbe5=0.3+0.7=1V,则 T4和 D2 管截止。

综上所述, TTL 反相器输入端输入低电平,输出即为高电平:当输入端输入高电平时,输出为低电平,实现了非逻辑功能也称为非门 。

2.2 肖特基 TTL C STTL) 结构及原理

BJT工作在饱和状态时,发射结和集电结都处于正向偏置,集电结正向偏置电压越大,表明饱和程度越深。为了限制 BJT 的饱和深度,在 BJT 的基极和集电极上并联一个导通阈值电压较低的肖特基二极管,如下图所示。

当没有 SBD 时, 随着基极电压的升高,电流直接沿着基极和集电极方向流动 。由于 SBD作用 ,当基极电压大于 0.4V 时, SBD 首先电导通, 电流沿着 SBD 方向流动, 从而使 T 的基极电流不会过大(而且 T 的集电结正 向偏压将被钳制在 0.4V 左右) , 因SBD 起到抵抗过饱和的作用,因而又将这种电路称为抗饱和电路,使电路的开关时间大为缩短。

-

三极管

+关注

关注

145文章

3726浏览量

128503 -

反相器

+关注

关注

6文章

332浏览量

45330 -

信号完整性

+关注

关注

68文章

1496浏览量

98235 -

CMOS电路

+关注

关注

0文章

50浏览量

12099 -

高速逻辑电路

+关注

关注

0文章

4浏览量

5783

发布评论请先 登录

信号完整性学习笔记之高速逻辑电路介绍

信号完整性学习笔记之高速逻辑电路介绍

评论