高速数字信号的反射是影响现代数字电路设计的重要因素之一 严重的反射将破坏信号完整性,并引起过冲现象,从而出现错误的数字逻辑和毁坏器件。 该文详细分析了信号反射产生机理和现象,并给出了反射解决的方案 。

1 信号反射现象

1.1 反射基本概念

反射就是在传输线上的回波。如果一传输线电尺寸满足长线时,且没有被合理的端接(终端匹配),那么来自于驱动端的信号脉冲在接收端被反射,从而引发不预期效应,使信号轮廓失真。反射是传输线的基本效应,即当信号沿着传输线前行时 , 碰到阻抗不连续时会发生反射:

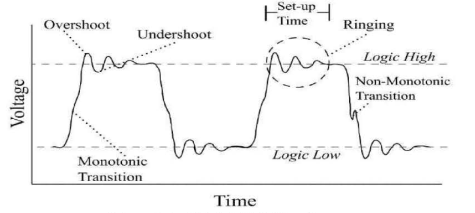

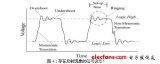

1)当信号在传输时碰到比目前阻抗高时,会发生正向反射,使信号边沿的幅度增加,信号边沿出现过冲 。从定义上来说,过冲就是指接收信号的第一个峰值或谷值超过设定电压----对于上升沿是指第一个峰值超过最高电压;对于下降沿是指第一个谷值超过最低电压。

2)当信号在传输时碰到比目前阻抗低时,会发生负向反射,使信号边沿的幅度减小,信号边沿出现台阶,即欠冲 。严重时将可能产生假时钟信号,导致系统的误读写操作。

如果在一个时钟周期中,反复的出现过冲和欠冲,我们就称之为振荡,也叫 振铃 。振荡是路中因为反射而产生的多余能量无法被及时吸收的结果。下图所示的波形就是一个明显在过冲,欠冲 , 振荡的例子 。

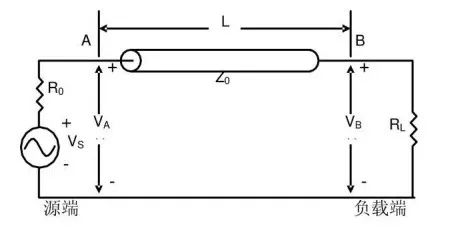

在PCB设计中,反射通常由连线阻抗的不匹配造成,如不同布线层阻抗不一样 、 T 型接、过孔、线宽的变化、器件的输入输出阻抗,封装寄生参数等等。 下图所示的理想传输线模型来分析与信号反射有关的重要参数。

理想传输线 内阻为R0的数字信号驱动源Vs 驱动,传输线的特性阻抗为 Z0,负载阻抗 RL。理想的情况是当R0= Z0= RL 时,传输线的阻抗是连续的,不会发生任何反射,但能量半消耗在源内阻 R0上, 另一半消耗在负载电阻 R1上(传输线无直流损耗,即无耗传输线)。

如果负载阻抗大于传输线的特性阻抗 Z0欠阻尼 。

如果负载阻抗小于传输线的特性阻抗,即 Z0>RL,负载试图消耗比当前源端提供的能量更多的能量,称为 过阻尼 。欠阻尼和过阻尼都会产反向传播的波形,某些情况下在传输线上会形成驻波 。

当 Z0=RL 时,负载完全吸收到达的能量,没有任何信号反射回源端,称为临界阻尼 。从系统设计的角度来看,由于临界阻尼情况很难满足,所以最可靠的方式轻微的过阻尼,因为这种情况没有能量反射回源端 。

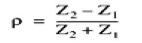

负载端阻抗与传输线阻抗不匹配会在负载端(B点)反射一部分信号回源端( A 点),反射电压信号的幅值由负载反射系数定,见下式:

如果传输线由两段不同特性阻抗的传输线组成,则连接点处也会产生信号的反射。传输线上出现的分叉点就是这样一个阻抗不连续点(断点)。

** 反射信号产生的主要原因:过长的走线;未被匹配终结的传输线,过量电容或电感以及阻抗失配。**

当信号在线终端处的阻抗不连续点被反射时,信号的一部分将反射回源头。当反射信号达源头时,若源头端阻抗不等于传输线阻抗就将产生二次反射 。因此若传输线的两端都存在阻抗不连续,信号将在驱动线路和接收线路之间来回反射 。信号的反射波因传输线的损耗将最后达到直流稳态 。

2 产生反射现象的因素

产生反射现象的因素有信号上升沿时间、传输线的端接、短分支节线、容性分支节线、拐角和通孔、载重线、电感性间断线等。

2.1 上升时间对反射的影响

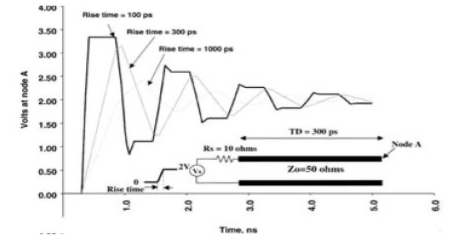

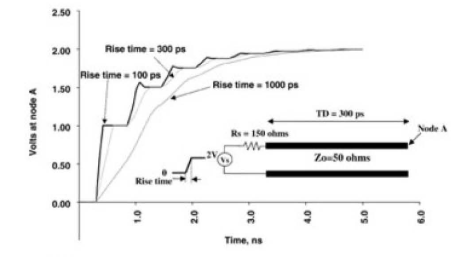

当上升时间变得大于传输线延迟(TD)的两倍时,传输线为短线,上升时间对波的形状会存在影响 。因为信号到达负载端时,产生了反射,反射信号回到源端,但此时源端的信号正处于上升阶段,这样的反射会在信号缓慢的上升过程中被吸收掉,从而不会影响信号电平的幅值。

但如果当上升时间小于TD的两倍时,上升时间开始对波的形状就会产生重要影响 。下两图分别显示了欠载和过载传输线上不同上升沿时间的影响 。

2.2 串联传输线的反射影响

电路板上走线的宽度必须被压缩,因为它可能经过通孔或在板密集区域的周围布线 。如果走线的线宽有一小段发生变化,特性阻抗就会改变 ,通常是增加 。

有三个特征会决定短的传输线片断的影响:不连续性的时延(TD),不连续性的特性阻抗(Z0),信号的上升时间 (RT) 。当时延与上升时间相比很长时,反射系数将饱和。发射系数最大值与不连续性的反射有关 :

阻抗的不连续会导致信号的振荡,因此设计互连线时必须具有均匀的特性阻抗。为了保证反射噪声小于信号摆幅的5%,要求特性阻抗的变化要小于10%,这就是为什么电路板上对阻抗的控制在±10%。

2.3 短分支传输线的反射影响

分析短线的影响是比较复杂的,因为要考虑很多反射的问题。当信号离开驱动端,首先会遇到分支点 。这里我们会看到两段传输线并联产生一个低的阻抗,则一个负反射将会返回到源端 。两个重要的因素可决定分支对信号完整性的影响 , 即信号的上升时间和分支的长度。

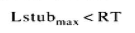

根据经验规则,分支的长度保持小于上升时间延展的20%,则分支的影响就不重要 。反之对信号就会产生影响。经验规则用式子来表示:

其中 Lstubmax 为可接受的分支长度的最大值,单位为 inch; RT 为信号的上升时间,单位为s;例如,对于1ns 的的上升时间,应保持分支长度小于 1inch。很明显 , 当上升时间变短时,将分支长度减小,使其不影响到信号的完整性,就变得越来越困。

-

电感器

+关注

关注

20文章

2329浏览量

70507 -

振荡器

+关注

关注

28文章

3832浏览量

139035 -

PCB设计

+关注

关注

394文章

4683浏览量

85547 -

信号完整性

+关注

关注

68文章

1404浏览量

95458 -

单端信号驱动

+关注

关注

0文章

2浏览量

1138

发布评论请先 登录

相关推荐

DVI接口详细分析

详细分析stm32f10x.h

详细分析了VTIM和VMIN的功能

高速电路信号完整性分析与设计(四)

详细分析信号反射产生的机理和现象

详细分析信号反射产生的机理和现象

评论