1 容性分支在传输线中间引起的反射影响

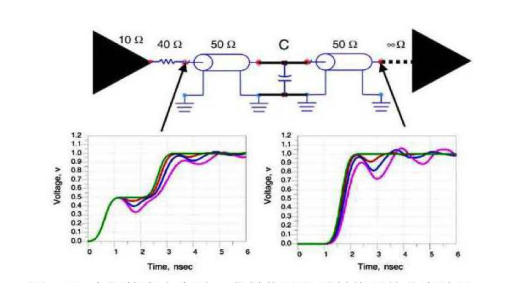

附着在走线中间的测试点 , 通孔, 封装引线,甚至一小段分支,作用就像一个集总电容 。下图所示就是一个电容加在走线中间时,发射电压和反射电压的仿真结果。

图为电容最初的阻抗较低,反射回源端的信号将有轻微的负极性偏向。下图所示的情况是上升时间为 0.5ns,容分别为 0,2, 5, 10pF 的情况 。

发射信号最初不会受到影响,但是当它从走线末端返回到源端时,就会受到影响 。返问信号再次遇到电容, 其中一些信号将带有负号,反射回远端 。这些反射回到接收端就为负电压,使接收到的信号下降,导致下冲。

输线中间理想电容的影响依赖于信号的上升时间和电容的大小。电容越大,阻抗越小 ,会产生更大的负极性反射电压,导致接收端出现更大的下冲。

在时域内,电容的阻抗为:

如果信号是线性倾斜的,带有上升时间为 RT, dV/dt 变为 V/RT,电容的阻抗为:

在上升时间的时间间隔内,信号线与返回路径间的电容是分流阻抗 Zcap, 跨越传输线的分流阻抗会导致反射。如下图所示。为了使该阻抗的存在不产生严重问题, 希望这个阻抗比传输线的阻抗大的多,即希望 Zcap>>Z0 作为起始位置,Zcap>5*Z0则电容和上升时间约束条件为 :

Cmax =反射噪声可能成问题之前,可接受的电容的最大值,单位为 nF。

2 短分支传输线的反射影响

分析短线的影响是比较复杂的,因为要考虑很多反射的问题。当信号离开驱动端,首先会遇到分支点 。这里我们会看到两段传输线并联产生一个低的阻抗,则一个负反射将会返回到源端 。两个重要的因素可决定分支对信号完整性的影响,即信号的上升时间和分支的长度。

设分支位于传输线的中间,并且与传输线有相同的阻抗 。下图所示了在分支长度从上时间的 20 %增加到 60% 时,对发射信号和反射信号仿真的结果 。

根据经验规则, 分支的长度保持小于上升时间延展的 20%,则分支的影响就不重要。反之对信号就会产生影响。经验规则用式子来表示:

其中 Lstubmax 为可接受的分支长度的最大值,单位为 inch; RT 为信号的上升时间,单位为s;

例如,对于1ns 的上升时间,应保持分支长度小于 1inch。很明显 , 当上升时间变短时,将分支长度减小,使其不影响到信号的完整性,就变得越来越困。

3 拐角和通孔的影响

当信号沿着均匀的互连线传输时,发射信号不存在反射及失真。如果均匀互连线存在 90的弯曲,就有阻抗的改变,则发生反射及信号的失真。90度的拐角导致了均匀互连线阻抗的不连续性,影响了信号的完整性。

下图所示是对上升时间为50psec 的信号所作的 TDR响应,附近有2个90 度的拐角,阻抗不连续性而导致反射,线宽为 65mil,阻抗为50欧姆。

将 90 度的拐角转换为 45 度的弯曲将会减小这种影响,如果改用常宽的圆弧状弯曲,影会进一步减小。

拐角对信号传输线的唯一影响是由于走线弯曲处的额外宽度 。这个额外的线宽作用就像个容性的不连续性。这个容性的不连续性导致了信号的反射和时延 。

如果走线的弯曲处是常宽的,走线宽度没有改变,信号在拐弯的每一点遇到的阻抗都是

相同的, 那么就不会有反射。下图表明了拐角代表了正方形的一部分,粗略的估计,有正方形的一半。

拐角的电容可从正方形的电容以及走线单位长度的电容来估算:

走线单位长度的电容与走线的特性阻抗有关:

对拐角电容的估计为:

我们可以把这个估算概括成为一个方便记忆的经验规则,在 50 欧姆的传输线中,拐角所带来的相关电容为2 ×线宽 。线宽单位为 mil,电容单位为 fF。

若仍然保持 50 欧姆的阻抗,而线宽变窄,则拐角所带来的电容将变小,影响就不明显 。对于高密度电路板上的标准信号线, 5mils的线宽,管脚的电容为 10fF。

10fF的电容所带来的反射噪声信号的上升时间,根据公式

上升时间为 0.010pF/4~3ps.

10fF的电容所带来的信号的时延,根据公式

时延为 0. 5× 50× 0.01pF=0.25ps 。

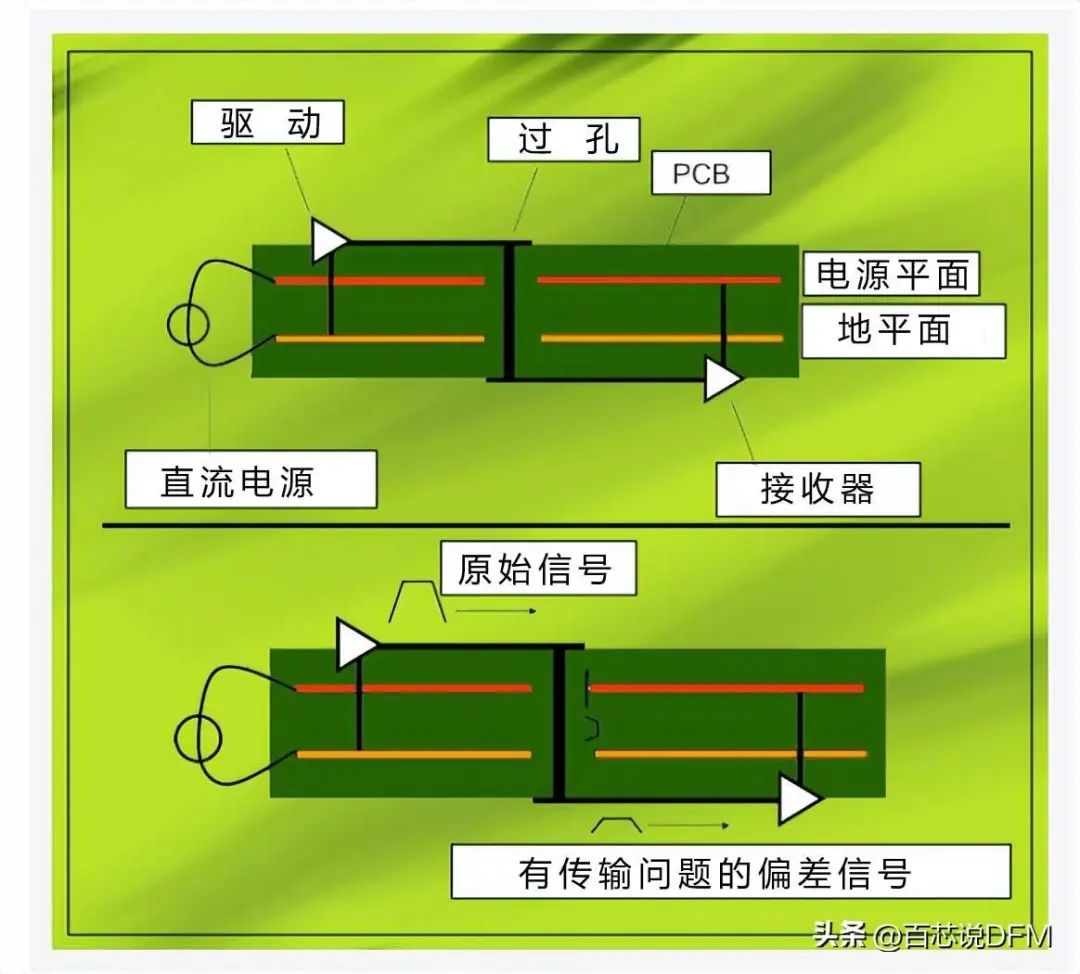

如果用通孔来连接一根信号线与测试点,或是与相邻板层的另一根信号线相连,通孔会对于电路板的不同层具有过多的电容。这时,通孔可看作是一个集总的电容负载 。

通孔的电容大小依赖于孔的大小,隔离孔,板的表层及底层焊点的大小 。它的大小可从 0. 1pF 到超过1pF 的范围 。信号线上的任一通孔都可看作是容性的不连续性,在高速互连中,是影响信号完整性的主要因素 。

4 载重线的反射影响

当传输线上有一个容性负载时,信号会发生失真,并且上升时间下降。如果有多个负载布在传输线上,如果间隔与信号上升时间的空间延展相比要短,则从每个电容性不连续的反射会消除 。带有均匀间隔分布的容性负载的传输线叫做载重线 。

每个不连续段都可看作是较低阻抗的区域。如果上升时间与电容间的时延相 比要短时,每个间断的作用对信号来讲就像离散的不连续性 。如果上升时间与电容间的时延相比要长,低阻抗区域叠加, 整个线的平均阻抗更低。

对于三个不同的上升时间,载重线的反射信号如图示。在该例中,5个3pF的电容每隔1inch 分布在50欧姆的传输线上,走线的最后10inch没有负载。

对于开始的几个电容,可看到明显的不连续性,但是后几个的电容带来的不连续性被消 。当上升时间与电容间时延相比要长时,均匀分布的容性负载产生的效果,即走线的表面来的特性阻抗降低。在这种负载线中,单位长度的阻抗增加意味着特性阻抗更低,时延更。

在均匀的,未加电容负载的传输线中,特性阻抗和时延与单位长度的电容和电感有关:

如果有均匀分布的电容负载,每个负载为 C1间隔为d1, 走线上单位长度分布的电容从C0L增加到(C0L+C1/d1).特性阻抗和响应的时延为:

可见,当增加分布的电容负载时,走线的特性阻抗降低,则端接电阻也应降低 。

-

电容器

+关注

关注

64文章

6263浏览量

100372 -

信号完整性

+关注

关注

68文章

1417浏览量

95683 -

TDR

+关注

关注

1文章

69浏览量

20003

发布评论请先 登录

相关推荐

信号完整性(五):信号反射

信号完整性简介及protel信号完整性设计指南

信号完整性与电源完整性分析 第三版 pdf_反射、串扰、抖动后,我的信号变成什么鬼?...

信号完整性的反射因素详解

信号完整性的反射因素详解

评论