开发目的

FPGA项目开发的过程中,需要完成设计代码开发、验证环境搭建、仿真分析、板级验证等操作,在这个过程中,许多操作虽然必不可少但是步骤是重复的。辅助软件通过预先定义的处理模式,对一些重复性复杂操作通过Python辅助软件使操作简化以提高项目开发效率。独立仿真可以不依赖Vivado,简化仿真步骤,但建立独立仿真往往需要复杂繁琐的步骤,所以简化建立独立仿真的步骤很有必要。

重要的是,有了脱离Vivado建的第三方仿真工具单独的环境,为FPGA工程后续ASIC化提前搭建好仿真环境,只把用到的库和相关文件从Vivado库里抽取出来,同时,每次仿真时不用启动非常占资源的Vivado软件,直接运行仿真脚本即可。同时,软件生成的仿真环境后也可以手动进行优化调整,按照用户自己熟悉的仿真习惯进行定制化修改。

功能描述

该软件用于提升FPGA仿真效率,节省仿真时间和步骤。本软件可以建立独立仿真,生成Questasim、modesim或VCS环境下的独立仿真,可视化界面,更加方便用户操作。

RTL设计完后会进行仿真Vivado内自带仿真器,或者可以通过Vivado启动第三方仿真工具联合仿真。但是在实际项目开发过程中,当我们修改代码后,需要关闭仿真软件并重启仿真,之前加载的波形信号也需要重新加载。因而很多时候,我们希望脱离Vivado,利用Modelsim或者VCS等第三方仿真工具,提高仿真效率;在这个过程中,通过提取工程中的代码文件和IP核信息文件,缩减工程所占用的内存空间,方便项目开发人员同步及备份。该软件建立独立仿真首先会提取源仿真工具、目的仿真工具,了解要建立哪种环境下的独立仿真。

还要提取自动化仿真文件名和创建独立仿真的路径,用于建立独立仿真文件夹,该文件夹有rtl和sim两个文件夹,仿真用到的文件都会放到该文件夹里面。然后会提取tb的module名字和vivado生成do文件路径,该软件会根据路径和tb的module名字找到Vivado生成do文件,提取do文件里面的信息,把对应文件放到自动化仿真文件夹里面。提取目的仿真工具的win64和.setup文件的路径,用于建立批处理文件和makefile文件。提取完信息后,点击“开始生成按钮”即完成建立自动化仿真操作。

该软件在可执行python的环境下均可以运行,在实际项目测试中,能够自动生成自动化仿真工程,减少仿真对vivado的依赖,减少了大量的重复性操作。

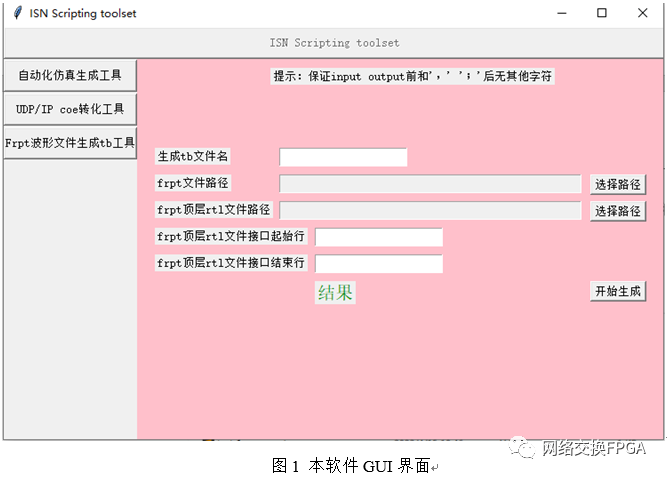

为了方便项目开发人员对辅助软件的使用,辅助软件需要具有良好的可视化操作界面,在完成一些基本参数的配置后,可一键式完成复杂操作。GUI界面如图1所示:

使用说明

1 安装和初始化

本软件免安装,通过点击FPGA_simulate_tool.exe文件即可执行,如图2所示:

2 输入

根据GUI界面的提示输入需要执行的命令。

3 输出

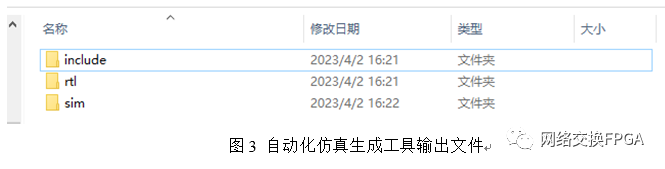

运行软件后,首先会根据选择生成不同的输出文件,选择“自动化仿真生成工具”,输入提示信息后,点击生成“开始生成”,会生成自动化仿真工程,如图3所示,其中所有rtl文件存放在rtl文件夹下,include文件存放在inlcud文件夹下,sim文件存放do文件和批处理文件。

操作步骤

本软件在Window10的python可执行环境下示例操作。自动化仿真生成工具使用步骤如下:

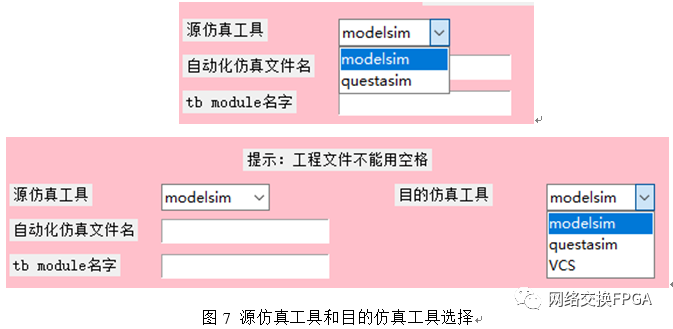

步骤1:首先选择源仿真工具和目的仿真工具。源仿真工具可供选择的有:ModeSim、Questasim,目的仿真工具可供选择的有ModeSim、Questasim、VCS,如图7所示。

步骤2:输入tbmodule名字、自动化仿真文件名字,会产生该名字的文件夹,自动化仿真工程在该文件夹里面。

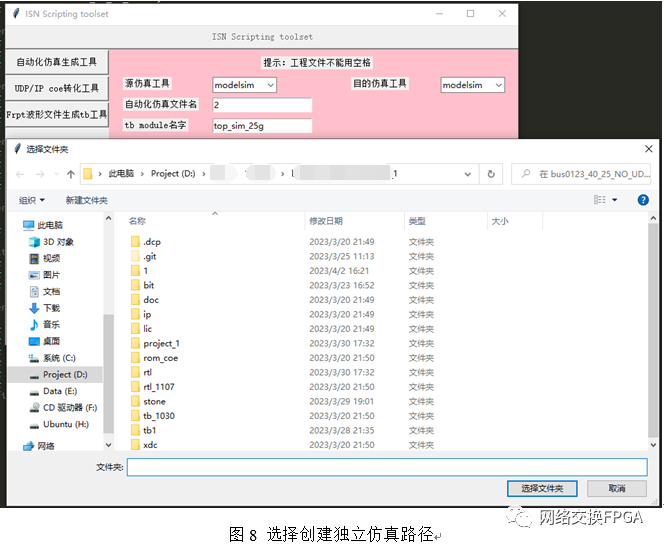

步骤3:选择“创建独立仿真路径”后面的“选择路径”按钮,会让选择路径,选择好后点击“选择文件夹”按钮,选择创建独立仿真路径,如图8所示:

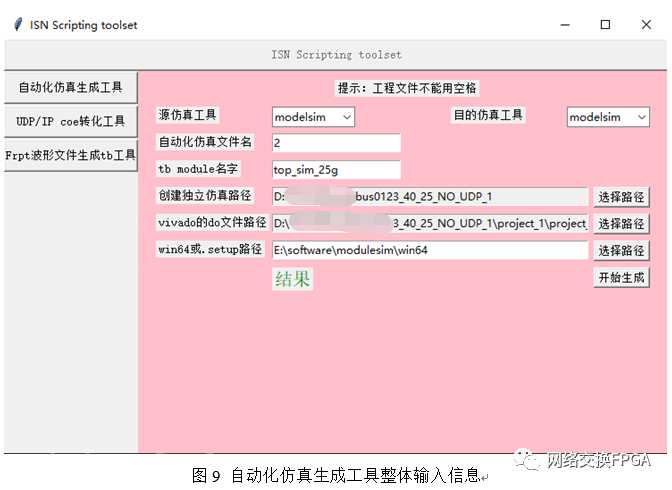

步骤4:点击“选择路径”按钮,选择vivado的do文件路径和win64或.setup路径,整体输入信息如图9所示:

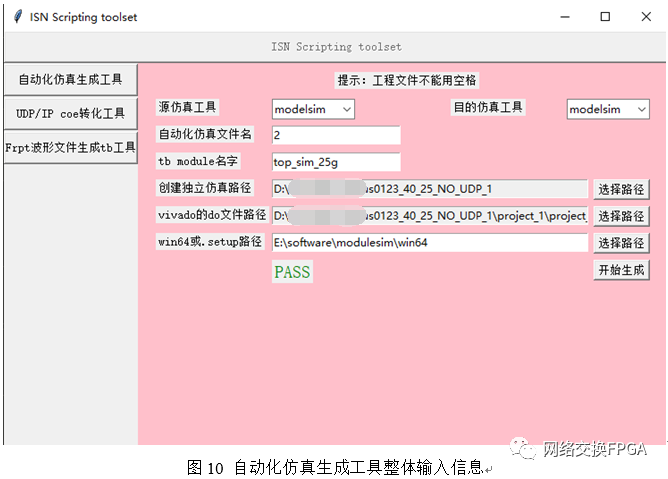

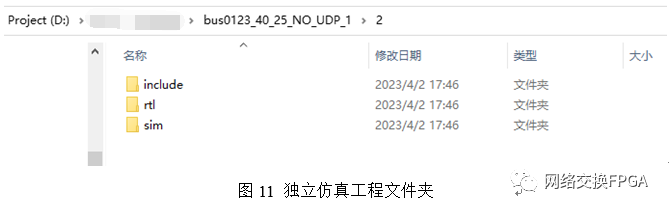

步骤5:点击“开始生成”按钮,生成独立仿真工程,生成成功会显示“PASS”。如图10所示。其中独立仿真工程目录在D盘文件夹“bus0123_40_25_NO_UDP_1”,文件名为“2”。该文件夹下内容如图11所示,其中所有rtl文件在rtl文件夹下,所有include文件在include文件夹下。

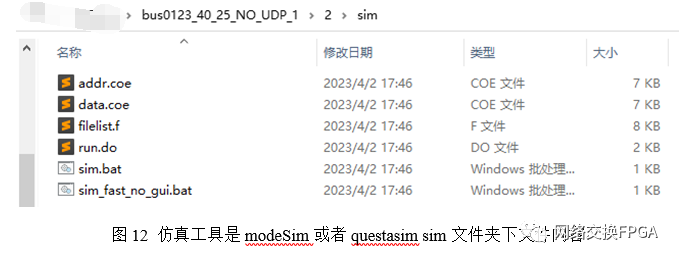

当目的仿真工具选择“modelsim”或者“questasim”,sim文件夹内容如图12所示。其中.coe文件是源vivado工程的RAM的初始化文件,不是该软件生成的文件。filelist.f文件存放所有需要编译的rtl列表,run.do文件是用于自动化仿真,sim.bat和sim_fast_no_gui.bat是批处理文件,以上四个文件都是该软件生成。点击sim.bat或者sim_fast_no_gui.bat即可运行仿真工具进行自动化仿真,其中sim_fast_no_gui.bat省去了仿真工具的GUI界面,可以加速仿真速度。

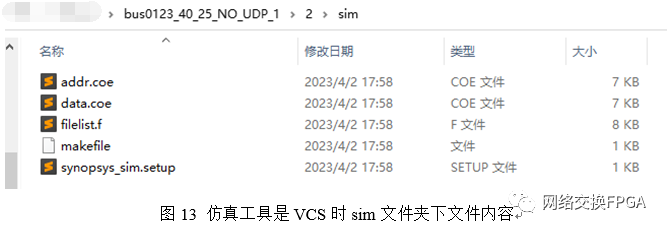

当目的仿真工具选择“VCS”时(虽然Vivado联合VCS仿真时有自带的一键转换到VCS仿真的功能,但本文软件提供的是一种更直接的脱离方式,把用到的库和所有文件单独提取出来放到一个文件夹中,便于分享,也便于为ASIC化的IP替换创建必要的环境),sim文件夹内容如图13所示。其中.coe文件是源vivado工程的RAM的初始化文件,不是该软件生成的文件。

filelist.f文件存放所有需要编译的rtl列表,makefile是自动仿真文件,输入make即可进行VCS的自动化仿真,仿真完后输入makeverdi,即可用verdi打开波形文件。

上图中双击sim.bat文件即可运行。

说明:建议在原Vivado工程所在的机器上运行该软件提取相关脚本信息,原Vivado工程需要调用第三方仿真工具运行过并保留相应的sim文件夹。如有问题,请检查vivado版本和仿真工具版本,以及编译的vivado仿真库所用的vivado版本和仿真工具版本。

结论

本软件根据预先定义的Python脚本命令,通过用户与GUI界面的交互,输入必要的信息,将原本重复繁琐操作通过辅助软件进行简化,提升了RTL的仿真的工作效率。本软件通过将大量重复性文件和文件夹进行批处理,减少了人力创建文件夹,书写重复代码,人工转化表项等繁琐操作。此外,通过GUI界面的交互,提供了一个可视化界面,极大的提高了软件的可操作性。

审核编辑:刘清

-

FPGA

+关注

关注

1631文章

21808浏览量

606807 -

FPGA设计

+关注

关注

9文章

428浏览量

26671 -

仿真

+关注

关注

50文章

4134浏览量

134145 -

仿真器

+关注

关注

14文章

1019浏览量

83998 -

RTL

+关注

关注

1文章

386浏览量

60028 -

GUI

+关注

关注

3文章

663浏览量

39953 -

python

+关注

关注

56文章

4811浏览量

85124 -

Vivado

+关注

关注

19文章

815浏览量

66984

原文标题:脱离Vivado建立单独仿真环境软件

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于PFGA的脱离Vivado单独建仿真环境工程

如何用Python实现Vivado和ModelSim仿真自动化?

怎样去使用PROTEUS电子仿真软件呢

如何使用vivado仿真zynq7000ov5640程序呢?

介绍一下xilinx的开发软件vivado的仿真模式

Vivado软件仿真DDS核的过程中应该注意的问题

Vivado调用Questa Sim或ModelSim仿真小技巧

如何脱离Vivado建立单独仿真环境软件呢?

如何脱离Vivado建立单独仿真环境软件呢?

评论