点击上方蓝字关注我们

1.概述

随着图像处理技术的快速发展,图像采集处理系统在提高工业生产自动化程度中的应用越来越广泛。本文结合实际系统中的前端图像处理和图像数据传输的需要,充分利用ARM的灵活性和FPGA的并行性的特点,设计了一种基于ARM+FPGA的高速图像数据采集传输系统。所选用的ARM体系结构是32位嵌入式RISC微处理器结构,该微处理器拥有丰富的指令集且编程灵活;而FPGA则在速度和并行运算方面有很大优势,适合图像处理的实时性要求;并且通过千兆以太网接口实现了采集板与上位机之间图像数据的高速远程传输。

2.硬件设计方案

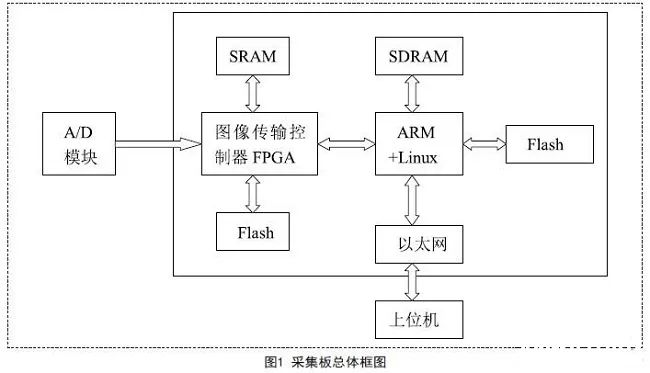

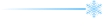

2.1 系统总体设计

本设计采用的ARM芯片为三星公司的S3C2440A、FPGA芯片为Xilinx公司生产的Spartan系列的S3C500E芯片,系统组成还包括千兆以太网控制芯片AX88180、千兆PHY芯片88E1111、存储器、嵌入式Linux、网络驱动程序等(如图1所示)。

本设计的主控芯片S3C2440A是基于ARM920T核的16/32位RISC微处理器,采用了0.13um的CMOS标准宏单元和存储器单元,运行频率高达500MHz.ARM920T 实现了MMU,AMBA BUS和Harvard高速缓冲体系结构构。这一结构具有独立的16KB指令Cache和16KB数据Cache.每个都是由具有8字长的行组成。通过提供一套完整的通用系统外设,S3C2440A减少整体系统成本和无需配置额外的组件。它主要面向手持设备以及高性价比、低功耗的应用,具有非常丰富的片上资源。

FPGA芯片S3C500E主要用于图像传感器的控制、图像数据的缓存及外围芯片时序的产生。它通过控制A/D实现数据采集,并保存至SRAM,对ARM的读写信号进行译码以将目标数据读回ARM并传到上位机。

ARM芯片S3C2440A负责整个系统的控制,它通过读写总线上的地址来进行指令和数据的传输以控制FPGA的所有动作[1-2]。嵌入式Linux内核负责系统任务的管理并集成TCP/IP协议,方便实现网络控制功能。

S3C2440A与AX88180以总线方式连接,是通信控制的主体。S3C2440A通过网络驱动程序实现对AX88180内部寄存器编程,以及对以太网数据的发送和接收,从而完成网络与系统之间的数据传输。

AX88180与88E1111之间采用RGMII接口方式互连,负责数据传送底层协议的实现。

2.2 数据采集接口设计

系统设计的难点在于数据采集接口的设计,它是数据传输的通道,同时也是连接系统前后端的桥梁。本系统采用S3C2440A和S3C500E配合共同实现数据的高速采集。

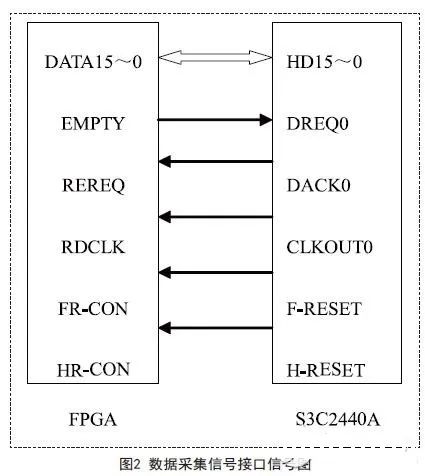

直接内存存取(DMA)作为一种独立于CPU的后台批量数据传输技术,以其快速、高效的特点在数据采集领域得到了广泛的应用。本设计中,S3C2440A采用外部DMA方式采集FPGA内部存储数据,其接口信号连接如图2所示。

接口设计的FPGA部分主要包括异步FIFO模块、复位模块和数据缓冲模块组成。异步FIFO模块主要解决图像输出数据频率和数据采集的频率不匹配的问题,系统采用的异步FIFO宽度为8bits,深度为2048.复位模块在控制信号的作用下实现对系统的FIFO的复位控制。

系统采用DMA通道0采集图像数据。

其中,DREQ0和DACK0分别为DMA的请求和应答信号。FPGA的空信号EMPTY与DREQ0相连,读请求RDREQ与DACK0相连。FPGA写时钟由图像输出位同步信号提供,读时钟由S3C2440A的时钟输出引脚CLKOUT0提供。CLKOUT0根据S3C2440A内部寄存器的设置可以输出几种不同的时钟频率。FIFO的读操作与ARM的DMA操作配合进行。系统采用单服务命令模式的DMA操作,每次传输一个字节数据位。当DREQ0信号变为低电平时DMA操作开始,每次传输一个字节后产生一个DACK0应答信号,而且只要DREQ0为低电平DMA操作就继续进行,直到DMA控制寄存器中的计数器为0,产生DMA中断。根据上述时序特点,将FIFO的空信号作为DMA的请求信号DREQ0.当图像输出的数据写入FIFO中时,空信号跳变为低电平启动DMA操作,同时以DACK0信号作为FIFO的读请求。每次DMA操作后产生的应答信号DACK0使FIFO内部的读指针前移1位指向下次要读出的数据。F-RESET和H-RESET分别控制FPGA内的帧同步复位和行同步复位,保证系统在每帧信号到来时开始工作,同时每采集完一行信号复位FIFO.FIFO输出数据经过以nGCS4为选通信号的BUFFER后接到ARM的数据总线上。nGCS4是S3C2440A存储空间中BANK4的片选信号,当S3C2440A对地址范围0×20000000~0×28000000的存储空间进行读写操作时为低电平,其余时间为高电平,NGCS4作为缓冲模块的选通信号可以有效地避免数据总线的污染。

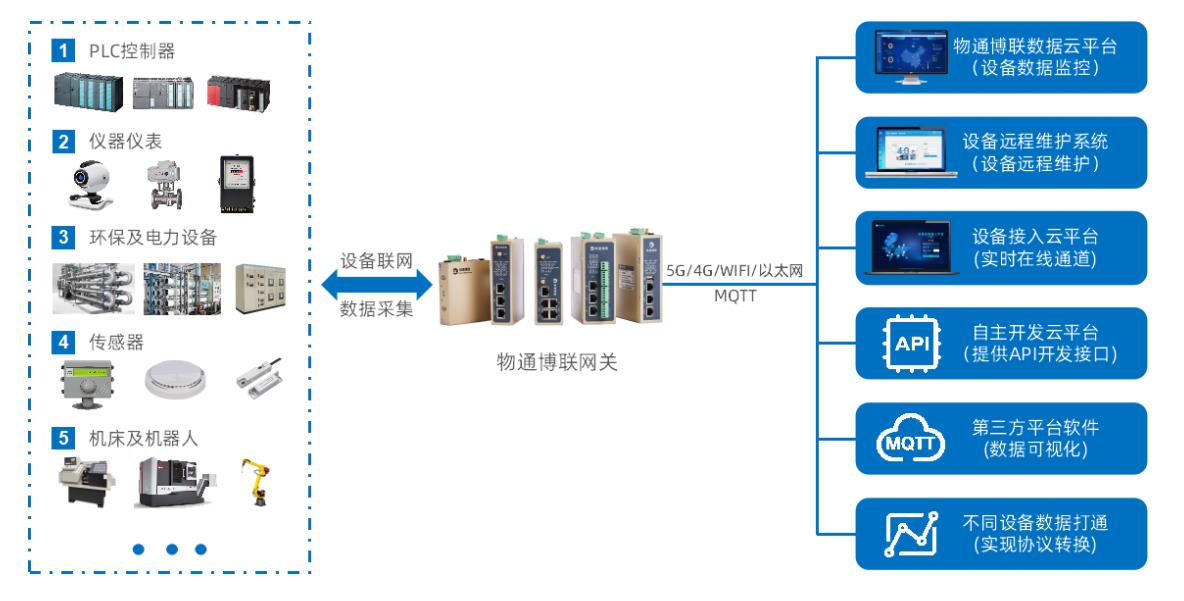

2.3 网络传输接口设计

本设计采用的以太网控制器为***亚信公司推出的一款Non-PCI千兆以太网控制芯片AX88180.其内置1000Mbps以太网媒体存取控制器(MAC);它可以十分方便地实现与一般16/32位微处理器连接,并且可以像SRAM一样被访问;它有40KBytesSRAM网络封包缓存器。它符合IEEE802.3/IEEE802.3u/IEEE802.3ab协议,可广泛应用于各种消费电子和家庭网络市场或要求更高的网络带宽连接,如数字媒体、家用网关及IP电视等。

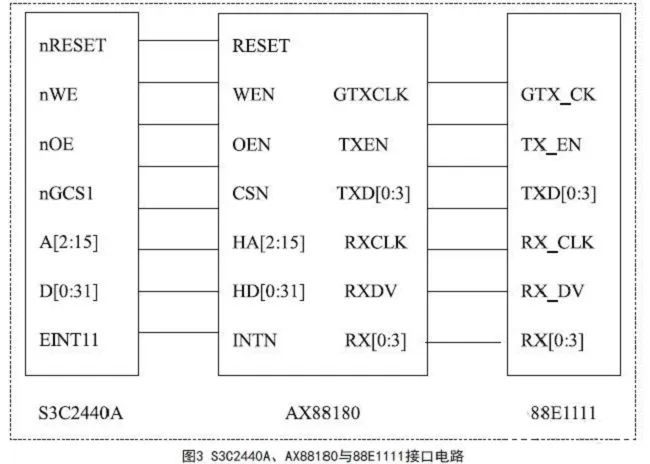

嵌入式芯片S3C2440A、以太网控制器AX88180及物理层芯片88E1111的接口电路图如图3所示。

S3C2440A与AX88180之间采用总线方式相连,地址总线A2~A15、数据总线D0~D31、读写信号等可以直接连接,AX88180中断信号与S3C2440A EINT11相连,AX88180的40M~100M时钟信号由S3C2440A提供,整个接口电路无需外加电路;AX88180与PHY芯片之间采用简化千兆比特媒体RGMII接口,信号对应 相连,负责实现数据传送底层协议[5]。

3.Linux驱动程序设计

FPGA作为ARM的外设,需要设计它在Linux下的驱动程序。驱动程序是操作系统与硬件之间的接口,它为应用程序屏蔽硬件的细节。硬件系统只有和高效可靠的驱动程序相结合才能在操作系统下正常工作。

Linux的设备驱动程序需要完成如下功能:

①对设备进行初始化和释放。

②提供各类设备服务。

③负责内核和设备之间的数据交换。

④检测和处理设备工作过程中出现的错误。

Linux下的设备驱动程序被组织成一组完成不同任务的函数集合,通过这些函数使Windows的设备操作犹如文件一般。

Linux将设备分为字符设备和块设备两类。我们使用的是字符设备。驱动程序的模块化我们先不做介绍,我们主要介绍Linux下的中断[6].Linux将中断处理程序分解成两个半部:上半部和下半部。上半部完成尽可能少的比较紧急的功能,下半部用来完成中断事件的绝大部分任务。因为中断的耗时工作在这里完成,所以将读取数据放在下半部完成。Linux系统实现下半部采用的机制主要有tasklet、工作队列和软中断。许多设备涉及到中断操作,因此,在这样的设备的驱动程序中需要对硬件产生的中断请求提供中断服务程序。与注册基本入口点一样,驱动程序也要请求内核将特定的中断请求和中断服务程序联系在一起。在Linux中,用request_irq()函数来实现请求:

int request_irq(unsigned intirq,void(*handler)int,unsigned longtype,char*name);

参数irq为要中断请求号,参数handler为指向中断服务程序的指针,参数type用来确定是正常中断还是快速中断(正常中断指中断服务子程序返回后,内核可以执行调度程序来确定将运行哪一个进程;而快速中断是指中断服务子程序返回后,立即执行被中断程序,正常中断type取值为0,快速中断type取值为SA_INTERRUPT),参数name是设备驱动程序的名称。

我们的中断处理函数是:

void fpgalc12_interrupt(int irq,void*dev_id,struct pt_regs*regs)。

Irqflags是中断处理的属性,若设置了SA_INTERRUPT,则表示中断处理程序是快速处理程序,快速处理程序被调用时屏蔽所有中断,而慢速处理程序不屏蔽。dev_id在中断共享时会用到,一般设置为这个设备的结构体或NULL.request_irq()返回0表示成功,返回-INVAL表示中断号无效或处理函数指针为NULL,返回-EBUSY表示中断已经被占用且不能共享。这两个函数分别要在初始化和释放模块中加载。

要在Linux申请了中断通道后,系统会响应外部中断IRQ_EINT0,从而进入中断处理序。中断处理程序功能就是将有关中断接收的信息反馈给设备,并根据要服务的中断的不同含义相应地对数据进行读写[7-8]。所以FPGA中断处理的主要任务是:FIFO在接收到AD转换来的数据后,向ARM发出中断请求信号,让ARM来读取FPGA中FIFO状态寄存器的值,获取需要信息并安排接受数据,然后写状态寄存器清除相关中断位以继续响应中断,保证数据的有效传输。

中断处理程序的第一步是要先清除S3C2440A的中断悬挂寄存器和中断源寄存器相应的位。这是为了能够继续响应FPGA产生的中断。为了能够让FIFO能及时的接收到新数据,把写状态寄存器放到中断的一开始,即第二步就是写状态寄存器相应位,通过置1清除状态使AD中断能够继续产生。最后读取FIFO的数据。使用中断后数据的传输效率大大得到提高,能够满足实际的采集需要。

4.结束语

本方案中的采集板充分利用了ARM的灵活性和FPGA的并行性的特点,实现了适用于高速数据采集板的设计。方案采用S3C2440A作为主控芯片,通过千兆以太网接口实时地将采集的数据传输到上位机PC机,上位机可实时控制目标数据采集。FPGA芯片在控制A/D转换芯片的同时,将数据存储在SRAM中,并通过DMA接口与S3C2440A进行数据传输。实验表明,本采集板的实时性和高速性能够满足系统的设计要求,可广泛应用于各种数据采集系统中。

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:基于ARM和FPGA设计高速图像数据采集传输系统

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1629文章

21734浏览量

603117

原文标题:基于ARM和FPGA设计高速图像数据采集传输系统

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

利用ADS869X做一个隔离的高速数据采集系统,ADC需要一个时钟信号,可以自己外接一个晶振电路吗?

高速分切机数据采集监控告警系统解决方案

基于ARM和FPGA设计高速图像数据采集传输系统

基于ARM和FPGA设计高速图像数据采集传输系统

评论