今天来讨论一个I2C走线问题,过程是通过用ST提供的IBIS模型,从SI的角度出发,做SI仿真来评估STM32的I2C信号和确定Layout走线到底能走多长。

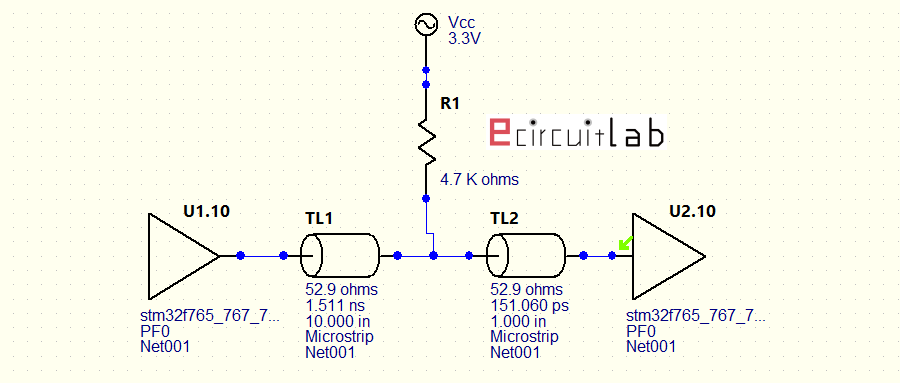

这里我选择了STM32F765XX-LQFP144封装的IBIS模式来实验,在Hyperlynx上把Layout模型电路画好如下图所示,U1使用STM32的PF0脚作为发送端,这个脚可以复用为SDA信号,U2使用STM32的PF0作为接收端,TL1、TL2分别为10in(25.4厘米)和1in(2.54厘米)的微带线走线,R1为上拉电阻。

图1. 使用STM32F765系列LQFP144封装的IBIS模型搭建的电路

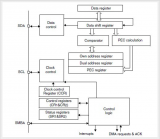

搭建好Layout电路后,打开Model Selector给U1和U2赋予对应的IBIS模型,可以看到,ST提供的STM32 IO有四种速度等级,和带或不带上下拉电阻几种,如下。

图2. IO有4中速度等级模型,每种又分带或不带上下拉电阻

上图中可以看到,IO内置的上拉电阻比较大,实际使用中一般不用内置电阻,都是外挂上拉电阻,所以我们 先选择最低速度SPEED0不带上下拉的模型验证 。

设置好模型后运行仿真,设置仿真条件为Oscillator模式,速率400K,IC modeling为Fast-Strong模式,模拟I2C以400K时钟速率运行,查看接收端波形如下图所示,可以看到波形很好,没有什么比较严重的过冲啥的,没啥问题。

图3. 速度等级为SPEED0,Layout走线11in(29.29厘米),400K速率运行波形正常

现在对标我们平时的产品设计,有时I2C会绕板子不止28.29厘米这么长,那我们试试把长度拉大到50厘米,设置TL1为20in(长度50厘米多),然后再运行仿真得到如下图结果。

图3. 速度等级为SPEED0,Layout走线21in(53.34厘米),400K速率运行波形有过冲

可以看到这时对于接收端接收到的波形,过冲有点严重了,因为STM32的IO可以兼容5V电平,所以这里高电平的过冲还没超过5V,我们就先不管。但是低电平时的下冲有318.7mV了。那到底要不要管呢?首先我们去翻下规格书,在规格书中找到电压特性表如下所示。

可以看到对于输入下冲信号,最小电压值是VSS-0.3V,即所选STM32的IO能接受的下冲最大为-0.3V,不能超过-0.3V。现在再看上面仿真的下冲电压,显然已经越过这个值。

芯片如果长时间在这样的条件下工作,可能一段时间后,IO就损坏失效,这也是我们很多产品在客户现场使用,一段时间后芯片的某个IO损坏的原因之一,就是Layout处理不好,有过冲、下冲超过IO极限值导致。当然,也有可能是其他原因导致,比如ESD之类的。

图4. STM32规格书中的IO输入电压极限值

那对于STM32的I2C Layout走线多长适合呢? 这里我尝试了不同长度仿真分析,总结为,对于STM32F7系列的芯片来说,IO速度等级为慢速,I2C Layout走线不建议超过45厘米 。其他系列的可以参考这个信息轻微浮动,如果可以的话,尽可能使用IBIS模型仿真评估。

那是不是得到这样的结论后我们就可以结束了呢?不,其实还有一大堆坑。上面我特别的去强调我使用的IO的速度等级是SPEED0,慢速等级。图2中我们看到还有3种速度等级可以选用,实际中我们也可以代码配置为另外的3种速度等级,那如果我们更改下速度等级会不会有影响呢?这里我马上做了尝试,保持Layout走线长度为上面结论的45厘米长,把输出IO的速度等级换为SPEED1,运行仿真得到结果如下。从结果可以看到,速度等级升高后,上面的结论就不成立了,此时高电平的过冲仍然还在可接受范围内,但下冲就不是那么友善了,都-905.4mV了,这样搞,芯片不坏都天理难容。

图5. 把IO速度等级换为SPEED1,Layout走线长度保存45厘米,仿真有严重过冲

从上面这个步骤来看,速度等级增加后,会使过冲变得严重,那这样的话,我们就不尝试SPEED2了,直接看SPEED3,看看最高速度等级到底会糟糕成什么样。同样保持Layout走线长度为45厘米不变,IO速度等级调整为SPEED3,运行仿真得到结果如下。嗯,看起来还好,没有糟糕到可以炸板,相对SPEED1来说,高电平过冲也还在可接受范围,下冲多了几个mV。

图6. 把IO速度等级换为SPEED3,Layout走线长度保存45厘米,过冲情况跟SPEED1差不多

实验到这里我突然好奇,现在ST主推用CubeMX来自动生成配置代码,用户在使用I2C时,它的IO会默认配置为什么样的速度等级?于是我马上打开CubeMX做了个尝试,很快就得到了答案,不过看完我傻眼了,默认配置为SPEED3,如下图所示。

根据上面仿真情况,我想了想,要是哪天哪位冤种用这配置代码放在一个主控到I2C从机设备线缆比较长的产品中,要是出问题了,估计加班排查好久都不一定查出来。

图7. CubeMX对于I2C的IO速度等级默认配置为SPEED3

说到上面的大冤种情形,想起2年前做的一个产品,产品也是主板上通过线缆把I2C信号拉到子板上配置子板的芯片,线缆有50厘米长。当时I2C主机总会莫名其妙的把子板芯片搞挂,最后发数据没ACK,需要重新给子板上电后才能恢复正常,但过一会又不行,当时搞得也是头疼。当时使用的主控是Altera的FPGA,排查无果后我倒回去重新看FPGA的规格书,在IO特性里发现IO的上升下降沿都比较陡,当时就觉得是遇到SI的问题了,然后就马上调了FPGA的IBIS模型搭模型电路仿真,结果跟猜测一样。

理论、仿真分析确认问题点后,因为FPGA的IO特性就那样,没办法去改变,想了想后就找了颗上升、下降沿没那么陡的电平转换芯片,放在FPGA IO和子板芯片IO之间做缓冲,最后问题解决。

唠嗑完大冤种后,我们再来看看使用SPEED3时,留给Layout的走线长度裕量还有多少。经过反复尝试,最终定下来对于我使用的STM32F765XX-LQFP144这颗芯片,使用I2C外设,如果IO速度等级配置为SPEED3模式的话,保险Layout走线长度建议控制在0.6in(1.524厘米)内,下图为控制长度为0.6in的仿真结果,长了就下冲厉害。

图8. IO速度等级为SPEED3时,控制Layout走线在0.6in时的仿真结果

惊讶吧!1.524厘米长,把这个约束给Layout工程师估计会被打死,所以对于STM32的I2C Layout要求,硬件设计时可以使用前面建议的45厘米长度约****束,但必须注意要求软件把IO速度等级配正确 ,不然大家都得加班查Bug。

原理讲解

现在我们经过一波仿真实操验证后,知道了STM32的I2C Layout最大走线长度的参考,那究竟是什么原因导致我们的Layout走线没法再增长呢?下面我简单解释下。

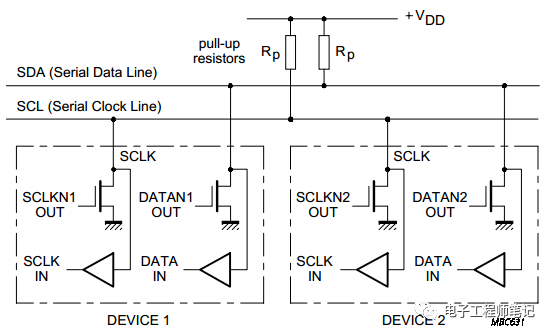

首先对于我们看到的Layout走线,细化去看的话,可以等效为下图所示的电路模型,由寄生电感和寄生电容构成。信号在上面传输时,如果电平翻转的上升、下降沿比较陡,那么在接收端接收到的电压不再等于输出端的电压,而是V=L*di/dt。

从这个公式可以看到,影响电压V的就是寄生电感L和IO的上升、下降沿dt,所以解决V不过度变化大的方法就是要么让L尽可能小,要么就是让上升、下降沿增大。L变小就是走线尽可能短,IO上升、下降沿增大一般就是找电平转换芯片来做做缓冲改善。

图9. Layout走线的寄生电路模型

如果对于上面的理论还是难以理解,那没问题,我们直接来搭一个电路仿真看看也可以。参考上面电路模型我们搭一个电路和仿真如下,电路设置输出周期15ns,50%占空比的波形,上升沿、下降沿设置为3ns,可以看到,输出波形震荡过冲和下冲还是比较大。

图10. 搭建Layout走线电路模型,设置上升、下降沿为3ns仿真波形

我们再把上升、下降沿时间缩小到1ns看看,仿真结果如下,可以看到过冲、下冲更大,所以这也验证了上面的理论解释。

图11. 搭建Layout走线电路模型,设置上升、下降沿为1ns仿真波形

同样为了论证减小L带来的改善,在上图11的基础上,把寄生电感缩小为0.1nH,运行仿真,从仿真结果来看,已几乎不再有过冲、下冲,也符合我们理论解释情况。

图11. 搭建Layout走线电路模型,设置寄生电感为0.1nH的仿真波形

-

STM32

+关注

关注

2270文章

10904浏览量

356326 -

I2C总线

+关注

关注

8文章

391浏览量

60974 -

寄生电感

+关注

关注

1文章

156浏览量

14604 -

FPGA芯片

+关注

关注

3文章

246浏览量

39803 -

LQFP封装

+关注

关注

0文章

10浏览量

7396

发布评论请先 登录

相关推荐

i2c总线ppt(I2C总线器件应用)

I2C LCD 器件通过驱动带有 I2C 接口的 2 线式 16 字符 LCD

STM32 I2C硬件的结构

STM32学习之I2C协议(读写EEPROM)

STM32的硬件I2C有BUG吗?

I2C接口配置ES7243录音芯片,MCU(STM32)收不到I2C ACK的问题

STM32F103硬件I2C Slave

硬件I2C与模拟I2C

STM32F 单片机硬件I2C Busy标志导致的I2C卡死的处理办法

I2C上拉电阻如何选择合适的阻值?

对于STM32的I2C Layout走线多长合适呢?

对于STM32的I2C Layout走线多长合适呢?

评论