Cortex-M 中断

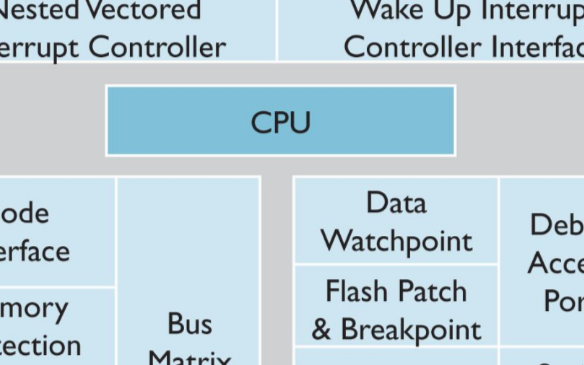

Cortex-M 内核(STM32)的 MCU 提供了一个用于中断管理的嵌套向量中断控制器(NVIC)。Cotex-M3 的 NVIC 最多支持 240 个 IRQ(中断请求)、1 个不可屏蔽中断(NMI)、1 个 Systick(滴答定时器)定时器中断和多个系统异常。

Cortex-M 处理器有多个用于管理中断和异常的可编程寄存器,这些寄存器大多数都在 NVIC 和系统控制块(SCB)中,CMSIS 将这些寄存器定义为结构体。以 STM32F103 为例,打开 core_cm3.h,有两个结构体,NVIC_Type 和 SCB_Type,就存储了这些信息。

优先级分组定义

当多个中断来临的时候处理器应该响应哪一个中断是由中断的优先级来决定的,高优先级的中断(优先级编号小)肯定是首先得到响应,而且高优先级的中断可以抢占低优先级的中断,这个就是中断嵌套。

Cortex-M 处理器的有些中断是具有固定的优先级的,比如复位、NMI、HardFault,这些中断的优先级都是负数,优先级也是最高的。

Cortex-M 处理器有三个固定优先级和 256 个可编程的优先级,最多有 128 个抢占等级,但是实际的优先级数量是由芯片厂商来决定的。但是,绝大多数的芯片都会精简设计的,以致实际上支持的优先级数会更少,如 8 级、16 级、32 级等,比如 STM32 就只有 16 级优先级。

FreeRTOS 中断配置宏

1、configPRIO_BITS:设置 MCU 使用几位优先级,STM32 使用的是 4 位,因此此宏为 4

2、configLIBRARY_LOWEST_INTERRUPT_PRIORITY :设置最低优先级。

3、configKERNEL_INTERRUPT_PRIORITY:此宏用来设置内核中断优先级。

4、configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY:来设置 FreeRTOS 系统可管理的最大优先级,是高于 x 的优先级不归 FreeRTOS 管理!

5、configMAX_SYSCALL_INTERRUPT_PRIORITY:低于此优先级的中断可以安全的调用 FreeRTOS 的 API 函数,高于此优先级的中断 FreeRTOS 是不能禁止的,中断服务函数也不能调用 FreeRTOS 的 API 函数!

-

处理器

+关注

关注

68文章

19164浏览量

229123 -

嵌入式

+关注

关注

5068文章

19018浏览量

303265 -

内核

+关注

关注

3文章

1363浏览量

40228 -

STM32

+关注

关注

2266文章

10871浏览量

354800 -

FreeRTOS

+关注

关注

12文章

483浏览量

62007

发布评论请先 登录

相关推荐

如何在zynq 7000平台下运行 java web程序

基于STM32应用的FreeRTOS中断设置

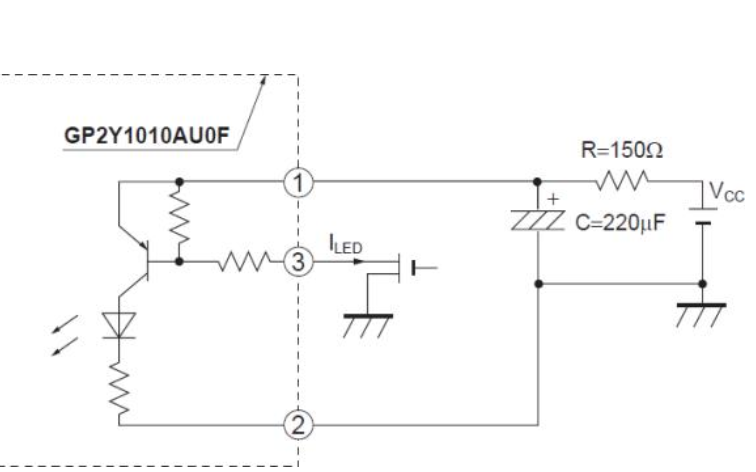

STM32平台下GP2Y1010AU0F灰尘传感器的使用源代码

基于STM32的FreeRTOS学习之中断配置和临界段(四)

stm32cubemx 配置FreeRTOS相关基础基础知识及串口接收中断实验

STM32之FreeRTOS:(一) 中断配置和临界段的使用

STM32平台下的FreeRTOS中断配置

STM32平台下的FreeRTOS中断配置

评论