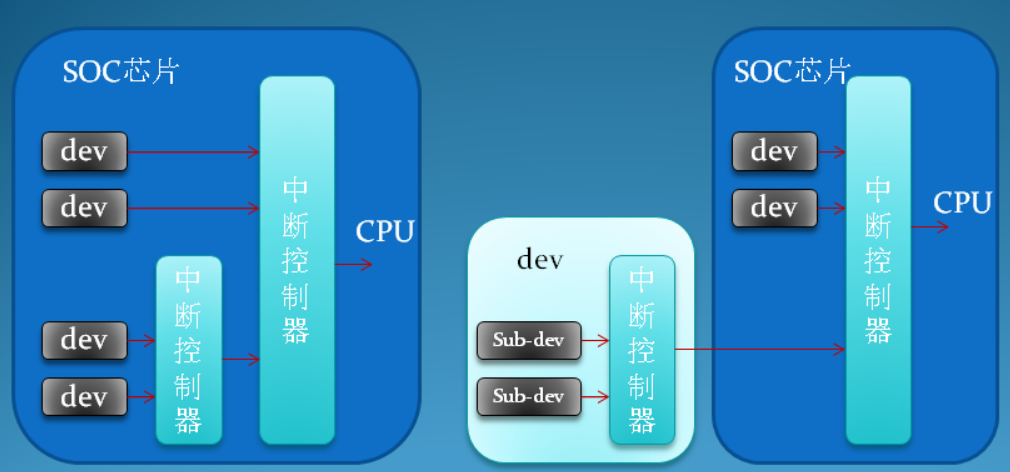

中断控制器的级联

根据中断数量的不同,中断控制器可以级联,以此来满足需求。比如在 GIC 中断控制器之前都会连接 EINT中断控制器,或者其他中断控制器,对不同的中断分级管控。

中断控制器的级联有两种类型:

机器级别的级联,级联的初始化代码理所当然地位于板子的初始化代码中(arch/xxx/mach-xxx),因为只要是使用这个板子或SOC的设备,必然要使用这个子控制器。

设备级别的级联,因为该设备并不一定是系统的标配设备,所以中断控制器的级联操作应该在该设备的驱动程序中实现。

机器设备的级联,因为得益于事先已经知道子控制器的硬件连接信息,内核可以方便地为子控制器保留相应的 irq_desc 结构和 irq编号,处理起来相对简单。

设备级别的级联则不一样,驱动程序必须动态地决定组合设备中各个子设备的 irq 编号和 irq_desc

结构。我只讨论机器级别的级联,设备级别的关联可以使用同样的原理。

中断子系统架构

整个中断子系统的架构分为 4 层,最底层(第四层)为硬件,包括 CPU、中断控制器。第三层是 CPU的驱动和中断控制器的驱动,由芯片原厂负责。第二层是 Linux内核提供的通用中断处理模块,这一层存在的意义在于,希望用户在第一层写的驱动在移植的时候更方便,保持接口不变,不让用户直接使用芯片原厂的 API,而是 Linux的 API。第一层就是驱动工程师日常写的驱动啦。

-

控制器

+关注

关注

113文章

16562浏览量

180300 -

Linux

+关注

关注

87文章

11372浏览量

211147 -

设备

+关注

关注

2文章

4580浏览量

71027 -

系统

+关注

关注

1文章

1022浏览量

21498

发布评论请先 登录

相关推荐

中断控制器级联的类型有哪几种

中断控制器级联的类型有哪几种

评论