GIC硬件原理

- ARM公司提供了一个通用的中断控制器

GIC(Generic Interrupt Controller),GIC的版本包括V1 ~ V4,由于本人使用的SoC中的中断控制器是V2版本,本文将围绕GIC-V2来展开介绍;

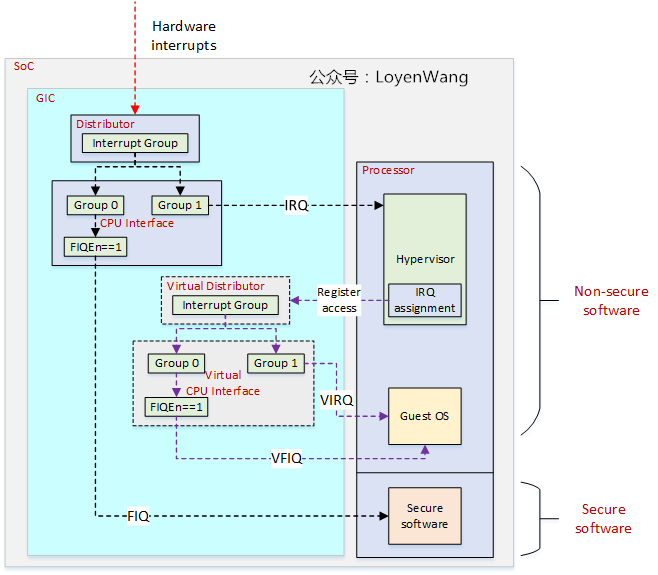

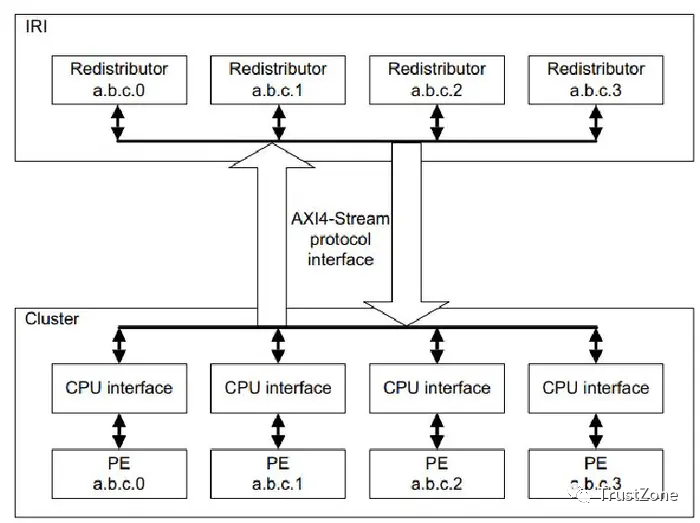

来一张功能版的框图:

GIC-V2从功能上说,除了常用的中断使能、中断屏蔽、优先级管理等功能外,还支持安全扩展、虚拟化等;GIC-V2从组成上说,主要分为Distributor和CPU Interface两个模块,Distributor主要负责中断源的管理,包括优先级的处理,屏蔽、抢占等,并将最高优先级的中断分发给CPU Interface,CPU Interface主要用于连接处理器,与处理器进行交互;Virtual Distributor和Virtual CPU Interface都与虚拟化相关,本文不深入分析;

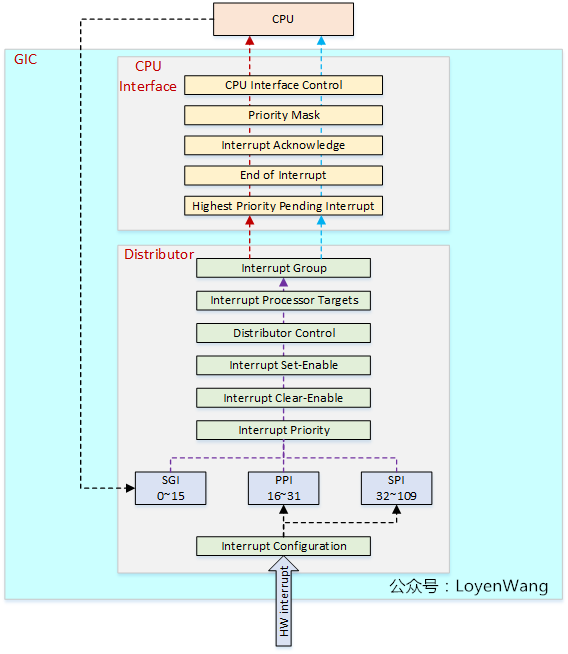

再来一张细节图看看Distributor和CPU Interface的功能:

GIC-V2支持三种类型的中断:SGI(software-generated interrupts):软件产生的中断,主要用于核间交互,内核中的IPI:inter-processor interrupts就是基于SGI,中断号ID0 - ID15用于SGI;PPI(Private Peripheral Interrupt):私有外设中断,每个CPU都有自己的私有中断,典型的应用有local timer,中断号ID16 - ID31用于PPI;SPI(Shared Peripheral Interrupt):共享外设中断,中断产生后,可以分发到某一个CPU上,中断号ID32 - ID1019用于SPI,ID1020 - ID1023保留用于特殊用途;

Distributor功能:- 全局开关控制

Distributor分发到CPU Interface; - 打开或关闭每个中断;

- 设置每个中断的优先级;

- 设置每个中断将路由的CPU列表;

- 设置每个外设中断的触发方式:电平触发、边缘触发;

- 设置每个中断的Group:Group0或Group1,其中Group0用于安全中断,支持FIQ和IRQ,Group1用于非安全中断,只支持IRQ;

- 将

SGI中断分发到目标CPU上; - 每个中断的状态可见;

- 提供软件机制来设置和清除外设中断的pending状态;

- 全局开关控制

CPU Interface功能:- 使能中断请求信号到CPU上;

- 中断的确认;

- 标识中断处理的完成;

- 为处理器设置中断优先级掩码;

- 设置处理器的中断抢占策略;

- 确定处理器的最高优先级pending中断;

中断处理的状态机如下图:

Inactive:无中断状态;Pending:硬件或软件触发了中断,但尚未传递到目标CPU,在电平触发模式下,产生中断的同时保持pending状态;Active:发生了中断并将其传递给目标CPU,并且目标CPU可以处理该中断;Active and pending:发生了中断并将其传递给目标CPU,同时发生了相同的中断并且该中断正在等待处理;

GIC检测中断流程如下:

- GIC捕获中断信号,中断信号assert,标记为pending状态;

Distributor确定好目标CPU后,将中断信号发送到目标CPU上,同时,对于每个CPU,Distributor会从pending信号中选择最高优先级中断发送至CPU Interface;CPU Interface来决定是否将中断信号发送至目标CPU;- CPU完成中断处理后,发送一个完成信号

EOI(End of Interrupt)给GIC;

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

嵌入式

+关注

关注

5101文章

19261浏览量

309676 -

Linux

+关注

关注

87文章

11372浏览量

211139 -

子系统

+关注

关注

0文章

110浏览量

12497 -

gic

+关注

关注

0文章

14浏览量

6307 -

控制器

+关注

关注

0文章

24浏览量

3274

发布评论请先 登录

相关推荐

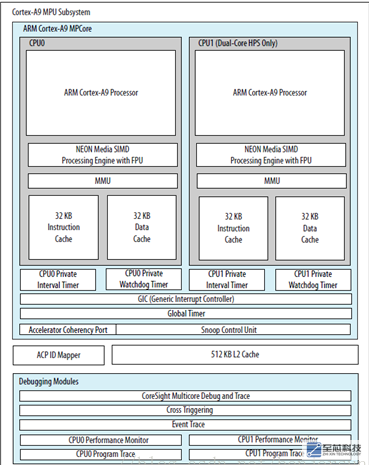

英特尔Altera系列cyclone V HPS GIC

大家好,又到了每日学习的时间了,今天我们来聊一聊英特尔 Altera系列 cyclone V HPS GIC. 一、CYCLONE V GIC配置 Cyclone v使用双核ARM CORTEX

ARM之中断GIC分析

1.“站的高尿的远” GIC为中断控制器,不要和ARM core的中断搞混了,这些中断都是连接到ARM core的IRQ或者FIQ上的。 要了解arm中断系统,GIC绝对不容错过,好先付

发表于 11-26 13:50

ARM GIC(一)之ARM soc中断的处理介绍

的桥接器件,就是arm公司推出大名鼎鼎的gic,general interrupt controller。gic其实是一个架构,版本历经了gicv1(已弃用),gicv2,gicv3,gicv4。对于

发表于 04-06 10:12

ARM GIC(二)之中断术语的定义

ARM在GIC中,对于中断,定义了如下的一些术语。一、中断状态对于每一个中断而言,有以下4个状态:◾inactive:中断处于无效状态◾pending:中断处于有效状态,但是cpu没有响应该中断

发表于 04-06 10:15

GIC ITS的ITS tables和Command Queue访问简析

ACE-Lite转换为了AXI interface,因而这个系统设计不能实现GIC ITS和CPU的硬件一致性。在这样的系统上运行Linux GICv3 driver可能会出现一致性问题:因为

发表于 12-20 14:35

小电阻器对治理电网GIC的效果分析

地磁感应电流(geomagnetically induced currents,GIC)引起变压器半波饱和对电力系统的安全运行产生不利影响,甚至引发大面积停电事故。为了有效治理GIC对大规模电力系统

发表于 01-04 17:03

•7次下载

应用K值算法的甘肃电网GIC-Q扰动计算

的安全运行。以甘肃750 kV电网和330 kV电网GIC的计算数据为基础,基于变压器GIC无功(GIC-Q)损耗系数K值算法,计算了750 kV和330 kV变压器的GIC无功损耗增

发表于 01-31 14:57

•3次下载

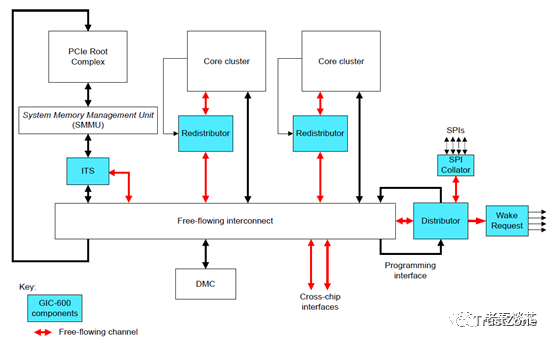

扒一扒GIC-600的相关知识

为了适应大规模的SoC设计,GIC-600被设计成分布式IP。所谓分布式,GIC-600由几种组件构成,每个组件可以跟其它相关模块在物理设计上摆放在一起,并与其拥有共同的电源域

发表于 02-06 11:36

•2903次阅读

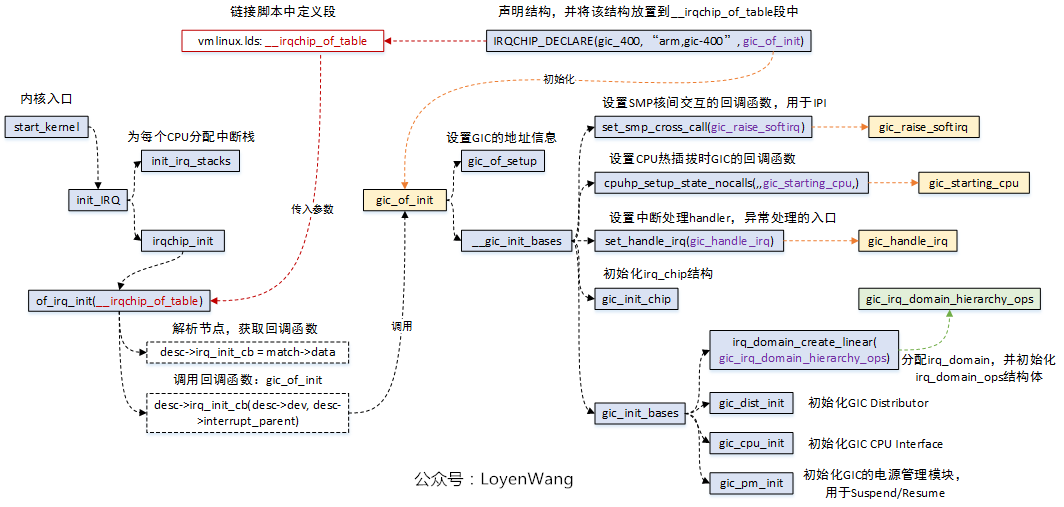

GIC驱动的执行流程是什么

驱动流程分析 GIC驱动的执行流程如下图所示: 首先需要了解一下链接脚本 vmlinux.lds ,脚本中定义了一个 __irqchip_of_table 段,该段用于存放中断控制器信息,用于最终来

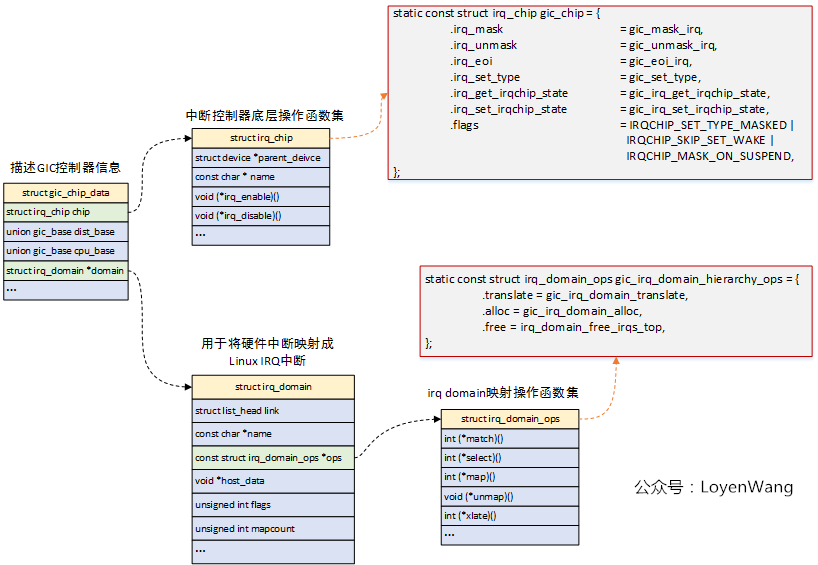

Linux GIC驱动数据结构分析

数据结构分析 先来张图: GIC驱动中,使用 struct gic_chip_data 结构体来描述GIC控制器的信息,整个驱动都是围绕着该结构体的初始化,驱动中将函数指针都初始化好,实际的工作

GIC-600的组件是如何连接的

为了适应大规模的SoC设计,GIC-600被设计成分布式IP。 所谓分布式,GIC-600由几种组件构成,每个组件可以跟其它相关模块在物理设计上摆放在一起,并与其拥有共同的电源域;组件之间通过片上网

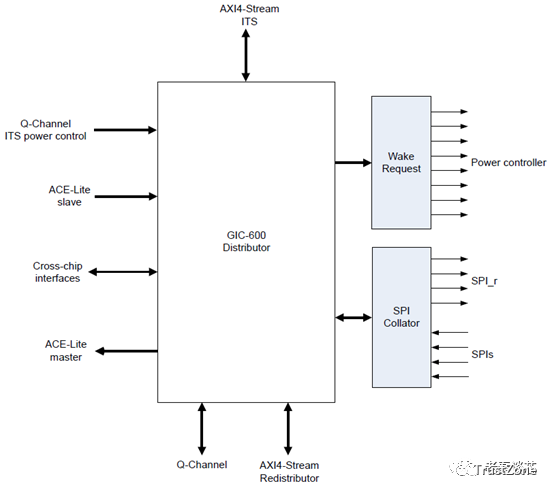

GIC-600的内部结构组件

接下来看看每个组件。 • 首先是distributor,一个SoC只有一个。 •它的组件只能与distributor通信。所以,可以看出,distributor是GIC-600中的核心,其作用是收集

gic和ARM Core的连接

• ◾nVIRQ: 虚拟普通中断 • ◾nVFIQ: 虚拟快速中断 (2)gicv3和ARM Core的连接 gicv3 AXI-stream协议 • ◾gic stream协议,是基于AXI-stream协议

GIC是什么意思 GIC硬件原理

GIC是什么意思 GIC硬件原理

评论