SDRAM是一种同步动态随机访问内存,它具有内置控制器,通过与CPU时钟同步来工作,使得数据传输更为高效。SDRAM在内存颗粒市场中占据主导地位,广泛应用于各种计算机系统和服务器中,为数据处理和存储提供了快速且可靠的支持。 SDRAM具有高速度、高密度、低功耗等优点。其内部结构采用Bank架构,允许同时进行多个读写操作,从而提高了整体性能。此外,SDRAM还具有自动刷新功能,能够确保数据在长时间内保持正确性。 华芯微特已经将SDRAM合封入芯片,合封的SDRAM大小根据芯片型号不同,具体见选型手册。

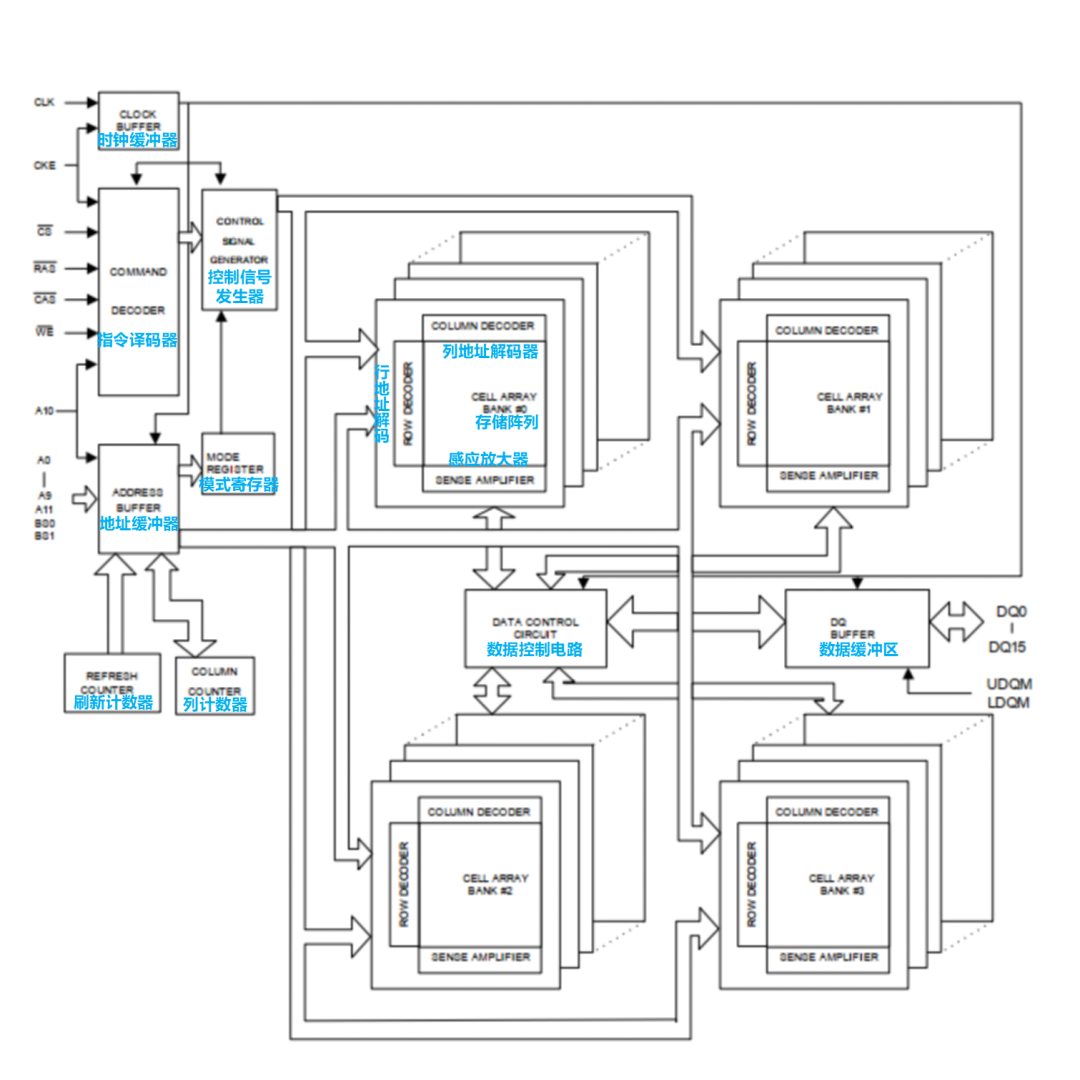

SDRAM 结构框图

SDRAM的内部是一个存储阵列,将数据“填”进去,你可以它想象成一张表格。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。 为了详细地介绍SDRAM以及它的使用,以某一款SDRAM数据手册结构框图来分析, 内部主要构成部分如下图所示:

01 SDRAM 信号线

CLK:同步时钟信号,提供SDRAM工作时钟,所有输入信号在CLK为上升沿时被采样。 CKE:时钟使能信号。时钟使能进入正常工作模式,时钟失能进入休眠模式或者自刷新模式。 CS :片选信号,低电平有效。 CAS:列地址选通,当为低电平时地址线表示为列地址。 RAS:行地址选通,当为低电平时地址线表示为行地址。 WE:读写指令切换信号。低电平:写使能;高电平:读使能。 DQM[1:0]:输入/输出掩码信号,表示DQ数据的有效部分。当DQM在读取周期中被采样为高时,输出缓冲器被置于Hi-Z(具有2的延迟)。在写入周期中,采样DQM高电平将以零延迟阻止写入操作。 BS:BANK地址输入,选择要控制的BNAK。 A[12:0]:地址信号线,地址线A10控制着是否进行在读或写操作之后当前L-Bank自动进行预充电。 DQ[15:0] :数据输入输出信号线。

对于DQM(Data I/O Mask)信号,每个DQM控制屏蔽8bit数据,对于这款SDRAM,它是16bit的,UDQM可屏蔽高8位,LDQM可屏蔽低8位。对于16bit的数0xDDFF,我们如果只需高8位写入,低8位不写入,在写入时可以将UDQM置低,LDQM置高。

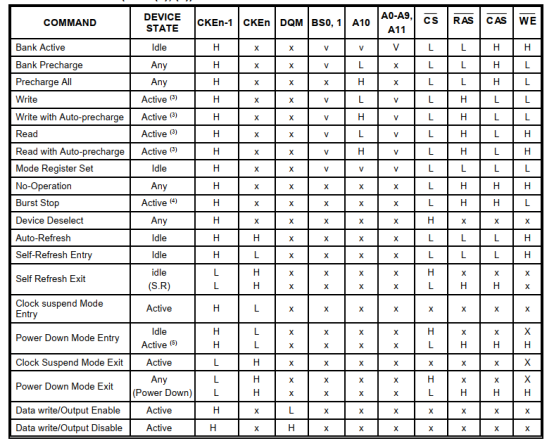

02 SDRAM 操作命令

NO-Operation:空操作命令,用于选中SDRAM,防止SDRAM接受错误的命令,为接下来的命令发送做准备。

Active (用于存储单位寻址):激活命令,该命令必须在读写操作之前被发送,用于设置所需要的BANK和行地址 (同时设置) ,BANK地址由BS0(BA0),BS1(BA1)决定,行地址由A0~12决定。

Read / Write:读/写命令,在发送完激活命令后,并进行读写再发送列地址就可以完成对SDRAM的寻址,并进行读写操作。

Precharge:预充电指令,用于关闭BANK中所打开的行地址,准备打开新行。进行完读写操作后,要对同一BANK的另一行进行寻址,就要将原来有效(打开)的行关闭,重新发送行/列地址。

Refresh:SDRAM存储的数据需要不断进行刷新操作才能保存,用于刷新一行数据,可以依次对所有的行进行刷新操作。CKE引脚高电平为自动刷新(Auto Refresh),CKE为低电平是自我刷新(Self Refresh)。

自动刷新:依靠刷新计数器(行地址生成器)自动依次生成要刷新的行地址刷新周期 (完成一次所有行的刷新所需要的时间) :64ms。自我刷新:用于休眠低功耗状态下的数据保存。

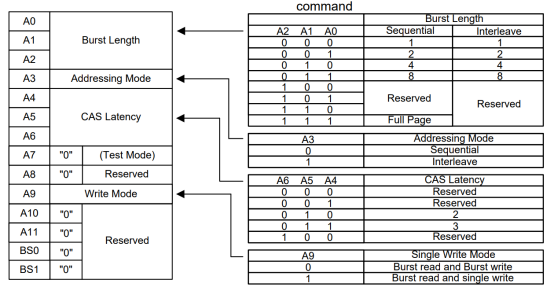

Mode Register Set:设置模式寄存器。SDRAM芯片内部有一个逻辑控制单元,控制单元的相关参数由模式寄存器提供。该命令在每次对SDRAM进行初始化时都需要用到。

具体模式设置,如下图:

A0~A2:用来指定突发的长度,1,2,4,8或者全页突发。所谓的“突发”是指当我们对一个地址进行寻址并操作完成后,不必再重新对下一个地址进行寻址,而是直接进行操作。

A3:设置突发的类型,连续型和非连续型。

A4~A6:指定潜伏期的长度,可以选择延时2,3两个周期。

A9:用来指定操作模式。

03 SDRAM容量计算

SDRAM总存储容量 =行数×列数×L-Bank的数量×存储单元的容量

Row Address : A0~A11

Column Address : A0-A8

Bank = 4

Data Width=16bit

Capacity=212x 29x 4bank x 16bit=128Mbit

04 SDRAM上电初始化过程

1、VDD (供输入buffer和逻辑电路)和VDDQ(供输出buffer)上电,此期间CKE保持低电平。2、开始时钟并使CKE置高。

3、电源、时钟都稳定后,再等待200uS。

4、发出预充电命令。

5、发出多个 (8个以上) 刷新命令 (REF)。

6、发出模式寄存器设置命令 (MRS),初始化模式寄存器 (DDR2 中还有EMRS,进行ODT.OCD等功能的设置和调整)。

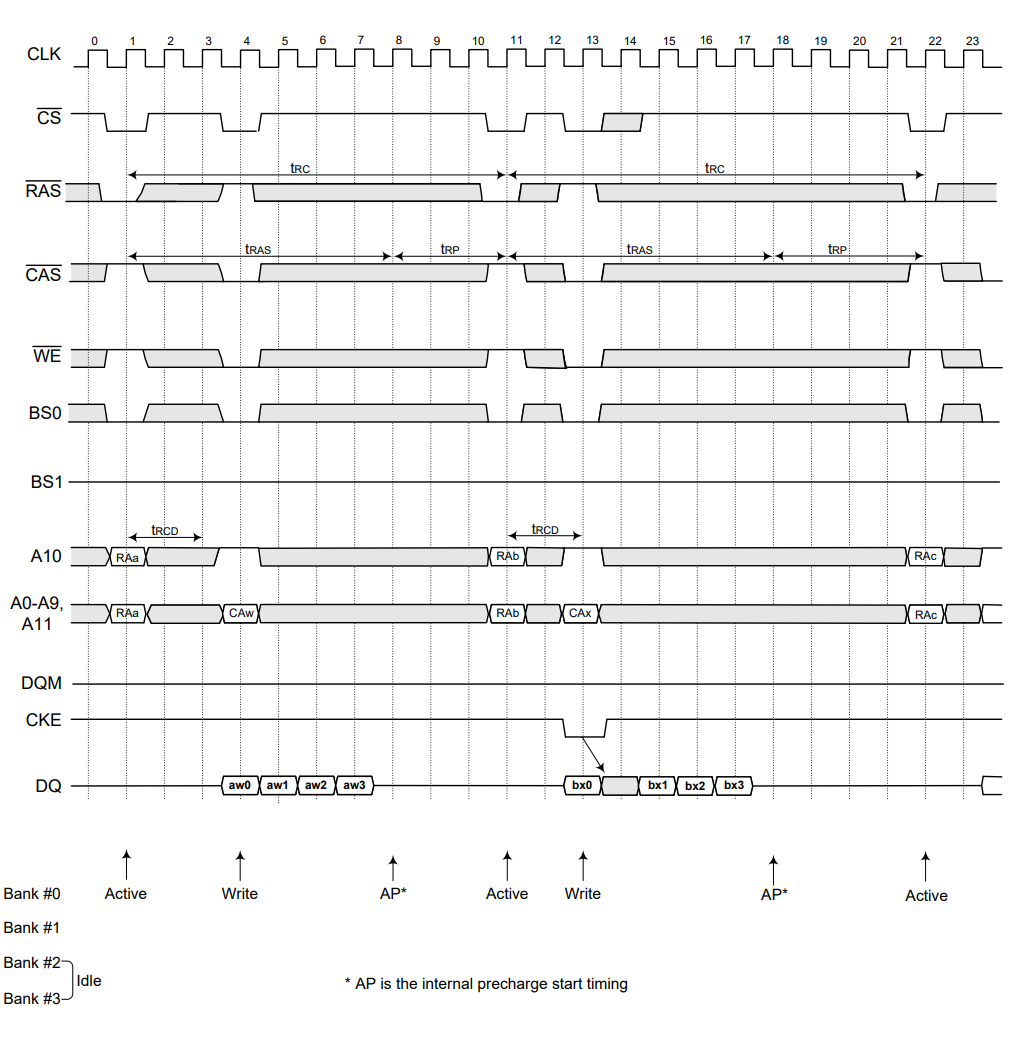

05 SDRAM 读写时序

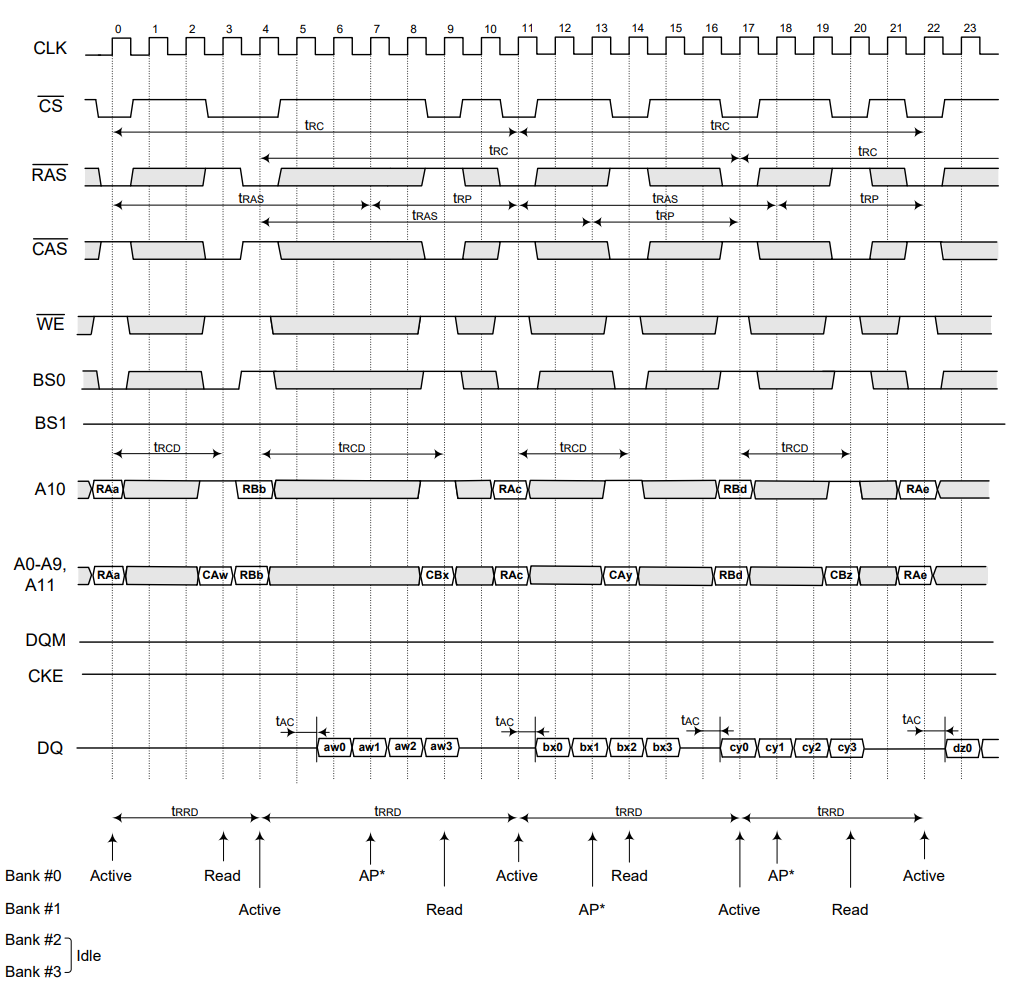

这里从SDRAM手册截取读时序进行分析,这里需要参考下图的操作命令具体值与时序图一起分析。

1.读时序(Burst Length = 4, CAS Latency = 3, Auto-Precharge))

读取数据过程:

1)发送激活命令,设置行地址和Bank地址。

2)设置列地址,发送读命令。

3)将A10地址线拉高,自动预充电使能。

4)开始执行预充电。

5) 完成数据读取。

2.写时序(Auto-Precharge Write,Burst Length = 4)

写过程跟读取类似:

1)发送激活命令,设置行地址和Bank地址。

2)设置列地址,发送写命令。

3)将A10地址线拉高,自动预充电使能

4)开始执行预充电。

5) 完成数据写入。

-

芯片

+关注

关注

458文章

51435浏览量

428870 -

SDRAM

+关注

关注

7文章

434浏览量

55459 -

寄存器

+关注

关注

31文章

5387浏览量

121592

原文标题:芯课堂|SDRAM工作原理及时序分析

文章出处:【微信号:gh_ed4f95bde4df,微信公众号:华芯微特32位MCU】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

时序分析总结(以SDRAM时序约束为例)

PDP4218三星V3屏电源工作原理及时序

SDRAM的原理和时序

SDRAM的工作原理

基于DDR SDRAM控制器时序分析的模型

关于SDRAM的时序控制研究方案分析

一种基于FPGA的SDRAM设计与逻辑时序分析

SDRAM工作原理及时序分析

SDRAM工作原理及时序分析

评论