在systemverilog协议中,logic定义四态值,即向量(vector)的每个位(bit)可以是逻辑0, 1, Z或X,与verilog协议中的reg很接近。但是logic有个很明显的优势,不允许多驱动。

多驱动对关键字logic而言是语法错误,在VCS编译阶段就能够发现,能够更早得发现错误。

而在Verilog协议中,并没有强调reg是不允许多驱的,因此VCS等编译工具不会主动报错。

需要在spyglass lint才能检查出来,或者通过VCS 仿真发现。

在芯片设计中,更早的暴露问题一直是设计和验证人员追求的目标,因此在RTL编码时,如果正常设计是不允许多驱动的场景中,建议使用logic替代reg。

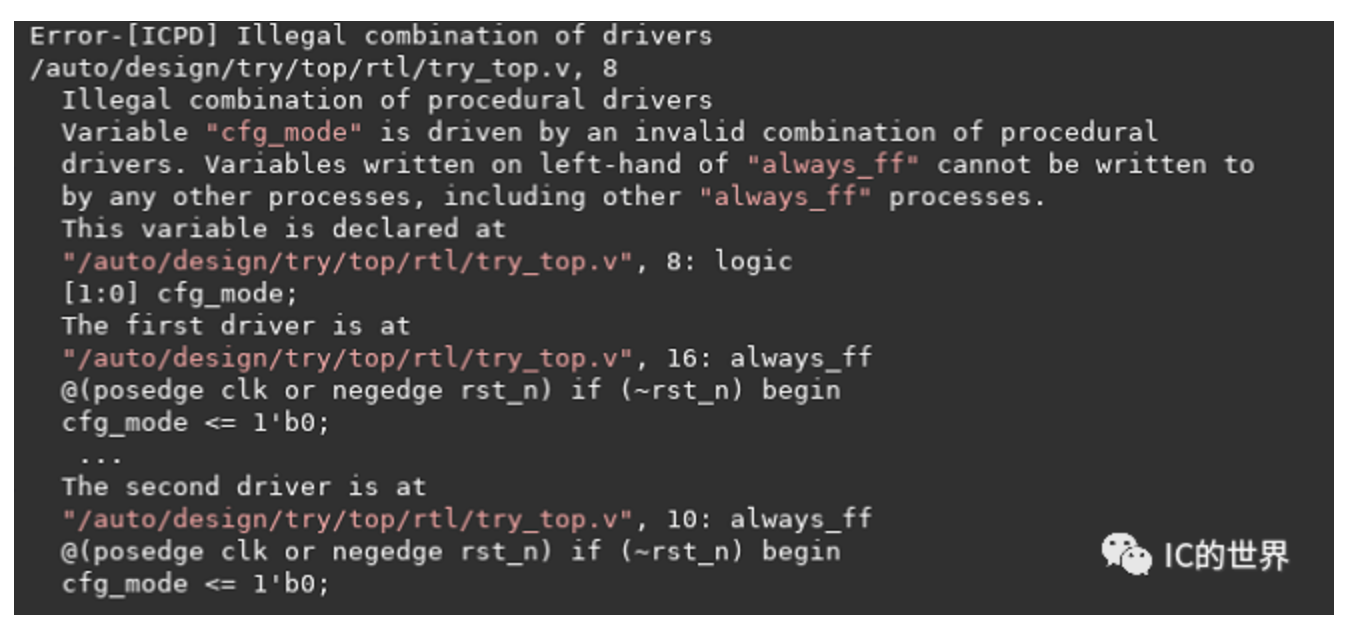

如下案例中:cfg_mode 被多驱动,在实际项目设计中,多驱动的问题往往更加隐蔽,更不容易发现。

module try_top (

input clk , //

input rst_n , //

input [1:0] cfg_mode_in //

);

logic [1:0] cfg_mode ;

always_ff@(posedge clk, negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

always_ff@(posedge clk, negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

endmodule

VCS报错:

如下案例中:cfg_mode 被多驱动,但是申明成reg类型,因此VCS不会报ERROR。

module try_top (

input clk , //

input rst_n , //

input [1:0] cfg_mode_in //

);

reg [1:0] cfg_mode ;

always@(posedge clk or negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

always@(posedge clk or negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

endmodule

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

驱动器

+关注

关注

53文章

8332浏览量

147332 -

仿真器

+关注

关注

14文章

1019浏览量

84007 -

RTL

+关注

关注

1文章

386浏览量

60061 -

VCS

+关注

关注

0文章

80浏览量

9667 -

Verilog语言

+关注

关注

0文章

113浏览量

8315

发布评论请先 登录

相关推荐

SystemVerilog学习一 —— 计数器

本帖最后由 鼻子抽筋 于 2012-2-21 15:41 编辑

SystemVerilog给予Verilog、VHDL和C/C++优点为一身的硬件描述语言,很值得学一学。1、8-bit up

发表于 02-21 15:39

[启芯公开课] SystemVerilog for Verification

学快速发展,这些趋势你了解吗?SystemVerilog + VM是目前的主流,在未来也将被大量采用,这些语言和方法学,你熟练掌握了吗?对SoC芯片设计验证感兴趣的朋友,可以关注启芯工作室推出的SoC芯片

发表于 06-10 09:25

是否有更好的方法来存储比reg [100,000:0] val更有效的大值

我对xilinx和verilog有些新意。对于我正在研究的程序,我需要一个非常大的寄存器。 (大约100,000位)当我尝试编译时,需要很长时间,我想知道是否有更好的方法来存储比reg

发表于 02-15 13:41

使用SystemVerilog来简化FPGA中接口的连接方式

的一小部分,入门也很快,因此建议FPGA工程师学一下SystemVerilog。 本文中用到的logic关键字的解释可以参考SystemVerilog教程之数据类型1 此次例程也比较简单,有两个模块

发表于 01-08 17:23

噪声频谱密度(NSD)比信噪比(SNR)更有用?

大家有木有发现,在比较在不同速度下工作的系统、或者查看软件定义系统如何处理不同带宽的信号时,噪声频谱密度(NSD)可以说比信噪比(SNR)更为有用。虽然它不能取代其他规格,但会是分析工具箱中的一个有用参数指标。难道真的噪声频谱密度(NSD)比信噪比(SNR)

发表于 03-05 08:17

SystemVerilog Assertion Handbo

SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

发表于 07-22 14:08

•188次下载

SystemVerilog的断言手册

SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

发表于 07-22 14:12

•20次下载

SystemVerilog 3.1a Language Re

Section 1 Introduction to SystemVerilog ..... 1Section 2 Literal Values... 42.1 Introduction

发表于 07-22 14:18

•39次下载

SystemVerilog的正式验证和混合验证

手册的这一部分探讨了使用SystemVerilog进行验证,然后查看了使用SystemVerilog的优点和缺点。

发表于 03-29 10:32

•24次下载

SystemVerilog在硬件设计部分有哪些优势

谈到SystemVerilog,很多工程师都认为SystemVerilog仅仅是一门验证语言,事实上不只如此。传统的Verilog和VHDL被称为HDL(Hardware Description

systemverilog:logic比reg更有优势

在systemverilog协议中,logic定义四态值,即向量(vector)的每个位(bit)可以是逻辑0, 1, Z或X,与verilog协议中的reg很接近。但是logic有个

SystemVerilog相比于Verilog的优势

我们再从对可综合代码的支持角度看看SystemVerilog相比于Verilog的优势。针对硬件设计,SystemVerilog引入了三种进程always_ff,always_comb

systemverilog:logic比reg更有优势?

systemverilog:logic比reg更有优势?

评论