高VDS尖峰可能会导致MOSFET雪崩,进而导致器件性能下降和可靠性问题···

电源行业的主要目标之一是为数据中心和5G等应用中的电源设备带来更高的电源转换效率和功率密度。与具有单独驱动器IC的传统分立MOSFET相比,将驱动器电路和功率MOSFET(称为DrMOS)集成到IC中可提高功率密度和效率。

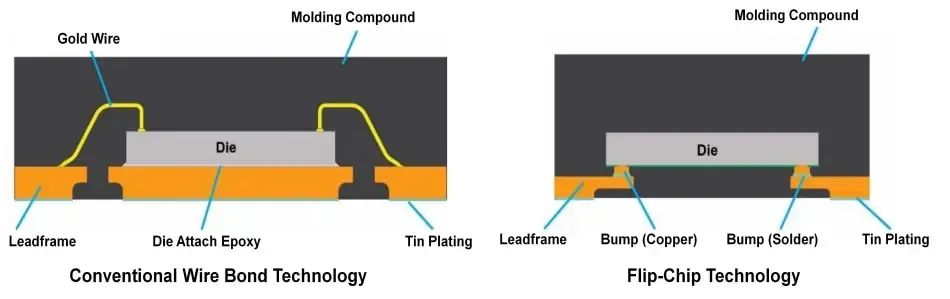

此外,DrMOS的倒装芯片技术通过缩短响应时间和减小芯片与封装之间的电感,进一步优化了稳压器的性能(图1)。

图1 这是传统接合线和倒装芯片技术之间的比较。资料来源:Monolithic Power Systems

然而,基板和PCB上的寄生电感会对漏-源极电压(VDS)尖峰产生重大影响,这是由于寄生电感与MOSFET输出电容(COSS)之间的谐振造成的。高VDS尖峰可能会导致MOSFET雪崩,进而导致器件性能下降和可靠性问题。为了防止MOSFET发生雪崩击穿,有多种方法可以减轻电压应力。

第一种方法是在DrMOS上应用更高电压的双扩散MOSFET(DMOS)工艺。如果在功率MOSFET设计中采用此工艺,由于同一空间内并联DMOS的数量减少,DrMOS的导通电阻(RDS(ON))会更高。

第二种方法是使用缓冲电路来抑制电压尖峰。然而,这种方法会导致缓冲电路产生额外的损耗。此外,添加缓冲电路可能无法有效降低MOSFET的VDS尖峰,因为引起谐振行为的杂散电感主要集成在DrMOS的封装中。

当尝试提高稳压器效率并减少MOSFET的电压尖峰时,上述权衡的方法可能会导致难以量化和优化寄生电感对PCB和基板的影响。

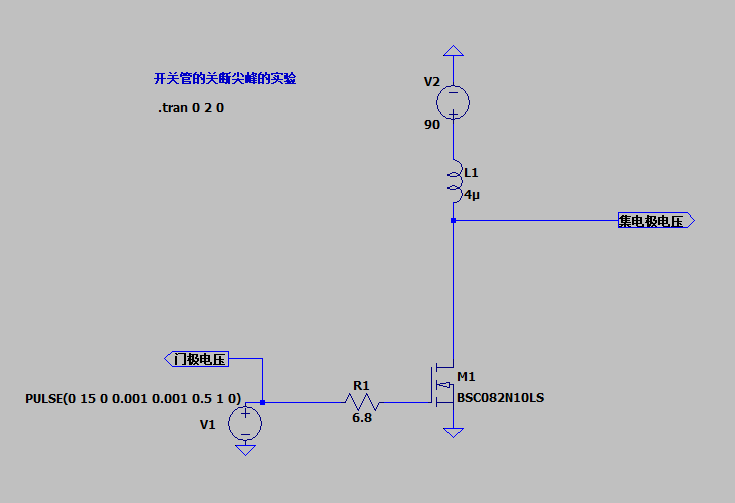

本文将首先讨论寄生电感的建模。接下来,在SPICE仿真工具中应用等效寄生电路模型来预测VDS开关尖峰。实验结果将用于验证寄生模型的可行性。

DrMOS上的寄生电感建模

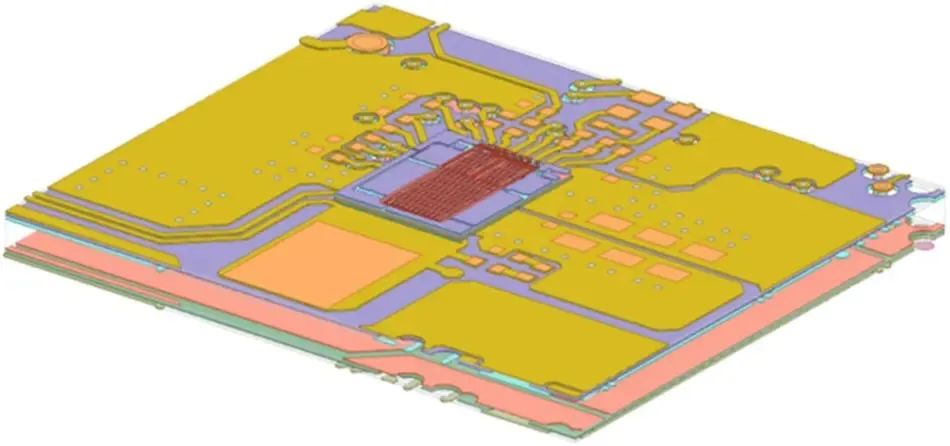

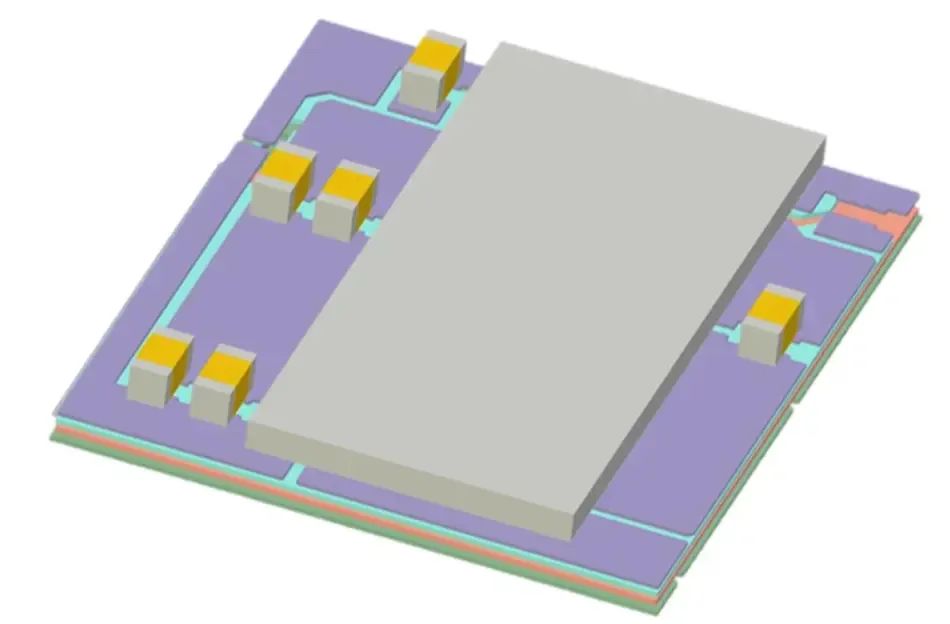

为了模拟寄生电感,我们构建了DrMOS和PCB的3D结构以进行仿真分析(图2)。材料、堆叠信息和PCB以及封装层厚度等参数对于建模准确性至关重要。

图2 DrMOS和PCB的3D建模结构可用于获取寄生电感。资料来源:Monolithic Power Systems

对PCB和DrMOS进行3D建模后,可以通过ANSYS Q3D提取器对寄生电感行表征和获取。由于本文重点关注MOSFET的VDS尖峰,因此主要的仿真设置是电源网络和驱动器网络上的寄生参数。

当考虑从Q3D提取器获得的寄生分量时,可以在不同频率条件下选择寄生电感矩阵(包括DrMOS上每个网络的自项和互项)。由于高侧MOSFET(HS-FET)和低侧MOSFET(LS-FET)上的VDS谐振频率在300MHz至500MHz之间,因此采用300MHz条件下的寄生电感矩阵进行进一步的行为模型仿真。

SPICE上的行为模型仿真

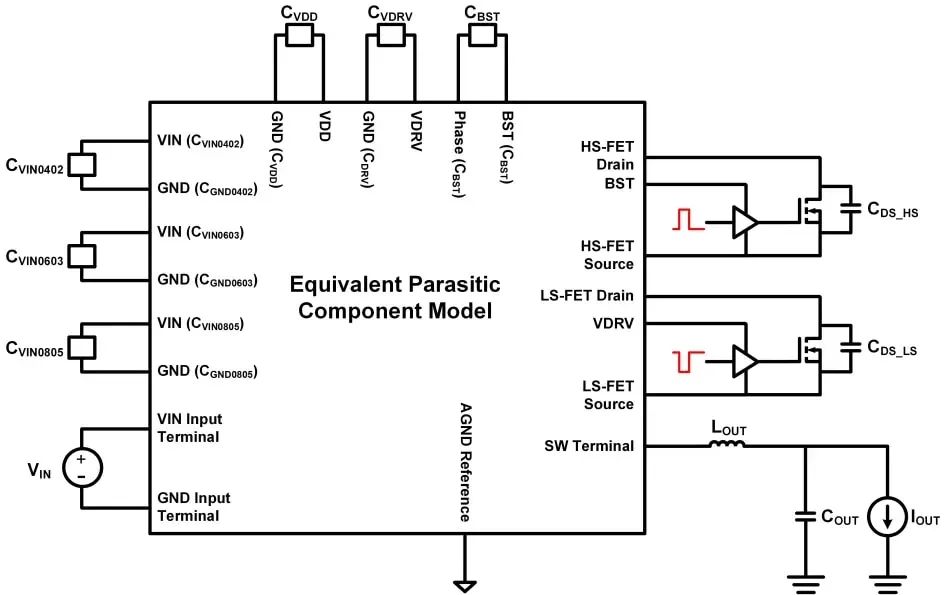

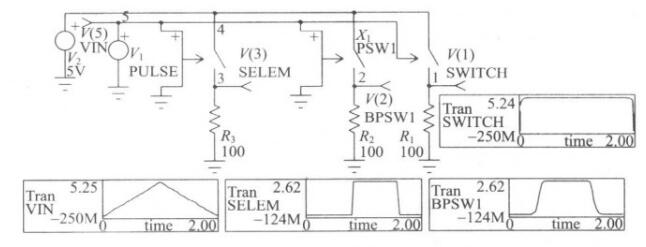

从Q3D导出等效寄生元件模型后,PCB上不同类型去耦电容的影响将被考虑在内。由于在多层陶瓷电容器(MLCC)上施加直流电压后电容会衰减,因此必须考虑每个MLCC在特定直流电压偏置条件下的等效电路。每个考虑因素都应基于MLCC的工作电压。图3显示了SPICE上行为模型仿真的电路配置。

图3 可以使用行为模型仿真来配置电路。资料来源:Monolithic Power Systems

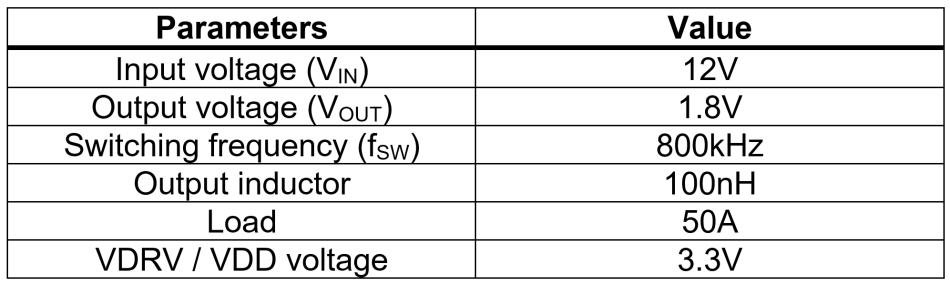

表1显示了基于图3所示原理图的仿真和测量条件。

表1 数据为实验测试台的结果。资料来源:Monolithic Power Systems

优化寄生电感

要在不影响效率的情况下抑制VDS尖峰,优化PCB和封装上的寄生电感至关重要。借助先进的封装技术,可以将输入电容器集成在封装中,以缩短去耦路径(图4)。在封装内并联嵌入式电容可以有效降低DrMOS上的等效寄生电感。

图4 具有嵌入式电容器的3D DrMOS结构优化了VDS尖峰。资料来源:Monolithic Power Systems

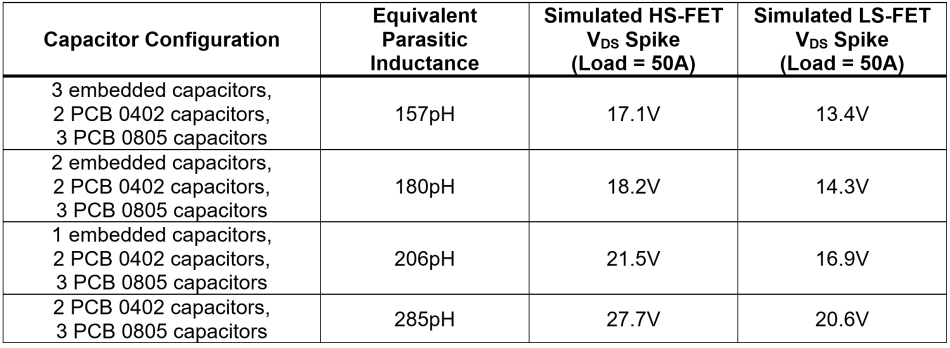

表2显示了在DrMOS上使用不同去耦电容器配置时的等效寄生电感和VDS尖峰。

表2 显示了不同电容器配置下的等效寄生电感和VDS尖峰。资料来源:Monolithic Power Systems

如表2中的仿真结果所示,不仅等效寄生电感降低,而且MOSFET上的VDS尖峰也得到抑制。此外,由于MLCC的低ESR特性,嵌入式输入电容器不会产生额外的功率损耗。因此,可以添加不同的嵌入式输入电容器来减少DrMOS应用中的寄生电感。

带有嵌入式电容器的DrMOS

本文解释了寄生电感对VDS开关尖峰的影响,以及防止VDS开关尖峰导致MOSFET雪崩击穿的几种方法。为了量化寄生电感对VDS开关尖峰的影响,首先引入了寄生电感建模,然后提出了SPICE上的行为建模。

通过SPICE获得的结果与MP87000-L等DrMOS解决方案的实验结果非常吻合,这意味着该行为模型可以准确预测MOSFET上发生雪崩击穿的风险。

为了有效抑制VDS尖峰而不需要任何权衡取舍,在封装中引入了嵌入式电容器。行为模型仿真证实,这些电容器可以降低等效寄生电感,从而降低VDS尖峰,而不会产生额外损耗。

审核编辑:刘清

-

MOSFET

+关注

关注

147文章

7192浏览量

213560 -

驱动器

+关注

关注

53文章

8255浏览量

146563 -

PCB板

+关注

关注

27文章

1448浏览量

51735 -

电源转换器

+关注

关注

4文章

317浏览量

34577 -

寄生电感

+关注

关注

1文章

156浏览量

14606

原文标题:怎么通过SPICE仿真来预测VDS开关尖峰?

文章出处:【微信号:PCB电子电路技术,微信公众号:PCB电子电路技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何在SPICE仿真工具中预测VDS开关尖峰呢?

如何在SPICE仿真工具中预测VDS开关尖峰呢?

评论