谈到package,用过VHDL的工程师并不陌生。实际上,SystemVerilog中的package正是从VHDL引入的,以进一步增强其在系统级的描述能力。我们来看一下SystemVerilog中package的使用方法与注意事项。 SystemVerilog中的package需要在关键字package和endpackage之间进行定义,其包含的内容可以是parameter,localparam,const,typedef,task,function,import,export和time unit。当然,package中也可以包含一些不可综合的用于验证的内容如class。

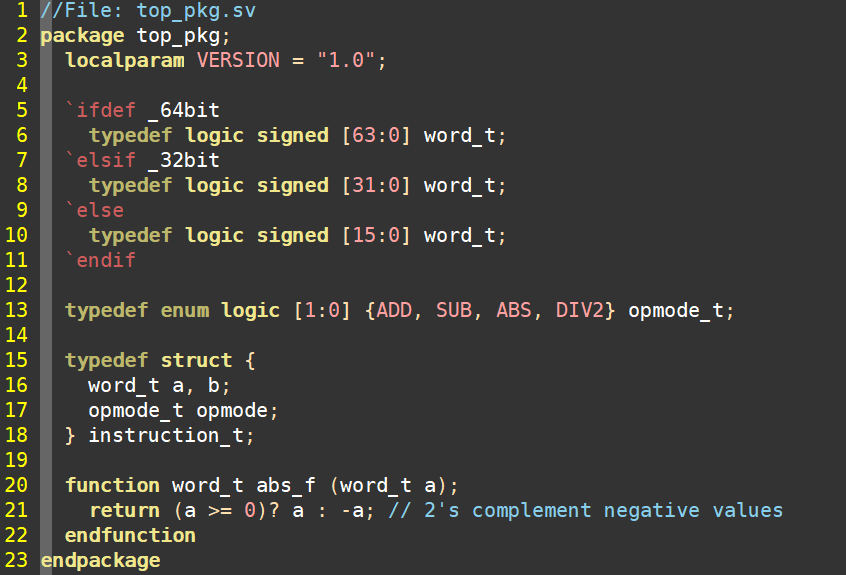

我们来看一个具体的例子,如下图所示代码片段。代码第2行通过关键字package表明其描述类别,package之后的top_pkg是package的名字。代码第5行至第11行以条件编译的方式结合typedef定义了数据类型。代码第13行通过typedef enum定义了枚举类型。代码第15行到第18行通过typedefstruct定义了结构体。代码第20行至第22行定义了function。代码第23行以endpackage确定package结束。

从可综合的SystemVerilog代码风格角度而言,需要注意:对于需要定义在package中的常数,应采用localparam或const定义,而不要使用parameter定义。此外,结构体应定义在package中,而不是以独立的.sv文件存在。

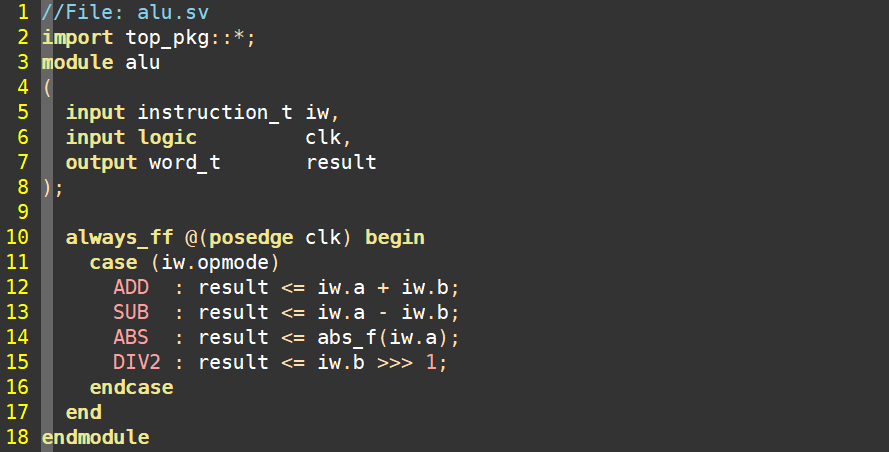

当需要使用package中的对象时,就需要导入package,如下图所示代码片段。代码第2行通过import导入package。“*”表示导入top_pkg中的所有内容。也可以只导入需要使用的package中的某个具体内容,例如

import top_pkg::word_t;

如果使用此方法导入用户定义的枚举类型时,需要明确导入使用到的枚举标签,如下所示:

import top_pkg::ADD;

import top_pkg::SUB;

import top_pkg::ABS;

import top_pkg::DIV2;

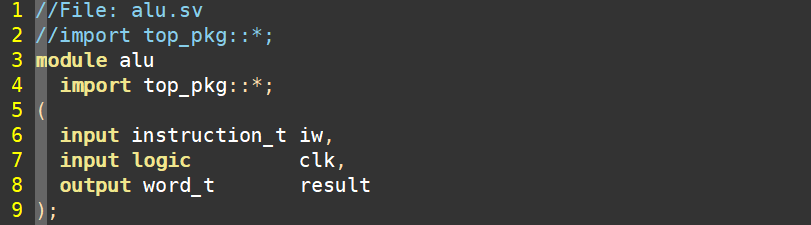

import package可以放在module声明之前,如上图所示代码第2行的位置,也可以放在端口声明之前,如下图所示代码片段的第4行。两者的效果是一样的,即:端口声明部分和module内的语句均可使用导入的package内容。

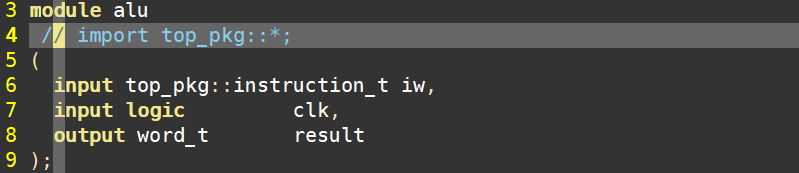

尽管可以使用如下图所示代码片段第6行所示方式,但实际工程中并不建议这么使用,这会导致代码变得冗长。工程实践表明,采用类似于“importtop_pkg::*;”的方式更为方便,也更为明了。

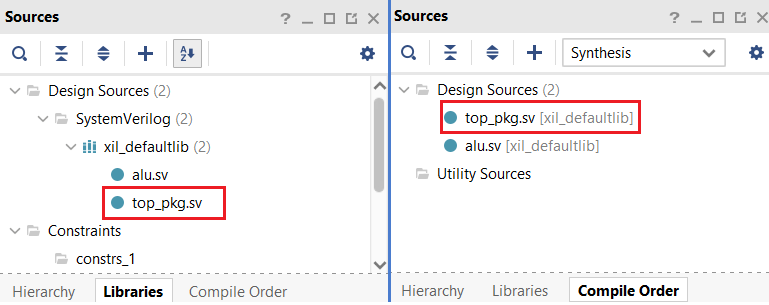

Vivado是支持package的。只需将package单独定义在一个后缀为.sv的文件中即可。Vivado会自动将package放在首位进行编译,如下图所示。

审核编辑:刘清

-

Vivado

+关注

关注

19文章

860浏览量

71491 -

Verilog语言

+关注

关注

0文章

113浏览量

8833 -

sub

+关注

关注

0文章

15浏览量

2983

原文标题:说说SystemVerilog的Package

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

信号发生器的使用方法及注意事项

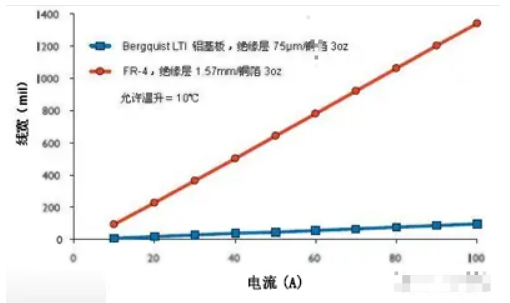

PCB承载大电流的操作方法和注意事项

看一下SystemVerilog中package的使用方法与注意事项

看一下SystemVerilog中package的使用方法与注意事项

评论