Cu-Clip技术

在上篇讨论TPAK封装时,我们聊到了Cu-Clip技术,当然它可以应用在很多模块封装形式当中。当时,我们简单地说了一些它的特点,降低寄生电感和电阻,增加载流能力,相应地提高可靠性,以及其灵活的形状设计。在芯片面积越来越小(比如IGBT 7 和SiC),这限制了常规绑定线的数量,但Cu-Clip技术相应地缓解了这方面的问题。

上面是绑定线和Cu-Clip的简单示意图。

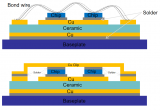

功率半导体器件结构可以分为好多层,其中影响长期可靠性的因素是CTE(热膨胀系数)的匹配,CTE失配而引起的应力对可靠性产生很大的影响,例如铝绑定线脱落就是其中较为典型的例子。这是由于铝绑定线和半导体材料之间CTE(铝:23ppm/K,Si:3ppm/K)差异较大导致的。而铜的CTE约为16.5ppm/K,相应地可以减轻CTE失配带来的热机械应力问题,同样又可以降低回路电感和电阻。

Cu clip粘接到其他表面的方式也有很多种,包括传统的焊接,银烧结以及铜烧结技术。当然这其中又牵扯到焊料,烧结工艺等,这些又都是复杂且不断发展的领域,所以任何事物都有着值得不断发展和迭代的过程,只是在一定的阶段,它受到市场需求,成本,技术等等因素的权衡。

就像绑定线有着材料、长度、直径、弯曲度等等因素的考量,Cu Clip也相应的会有厚度,材料,形状等等考量。今天我们就借着一篇论文来学习一下几个因素的影响趋势,其采用有限元仿真的方法来比较几个因素的影响,并且提出了新的Clip材料CMC(铜-钼-铜)。

Clip的厚度

采用AlN基板,三芯片(IGBT和FRD)并联,焊料采用SnAgCu,来比较Clip厚度0.5mm和1.5mm在一定温度差下的热机械应力,检测位置为Clip和芯片之间的焊接层,以及芯片表面。

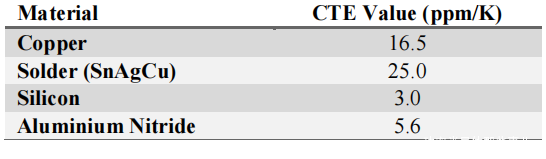

材料CTE的参数,

进行了归一化处理,我们可以看到,使用较薄的Clip,连接的位置应力会更小,但满足必要的载流能力的同时,尽量使用较薄的Clip。

应力缓解

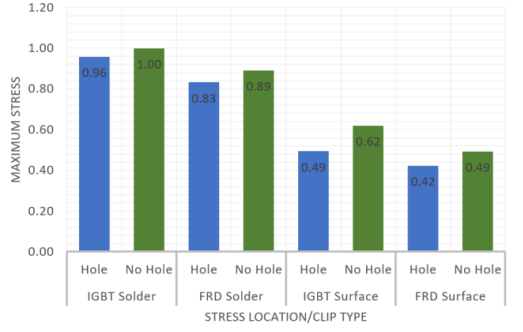

上面的模块图片中,我们可以看到Clip上有开孔,主要便是为了缓解应力,而相比于不开孔,应力具体会怎么样呢?从下面的仿真结果我们可以看到。

结果显然,可以通过开孔来缓解应力,但孔的形状大小和位置又有所考究,这需要我们结合实际来具体设计完善的。

Clip材料

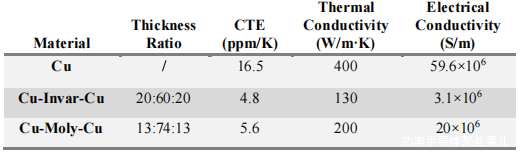

这里,作者提出了两种材料,一个上面说到的CMC,一个是CIC,Invar是一种镍铁合金,以低CTE而闻名,下面是它们的相关参数,

但是由于CIC的导电率较低,虽然CTE和Si更为接近,但是温升却很高,并不是一个理想的Clip材料,所以这里作者只比较了纯铜和CMC。

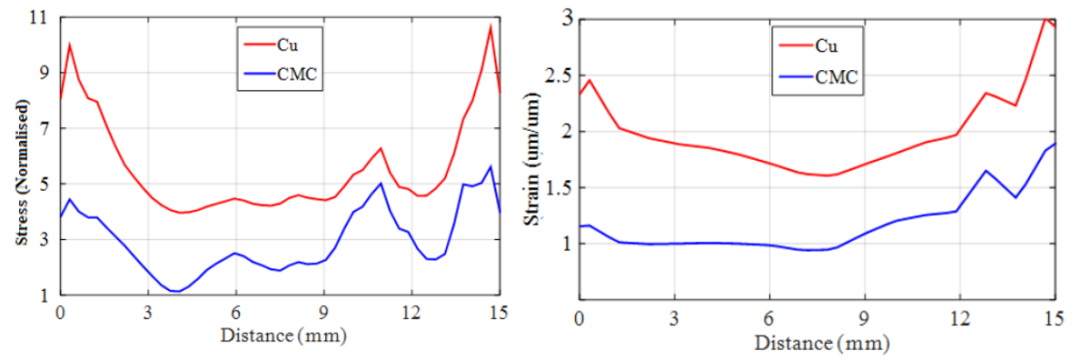

从相同芯片表面的应力和应变曲线来看,CMC由于和Si较小的CTE差异而产生更小的应力。同时我们可以看到最大的应力和应变出现在芯片边缘位置,所以又回到上一个问题,缓解应力的开孔放在和芯片接触的边缘位置会更好一些。

小结

今天我们又重新了解了关于Cu-Clip的一些细节,当然这也是我学习的一个过程,跟大家一起分享下。

审核编辑:刘清

-

IGBT

+关注

关注

1269文章

3846浏览量

250374 -

SiC

+关注

关注

30文章

2915浏览量

63065 -

寄生电感

+关注

关注

1文章

156浏览量

14634 -

功率半导体

+关注

关注

22文章

1194浏览量

43228 -

Clip

+关注

关注

0文章

31浏览量

6733

原文标题:车规模块系列(四):Cu-Clip互连技术

文章出处:【微信号:功率半导体那些事儿,微信公众号:功率半导体那些事儿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

OpenHarmony应用核心技术理念与需求机遇简析

DVB-H RF Tuner移动电视技术简析

直流和脉冲电镀Cu互连线的性能比较

EPON技术简析

简析BGA封装技术与质量控制

简析电源模块热设计注意事项资料下载

什么是 Cu clip 封装

Cu-Cu Hybrid Bonding技术在先进3D集成中的应用

车规模块系列(四):Cu-Clip互连技术简析

车规模块系列(四):Cu-Clip互连技术简析

评论