点击上方蓝字关注我们

本文提出了一种新的包括PCI9054单周期读、写和存储器映射传输的设计,并讨论了通用PCI总线高速数据采集卡的实现方案。

PCI总线(Peripheral Component Interconnect)是Intel公司推出的一种高性能32/64位局部总线,最大数据传输速率为132~264MB/s,是目前使用较为广泛的一种总线。在高速信号的实时处理中,利用PCI总线将采集数据直接传送到微机系统内存,可有效解决数据的实时传输和存储,为信号的实时处理提供方便。利用PCI总线进行高速数据采集,可以简化电路设计,而且这种高速数据采集接口模块可以在多次设计中重复使用,缩短产品的研发周期。在此通过对专用接口芯片PCI9054的性能分析,特别是对单周期读、写和存储器映射传输操作的时序进行了分析,提出了一种新的包括PCI9054单周期读、写和存储器映射传输的设计,并讨论了通用PCI总线高速数据采集卡的实现方案。

1 PCI9054性能简介

PCI9054是PLX公司推出的一种32位33 MHz的PCI总线控制器。它采用多种先进技术.可以将复杂的PCI接口应用设计变得简单。利用PCI9054灵活的局部总线可以方便地连接多种存储器、I/O外围设备和CPU,其中包括与Motorola公司的MPC860和Intel公司的960和IBM公司的PPC401等处理器之间的直接连接。PCI9054可广泛应用于Motorola公司的MPC 860适配器设计、Compact PCI热交换适配器设计、PCI总线主控适配器和嵌入式主机等设计系统中。PCI9054的本地总线时钟可与PCI总线时钟异步,本地总线有三种工作模式:M模式、C模式和J模式,可方便地与多种微处理器连接。其中,在C模式下,本地总线(Local Bus)为非复用的32 b地址与数据总线,时序与控制比较简单。PCI9054还有三种数据传送方式,即PCI主发起、PCI从目标、DMA方式。PCI从目标即PCI9054作为PCI总线的从设备,由总线上的其他主设备向它传送数据;在PCI9054的本地总线端,PCI9054又作为主设备,向本地的存储空间和I/O空间传送数据。在设计本地总线的数据传送接口时,主要有两项工作,一是需要对PCI空间到本地空间,或本地空间到PCI空间的地址映射,进行相应的存储器配置;二是根据PCI9054提供的本地总线控制信号设计本地总线的逻辑控制功能,实现相应的数据传送时序。

2 数据采集卡PCI接口电路设计

PCI总线规范定义了严格的电气特性和时序要求,它要求在接口卡和终端设备之间有一个总线接口控制器,采用某些公司提供的专用接口芯片,如PLX公司的PCI9080,PCI9054和AMCC公司的S5933,S5920等。使用它只需要设计用户接口逻辑和配置电路。大大减少了开发人员的工作量,且功能强,使用灵活。

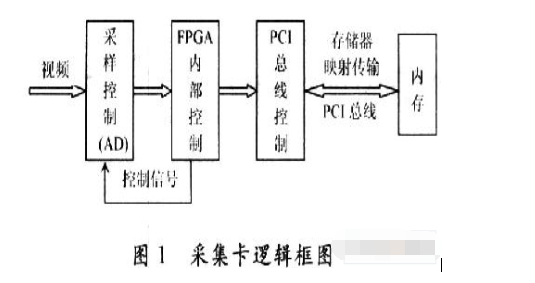

该设计采用PCI9054+FPGA实现高速数据传输接口。PCI9054能实现复杂的PCI总线规范2.2版,支持重要产品数据(VPD)配置,支持双地址周期,可编程中断生成,可编程突发管理,存储器映射传输,具有可选的串行E2PROM接口,并支持Compact PCI和热交换功能,性能卓越,使用方便。FPGA用来配合PCI9054的Local总线控制信号,实现Local总线端的数据传送。E2PROM接口直接连接一个E2PROM来初始化配置PCI9054。整个板卡的逻辑结构框图如图1所示。

2.1 FPGA内部控制

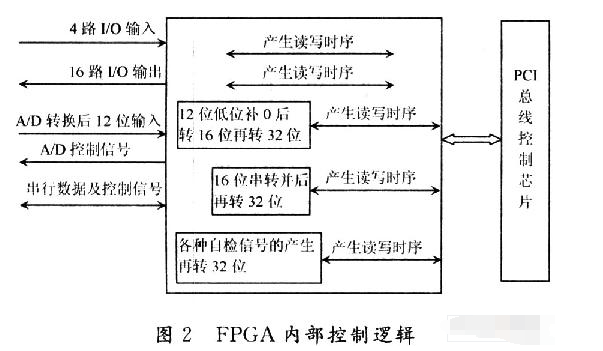

采样控制电路主要完成视频信号和动目标信号采样,并对采样值进行处理。设计的FPGA采用Altera公司的FLEX系列中的EPF1OK20芯片,并采用该公司与之配套的配置设备EPC2芯片来完成采样后的数据处理。在FPGA内部,根据由网络传过来高低、方位及自定义的差分信号传送时钟、串行帧同步、串行数据、模式字,对采样数据进行相关处理和小目标的放大。当信号小于一定值,则认为没有信号;信号值落在某一区间,为了观察方便要将其放大。FPGA同时完成各种自检信号的产生、A/D的控制信号、以及各种读写时序。Local总线与外部的I/O部分,用锁存器(如74F574)接口数据通路,用双向通路(如74LS245)接口控制信号线。具体框图如图2所示。

2.2 存储器映射传输

基于PCI9054的存储器映射传输是核心部分。根据配置寄存器配置的Local总线三个空间的大小以及三个空间的基地址,把数据写到相应的存储空间。计算机操作系统识别板卡正确后,自动分配存储空间给本卡,应用软件应用计算机自动分配的存储空间进行编程,完成所需要的功能。REQ,GNT,LHOLD,LHOL-DA为PCI BUS和LocaI BUS的仲裁信号,IRDY和TRDY分别为主设备准备好信号和从设备准备好信号,当两者同时有效时,才能真正进行数据传输。板卡复位或上电时,PCI9054自动装载E2PROM中的配置信息,同时EPC2自动配置EPF10K20,即装载程序入FP-GA。芯片PCI9054已经整合了PCI协议,实现了PCI总线的接口。整个板卡设计的关键工作就在于FPGA程序的设计、PCI9054的配置和板卡驱动程序的编写。PCI9054的正确配置是其正常工作的关键,PC操作系统在开机扫描总线时,正确的配置信息使操作系统正确识别板卡,并提示安装驱动程序。如果配置不正确或不完整,则操作系统将找不到板卡,并且可能死机。单靠硬件无法将数据送到内存供显示读数设备所用,设备驱动程序是连接到板卡的软件接口。该设计中,设备驱动程序的基本功能就是完成设备的初始化,对端口的读写操作,对中断的设置、响应和调用,以及对内存和接口设备存储器空间的直接读写。这里选用的驱动程序开发工具是Windrive。Windrive与DDK和VtoolsD相比,适应面比较窄,但是它主要针对ISA/PCI插卡,还包含一个代码生成器Windrive Wizward和针对于PCI9054的函数,所以开发比较简单,周期比较短。文献[4,5]在设计驱动程序之前,对欲控制的硬件设备进行了细致的分析,详细了解硬件设备的特性。硬件设备的特性对驱动程序设计会产生重大的影响。需要了解的最主要特性有:

设备的总线结构,该设计中即PCI总线;

寄存器,该设计中即配置的PCI9054寄存器的值;

设备的错误和状态,了解如何判断设备的状态和错误信号,通过驱动程序返回给用户程序;

中断行为,了解设备产生中断的条件和使用中断的数量;

数据传输机制,是I/O传输、DMA传输,还是存储器映射传输;

设备内存,RAM的容量,与系统总线(PCI)对应的基地址和范围。

3 寄存器配置

设计好接口连接,接口设计工作只完成了50%。由于PCI9054是通用PCI接口功能芯片,它的功能还不一定能够满足用户的需求,所以还要进行功能寄存器设置,以使接口电路具有特定的功能。寄存器的配置包括E2PROM初始化,以及Local功能寄存器和PCI配置寄存器的配置。

3.1 E2PROM初始化

在计算机的加电自检期间,PCI总线的RST信号复位,PCI9054内部寄存器的默认值作为回应。PCI9054输出本地LRESET信号并检测串行E2PROM。如果串行E2PROM中的前33个比特不全为1,那么PCI9054确定串行E2PROM为非空,用户可通过向9054的寄存器CNTRL的CNTRL29位写1来加载E2PROM的内容到PCI9054的内部寄存器,配置的信息(设备识别号,供应商代码号,Local总线三个空间的大小以及三个空间的基地址等)事先要利用编程写入配置寄存器中。

3.2 PCI配置寄存器的配置

配置PCI配置寄存器比较简单。主要是填写生产商ID号、器件ID号、类码子系统ID号和子系统生产商ID号。对于PCI9054,其生产商ID号为10B5,器件ID号为9054,子系统号ID为9054,子系统ID号为10B5,类码号为0680,表示其为桥设备中的其他桥设备类。

3.3 本地配置寄存器的配置

对于本地配置寄存器的配置就是对本地地址空间及其本地总线属性的配置。这些配置是根据实际开发的硬件板卡的硬件资源进行配置。设备人员配置寄存器的任务就是要把某一段本地地址应设为PCI地址。也就是当主机CPU要访问本地地址空间时,要知道其对应的PCI总线地址。

4 电路板实现与测试

PCI规范对扩展板的机械和电气方面都有一系列的规范要求。在布板和绘图的过程中需要特别注意一些技术要求,布出来的板子工作起来才会稳定可靠。如:除了PCI协议中的信号线外,连接器本身的信号引脚值得注意,如板卡存在信号PRSNT1和PRSNT2;电源的退耦、PCI协议信号线的走线长度限制和扩展板上信号线的负载要求等都是在布板过程中特别应该重视的,都要满足PCI电气规范的要求。

该设计中严格按照规范要求设计,PCI连接器上的PRSNT1而开路,PRSNT2接地,表示本板卡的最大功耗为15 W。元件的退耦电容采用0.1μF,电源的滤波电容采用10μF的电解电容。采用存储器映射的传输方式,本地时钟采用20 MHz时,通过测试,传输速率能够达到20 MB/s以上,提高本地时钟的频率,数据传输率还能够更高。

5 结 语

这里实现的PCI数据传输接口,有效地解决了系统的数据传输问题,有利于数据的实时处理,获得了比较满意的效果。随着信号处理技术的发展,这种基于PCI的数据传输接口有着十分广阔的应用前景。

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:基于PCI总线的雷达视频高速数据采集接口设计?

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1630文章

21761浏览量

604398

原文标题:基于PCI总线的雷达视频高速数据采集接口设计?

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

使用CAN总线进行数据采集的方法

PCIe接口的工作原理 PCIe与PCI的区别

通过PLX PCI9080桥接芯片实现TMS320C6000扩展总线与PCI总线的接口

高速分切机数据采集监控告警系统解决方案

YXC差分振荡器赋能数据采集卡,让数据更精准!

NI数据采集板卡如何连接使用?

多通道数据采集器的特点和功能有哪些

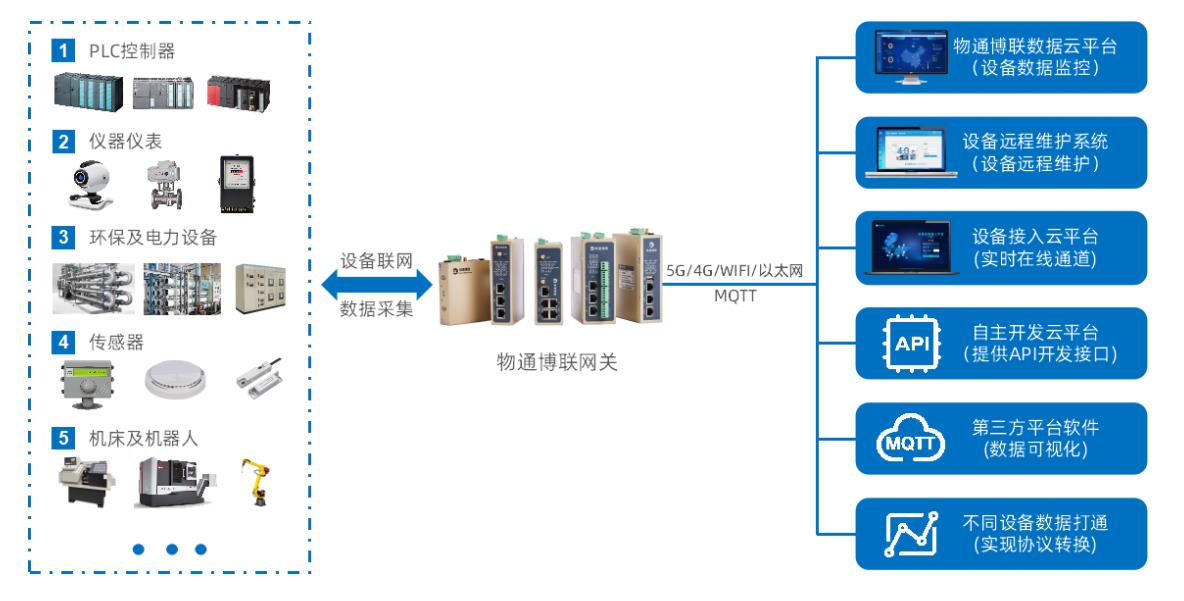

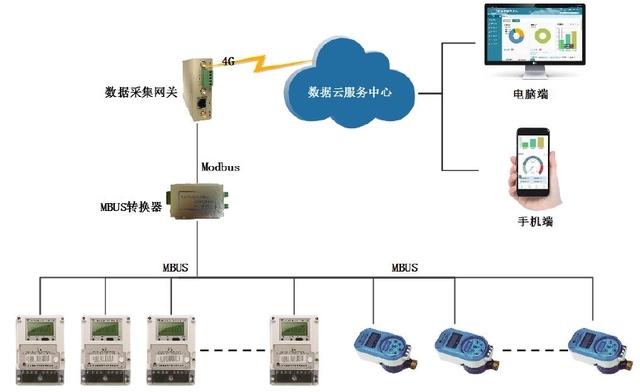

基于物通博联工业数据采集网关的工厂数据采集方案

基于PCI总线的雷达视频高速数据采集接口设计?

基于PCI总线的雷达视频高速数据采集接口设计?

评论