PLIC:Platform-Level Interrupt Controller.

实际上,除了CLINT管理的软件中断和定时器中断,其他的中断都是由PLIC管理的。

U54内核的平台级中断控制器 (PLIC) 最多可支持 132 个具有 7 个优先级的外部中断源。

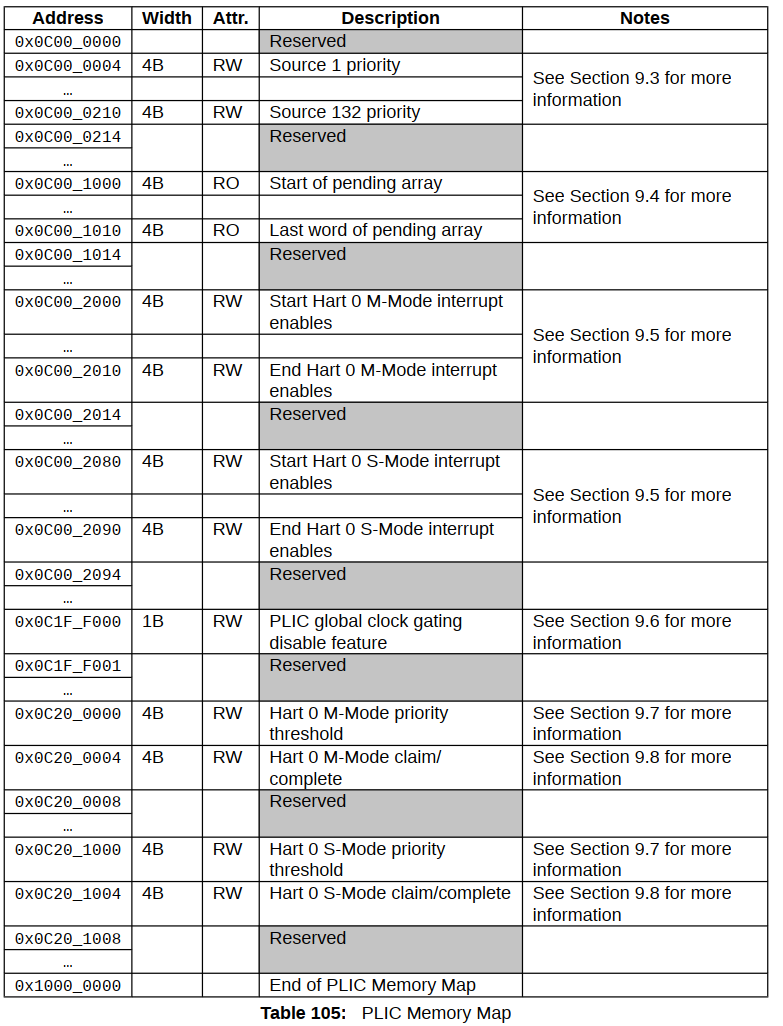

Memory Map

U54 内核 PLIC 控制寄存器的内存映射如表 105 所示。PLIC 内存映射仅支持对齐的 32 位内存访问。

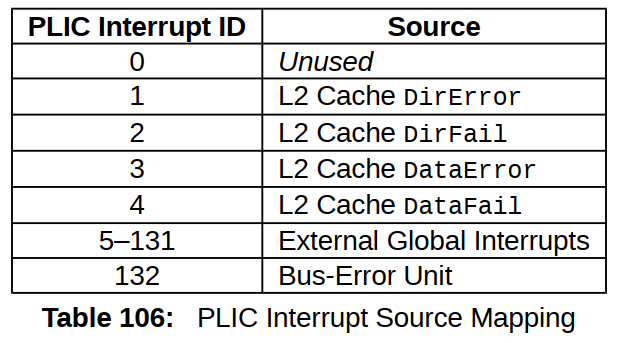

中断源

U54内核共有 132 个全局中断源,此外还有CLINT管理的 中描述的本地中断。

其中 127 个是外部全局中断,其余由表 106 中列出的各种片上设备驱动。表 106 描述了 U54 核心复合体上的全局中断源。

Note:在 RISC‑V 平台级中断控制器规范中,中断源 0 (ID 0) 未使用,因此第一个可用的 PLIC 中断 ID 的值为 1

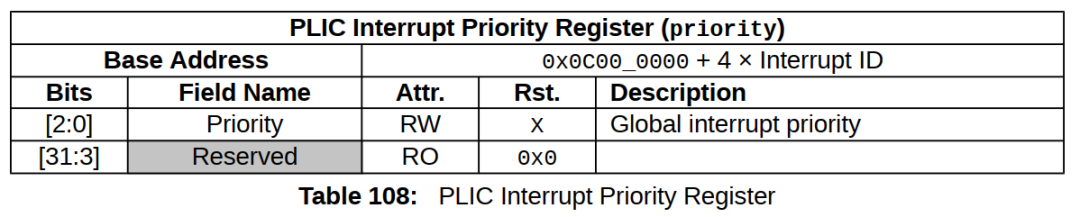

中断优先级

每个 PLIC 中断源都可以通过写入其 32 位内存映射优先级寄存器来分配优先级。

U54 内核支持 7 个优先级。保留优先级值 0 表示“永不中断”并有效地禁用中断。

优先级 1 是最低的活动优先级,优先级 7 是最高的。

相同优先级的全局中断之间的关系由中断 ID 打破;ID 最低的中断具有最高的有效优先级。相关寄存器信息如下:

-

内核

+关注

关注

3文章

1390浏览量

40574 -

RISC

+关注

关注

6文章

468浏览量

84084 -

sifive

+关注

关注

0文章

36浏览量

9486

发布评论请先 登录

相关推荐

psoc1中断控制器

在usart.c上增加配置NVIC优先级中断控制器

NVIC嵌套向量中断控制器介绍

简要介绍配置嵌套向量中断控制器

华芯微特MCU的嵌套向量中断控制器与外部中断/事件控制器的使用方法

中断控制器的驱动解析(上)

扒开 ARM 中断控制器的底裤

细说STM32的中断控制器(NVIC)那些事

PLIC平台级中断控制器介绍

PLIC平台级中断控制器介绍

评论