中断挂起位

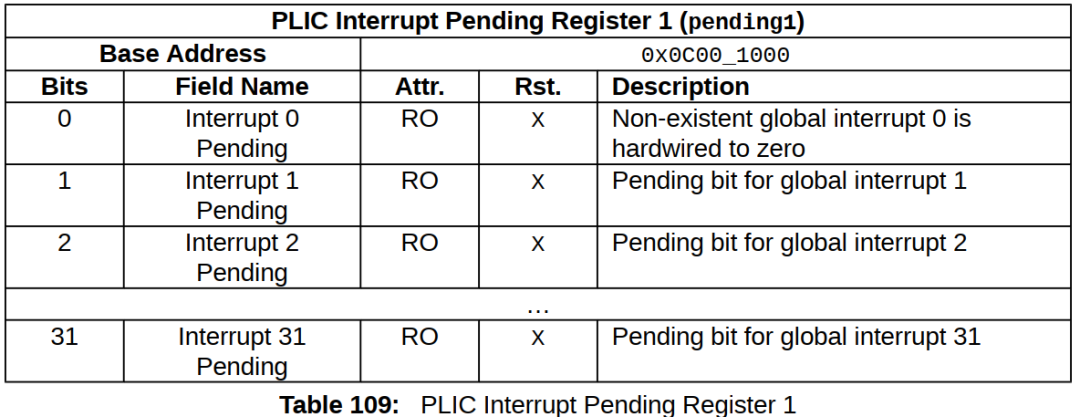

PLIC 内核中中断源挂起位的当前状态可以从挂起数组中读取,组织为 32 位的 5 个字。中断 ID 的挂起位存储在字的位中。

因此,U54 内核有 5 个中断挂起寄存器。表示不存在的中断源 0 的字 0 的位 0 硬接线为零。

PLIC 内核中的挂起位可以通过设置相关的启用位然后执行第 9.8 节中描述的声明来清除

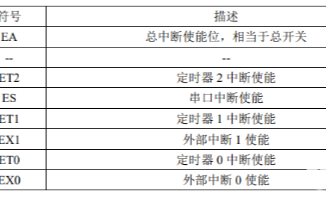

中断使能

每个全局中断都可以通过设置启用寄存器中的相应位来启用。使能寄存器作为 5 × 32 位字的连续数组进行访问,其打包方式与未决位相同。使能字 0 的位0 表示不存在的中断 ID 0,并硬接线为 0。

SiFive RV64 系统中的使能数组支持 64 位和 32 位字访问。

PLIC Clock Gate Disable

PLIC 实现时钟门控功能以在不活动时门控模块时钟节点。PLIC 时钟门控在复位后被禁用,应在启动代码中启用,除非 SiFive勘误表另有规定。一旦启用,时钟仅在 PLIC 控制总线上或任何中断线上有活动且相应中断未运行时才可用。

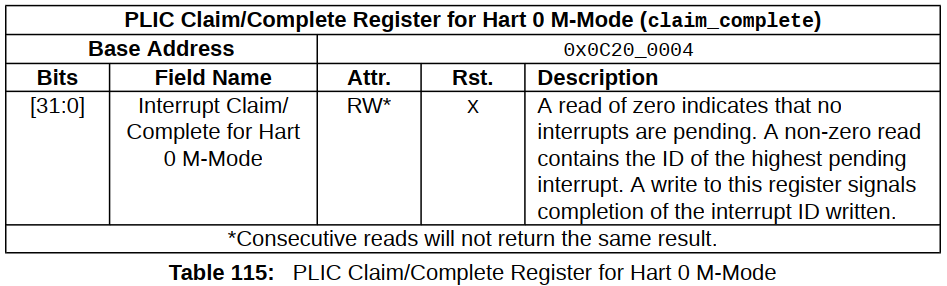

优先级阈值

U54 内核 支持通过阈值寄存器设置中断优先级阈值。阈值是一个WARL字段,其中U54 内核支持的最大阈值为7。

U54 核心复合体屏蔽优先级小于或等于阈值的所有 PLIC 中断。例如,阈值为零允许所有具有非零优先级的中断,而值为 7则屏蔽所有中断。如果阈值寄存器的值为 5,则不允许将优先级配置为从 1 到 5 的所有 PLIC 中断传播到 CPU。

-

内核

+关注

关注

3文章

1389浏览量

40546 -

中断

+关注

关注

5文章

900浏览量

41923 -

RISC

+关注

关注

6文章

468浏览量

84052 -

LIC技术

+关注

关注

0文章

2浏览量

5042 -

sifive

+关注

关注

0文章

36浏览量

9486

发布评论请先 登录

相关推荐

Linux内核中断设计与实现

stm32上的中断挂起和屏蔽与ARM内核中的挂起屏蔽是相同的吗?

Linux 2.4.x内核软中断机制

MSP430的中断

linux内核-时钟中断

STM32 中断原理及外部中断的实现

STM32自学笔记(二)中断

LIC内核中断挂起位和中断使能

LIC内核中断挂起位和中断使能

评论