中断

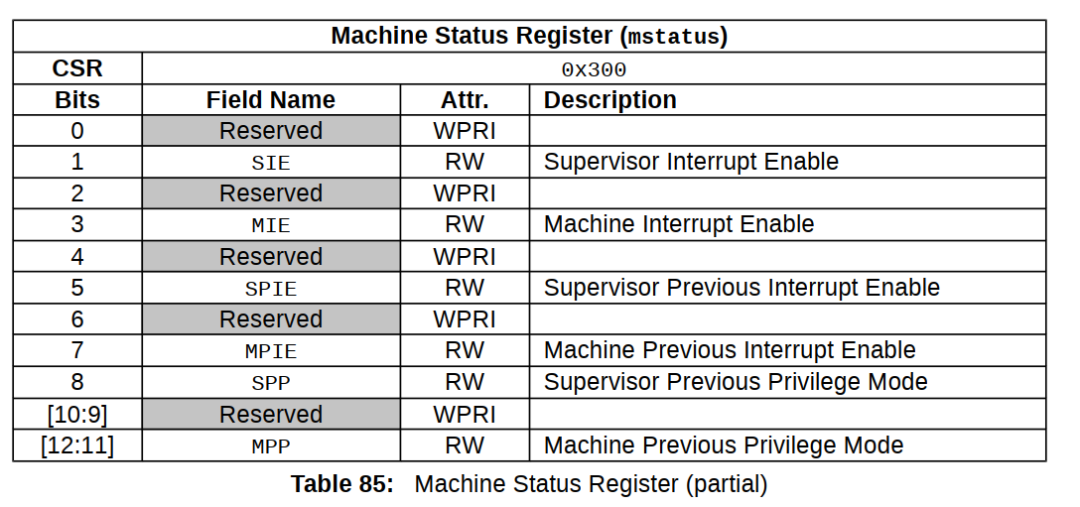

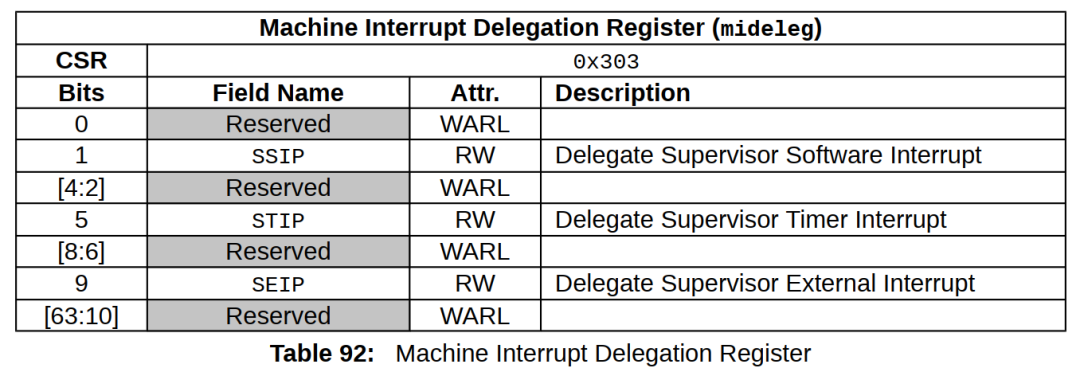

U54内核支持M模式和S模式中断。默认情况下,所有中断都在M模式下处理。对于支持S模式的 hart,可以有选择地将中断委托给S模式。

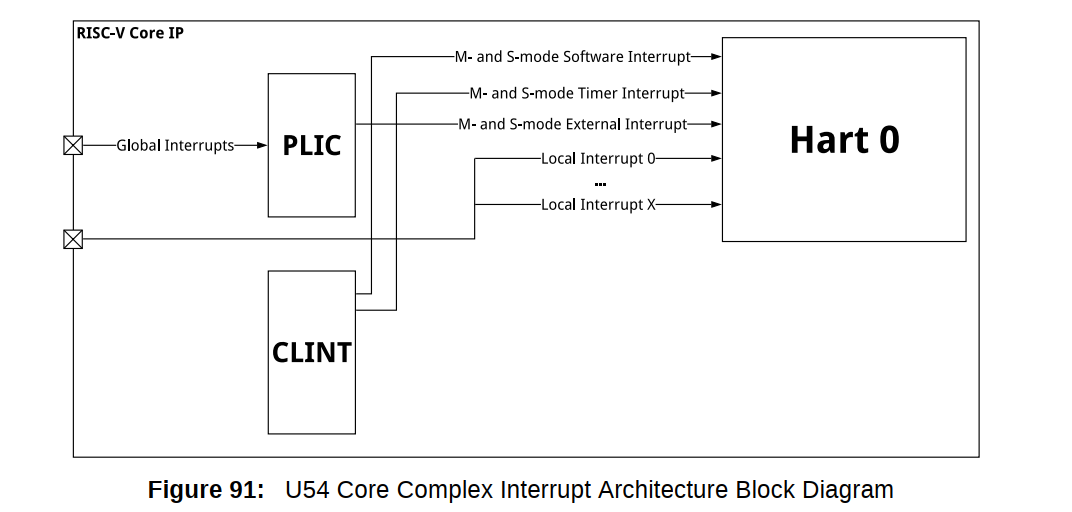

U54中断架构如下:

U54内核还支持两种类型的 RISC-V 中断:本地和全局。

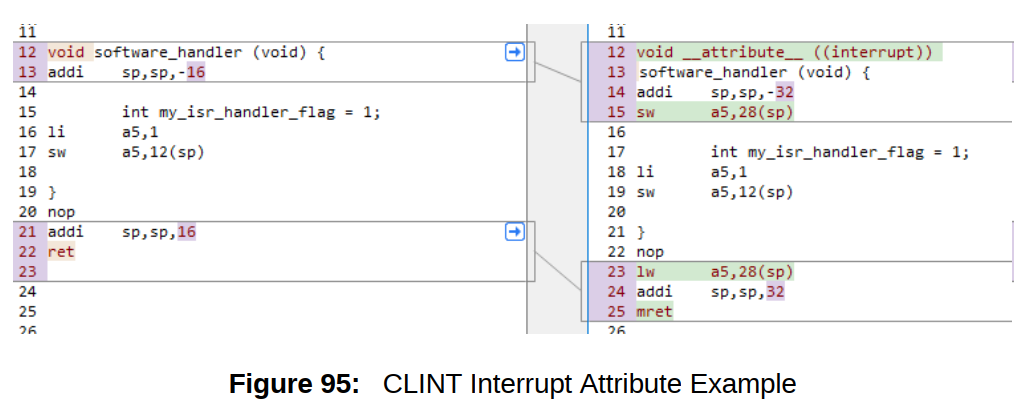

本地中断:U54内核的本地中断只有2种,软件中断和定时器中断,这两个中断都由本地中断器(CLINT)生成。本地中断通过专用中断异常代码和固定优先级直接发送给单个hart。因此,本地中断没有仲裁,也不需要额外的内存访问来确定中断的原因。

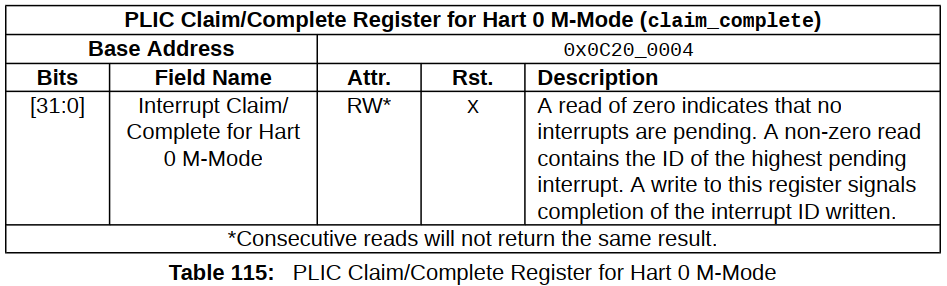

全局中断:通过平台级中断控制器 (PLIC) 路由,该控制器可以通过外部中断将中断定向到系统中的任何 hart。所有的外设都属于全局中断。

中断优先级

全局中断的各个优先级由 PLIC 确定。

U54内核的优先级如下,按优先级降序排列:

机器外部中断

机器软件中断

机器定时器中断

主管外部中断

主管软件中断

主管定时器中断

异常

如果一个 hart 在S模式下运行并尝试访问一个仅M模式的控制和状态寄存器 (CSR),这会立即进入异常处理程序并确定下一步行动。mstatus寄存器中的异常代码将保持值 0x2,表明发生了非法指令异常。根据系统的要求,监督模式应用程序可能会报告错误和/或完全终止程序。

没有特定的启用位来允许发生异常,因为默认情况下它们总是启用的。然而,在引导流程的早期,软件应该将 mtvec.BASE设置为一个定义的值,其中包含默认异常处理程序的基地址。所有异常都会捕获 tomtvec.BASE。软件必须读取 mcause CSR以确定异常的来源,并采取适当的措施。

在中断处理程序中发生的同步异常将立即导致程序执行中止中断处理程序并进入异常处理程序。中断处理程序中的异常通常是软件错误的结果,通常应该避免,因为mepc 和 mcause CSR 将被原始中断上下文中捕获的值覆盖。

RISC-V 定义的同步异常具有优先级顺序,当单个指令同时发生多个异常时,可能需要考虑优先级顺序。下表描述了同步异常优先级顺序。

数据地址断点(watchpoints)、指令地址断点、环境断点异常(EBREAK)都具有相同的异常码(3),但优先级不同,如上表所示。

指令地址未对齐异常 (0x0) 的优先级低于其他指令地址异常,因为它们是目标未对齐的控制流指令的结果,而不是取指的结果。

-

内核

+关注

关注

3文章

1372浏览量

40282 -

RISC

+关注

关注

6文章

462浏览量

83715 -

架构

+关注

关注

1文章

513浏览量

25468 -

sifive

+关注

关注

0文章

36浏览量

9458

发布评论请先 登录

相关推荐

三星将SiFive RISC-V内核用于SoC,汽车,5G应用

SiFive发布P870和X390,RISC-V架构内核性能暴涨

全球首款基于 RISC-V “HiFive Unleashed” 单板计算机(SBC)

可扩展的高性能RISC-V 内核IP

带有SiFive开发板和高性能CPU的RISC-V迈向主流

RISC-V是什么?有哪些优势

SiFive及晶心科技共同推展RISC-V_扩大RISC-V市占率

Sifive Learn Inventor基础之GPIO 按键中断 RISC-V

RISC-V掀开源风暴SiFive王者再临

U54内核PLIC中断处理例子

U54内核上CLINT的内存映射

U54内核中断控制和状态寄存器

RISC-V发展及FPGA厂商为什么选择RISC-V

RISC-V SiFive U54内核的中断介绍

RISC-V SiFive U54内核的中断介绍

评论