陷阱trap

术语陷阱描述了软件应用程序中的控制转移,其中陷阱处理通常在更特权的环境中执行。例如,一个特定的 hart包含三种权限模式:机器、管理员和用户。每种特权模式都有自己的软件执行环境,包括专用的堆栈区域。此外,每种特权模式都包含用于陷阱处理的单独控制和状态寄存器(CSR)。在用户模式下操作时,需要上下文切换来处理主管模式下的事件。软件为上下文切换设置系统,然后执行 ECALL 指令,将控制同步切换到Environment call-from-User 模式异常处理程序。

复位后的默认模式是机器模式。软件以最高权限级别开始执行,这允许在任何权限级别更改之前初始化所有 CSR和系统资源。下面的步骤描述了将特权模式从机器模式更改为用户模式所需的步骤,在特定设计上也包括管理员模式。

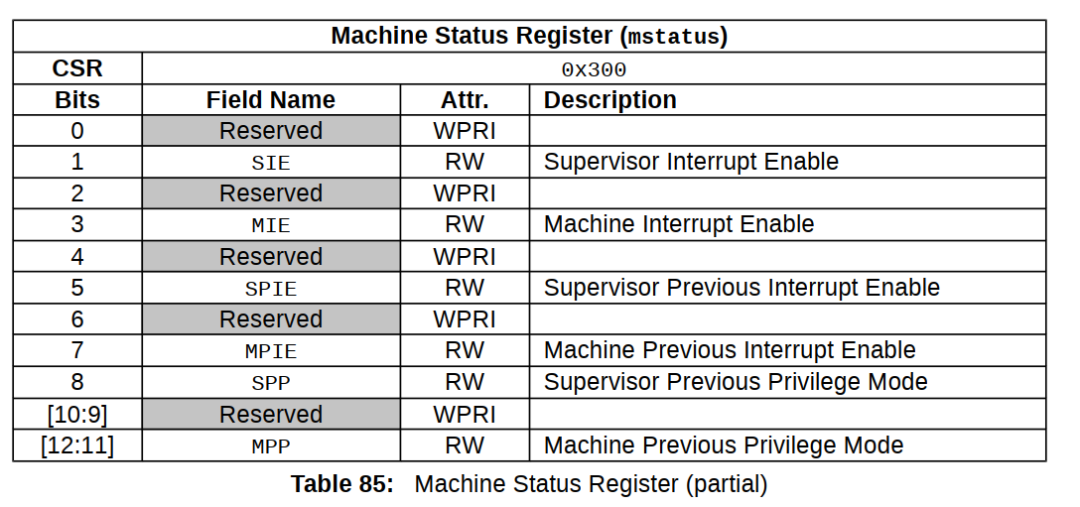

应首先通过将 mstatus.MIE 写入 0(默认复位值)来全局禁用中断。

将机器模式异常处理程序的基地址写入 mtvec CSR。这是任何引导流程中的必需步骤。

将 mstatus.MPP 写入 0 以将之前的模式设置为 User,这允许我们返回到该模式。

设置物理内存保护 (PMP) 区域以将所需区域授予用户和主管模式,并可选择从机器模式撤消权限。

用主管模式异常处理程序的基地址写入 stvec CSR。

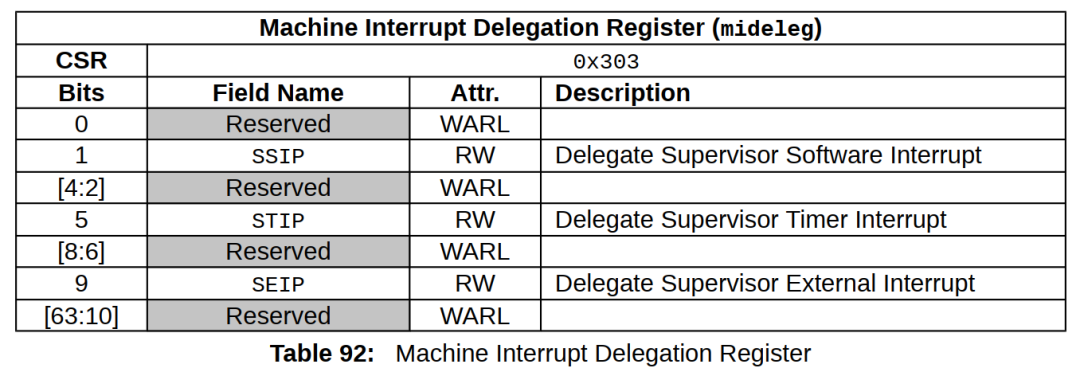

编写 medeleg 寄存器,将异常委托给主管模式。考虑 ECALL 和页面错误异常。

编写 mstatus.FS 以启用浮点(如果支持)。

将机器模式用户寄存器存储到堆栈或应用程序特定的帧指针。

用用户态软件的入口点编写mepc

执行mret指令进入用户模式。

Note:只有一组用户寄存器 (x1 - x31) 用于所有权限级别,因此应用软件负责在进入和退出不同级别时保存和恢复状态。

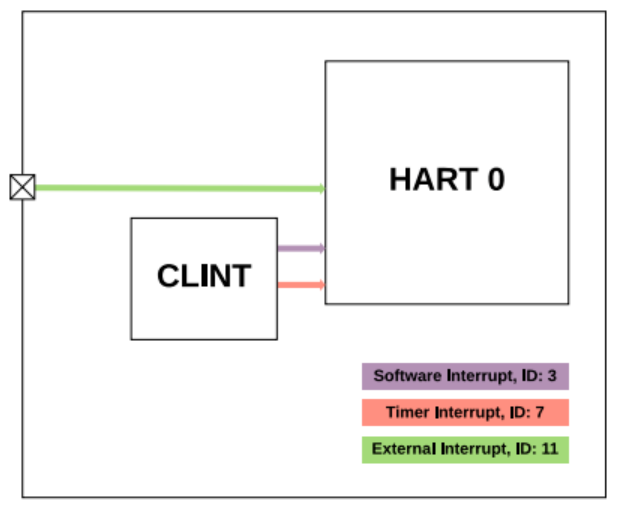

本地中断

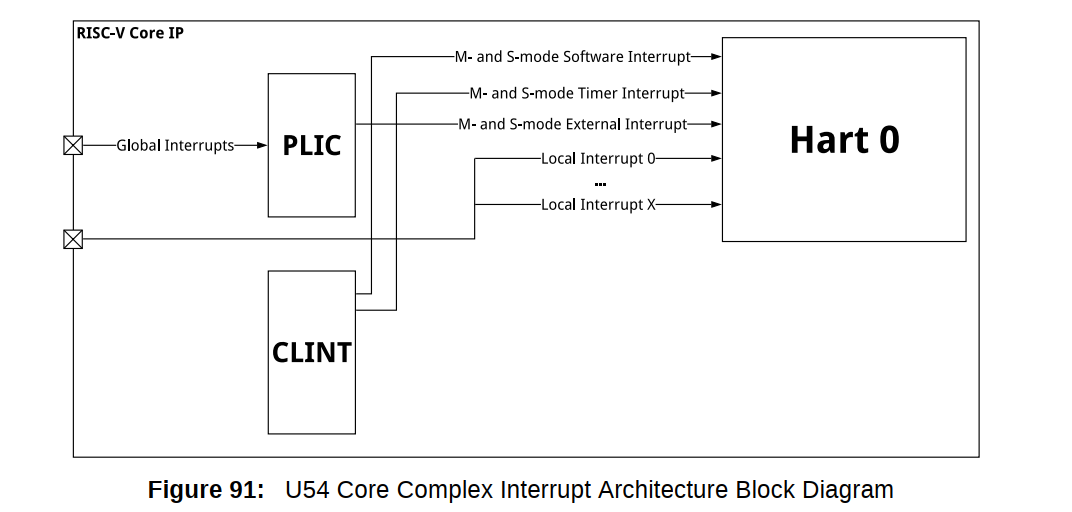

软件中断(中断 ID #3):通过写入特定 hart 的内存映射中断挂起寄存器 msip 来触发。

定时器中断:当寄存器 mtime 大于或等于寄存器 mtimecmp 并且两个寄存器都是 CLINT 内存映射的一部分时,会触发定时器中断(中断 ID#7)。mtime 和 mtimecmp 寄存器通常仅在机器模式下可用,除非 PMP 授予用户或管理员模式访问它们所在的内存映射区域的权限。

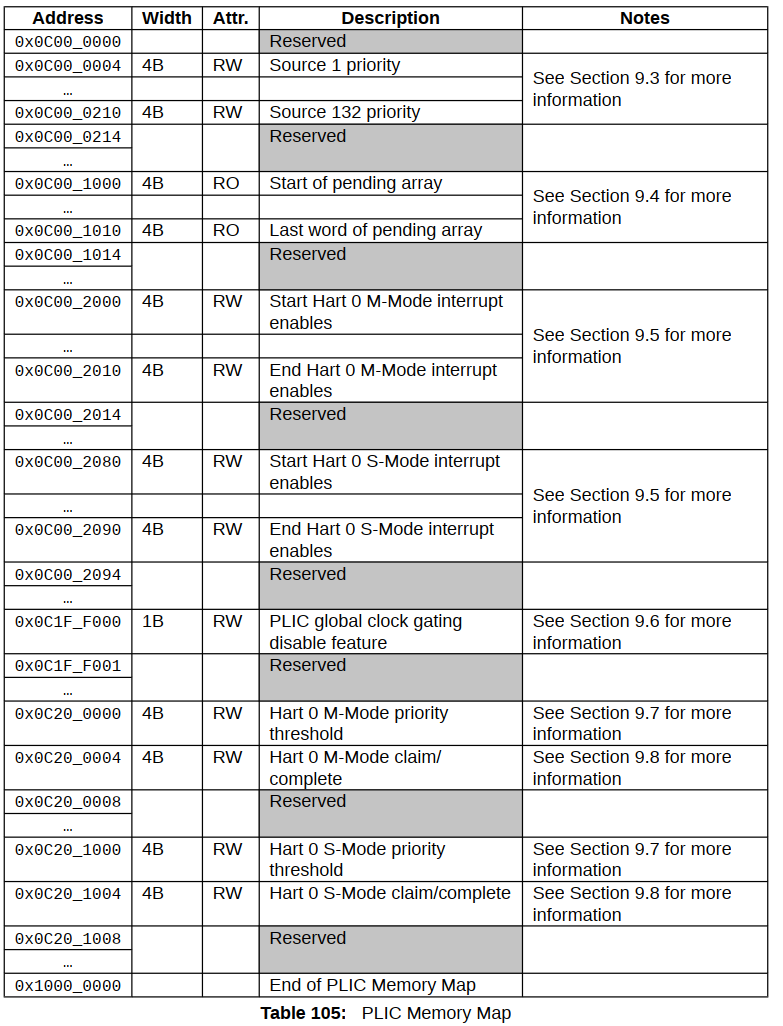

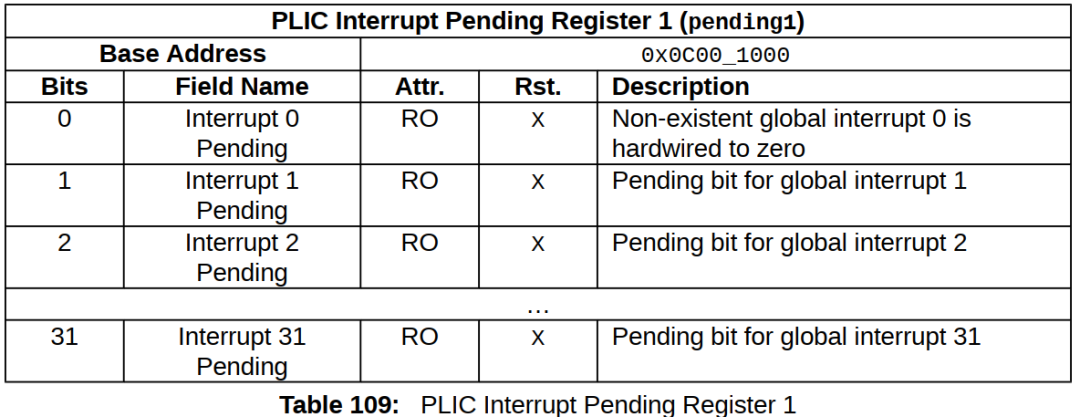

全局中断通常首先路由到 PLIC,然后使用外部中断进入 hart(中断 ID #11)

中断操作

在特权模式 m 内,如果相关的全局中断使能 {ie} 清零,则在该特权模式下不会产生任何中断,但更高特权模式下的待决启用中断将抢占当前执行。如果设置了{ie},则在相同特权模式下处于更高中断级别的挂起启用中断将抢占当前执行并运行更高中断级别的中断处理程序。

当发生中断或同步异常时,会修改特权模式以反映新的特权模式。处理程序特权模式的全局中断使能位被清除

中断进入和退出

当中断发生时:

• mstatus.MIE 的值被复制到mcause.MPIE 中,然后mstatus.MIE 被清除,有效地禁用了中断。

• 中断前的特权模式在mstatus.MPP 中编码。

• 当前 pc 被复制到 mepc 寄存器中,然后将 pc 设置为 mtvec 指定的值

此时,控制权移交给中断处理程序中的软件,并禁用中断。执行 mret 指令时,会发生以下情况:

• 特权模式设置为在 mstatus.MPP 中编码的值。

• 全局中断使能 mstatus.MIE 设置为 mcause.MPIE 的值。

• pc 设置为mepc 的值。

此时,控制权交给软件。

-

寄存器

+关注

关注

31文章

5363浏览量

121035 -

内核

+关注

关注

3文章

1382浏览量

40393 -

控制

+关注

关注

4文章

1014浏览量

122739 -

RISC

+关注

关注

6文章

465浏览量

83835 -

sifive

+关注

关注

0文章

36浏览量

9469

发布评论请先 登录

相关推荐

Linux内核中断设计与实现

STM32U5退出stop2模式后进入HardFault_Hand的原因?

串口中断程序里发送数据如何进入中断?

TMS320C54x系列DSP的中断机制

STM32进入和退出睡眠模式

U54内核PLIC中断处理例子

U54内核上CLINT的内存映射

U54内核中断控制和状态寄存器

U54内核中断进入和退出

U54内核中断进入和退出

评论