中断控制和状态寄存器

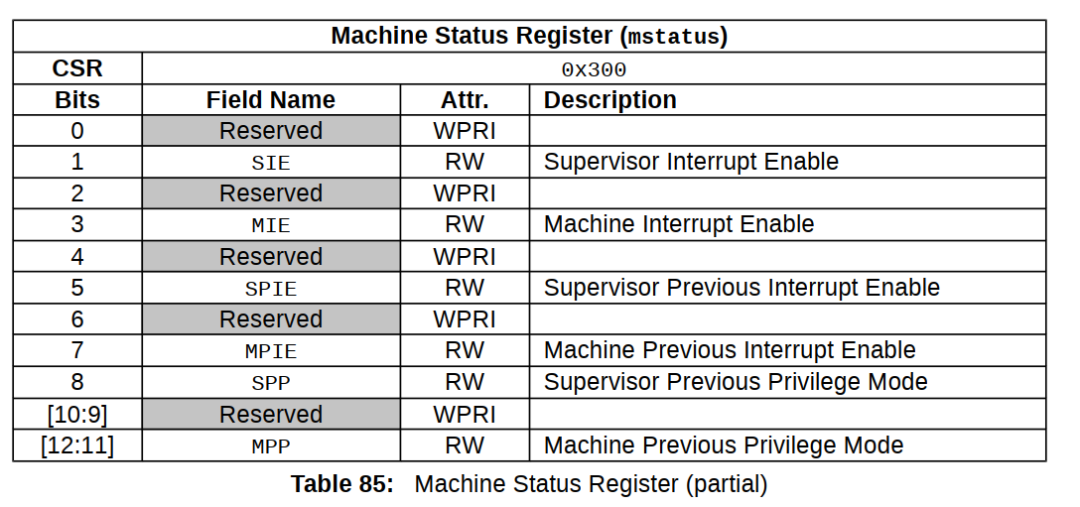

Machine Status Register (mstatus)

mstatus 寄存器跟踪并控制 hart 的当前操作状态,包括是否启用中断。

通过设置 mstatus 中的 MIE 位来启用中断。在写入 mstatus.MIE=1 之前,建议先在 mie 中开启中断。

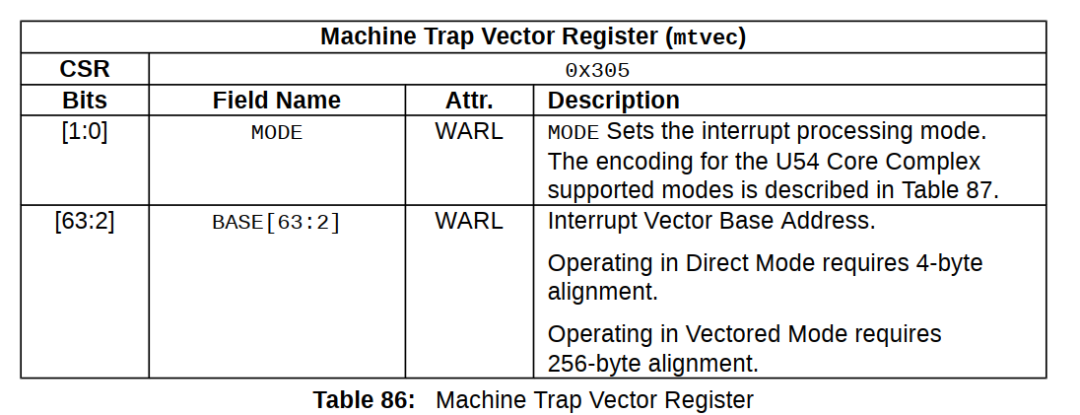

Machine Trap Vector (mtvec)

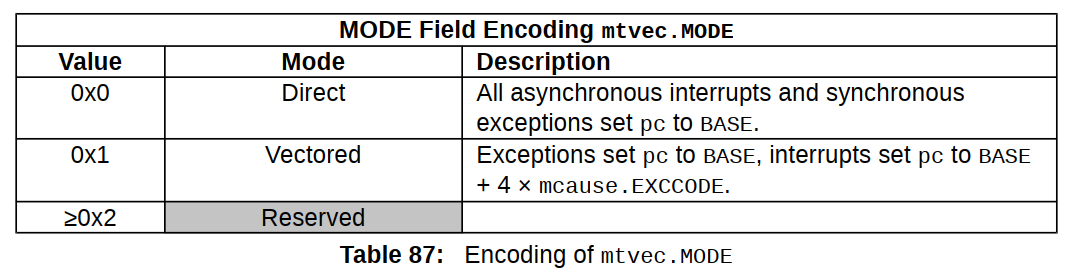

mtvec 寄存器有两个主要功能:定义陷阱向量的基地址,以及设置 U54内核处理中断的模式。对于 Direct 和 Vectored模式,中断处理模式在 mtvec 寄存器的 MODE 字段中定义。mtvec 寄存器在表 86 中描述,mtvec.MODE 字段在表 87 中描述。

Mode Direct

在直接模式下操作时,所有中断和异常都会捕获到 mtvec.BASE 地址。在陷阱处理程序内部,软件必须读取 mcause寄存器以确定触发陷阱的原因。

在直接模式下操作时,BASE 必须是 4 字节对齐的。

Mode Vectored

在向量模式下运行时,中断将 pc 设置为 mtvec.BASE + 4 ×异常代码(mcause.EXCCODE)。例如,如果发生机器定时器中断,则将 pc 设置为 mtvec.BASE +0x1C。通常,陷阱向量表填充有跳转指令,以将控制转移到特定于中断的陷阱处理程序。

在向量中断模式下,BASE 必须是 256 字节对齐的。

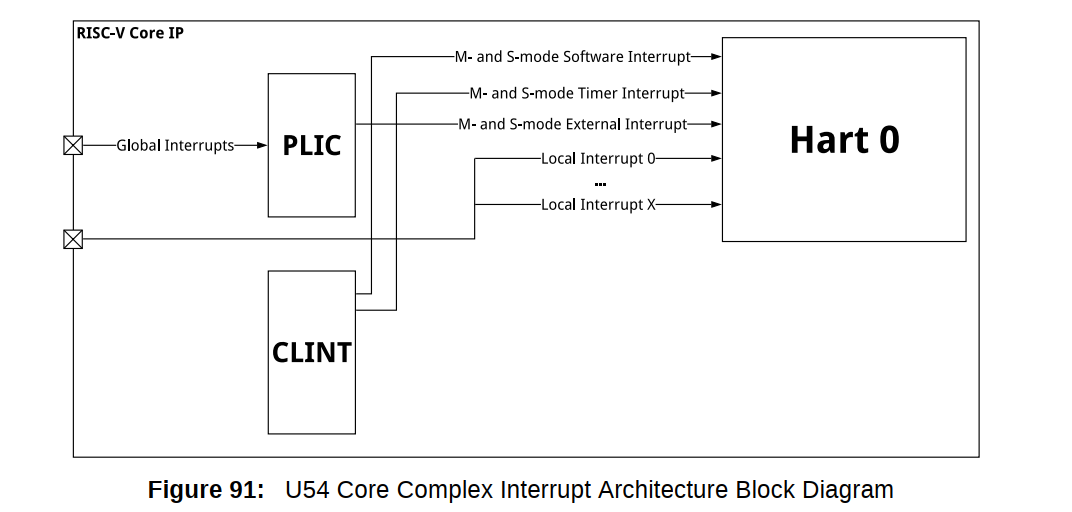

所有机器外部中断(全局中断)都映射到异常代码 11。因此,当启用中断向量时,pc 设置为任何全局中断的地址 mtvec.BASE +0x2C。

Machine Interrupt Enable (mie)

通过设置 mie 寄存器中的相应位来启用各个中断。

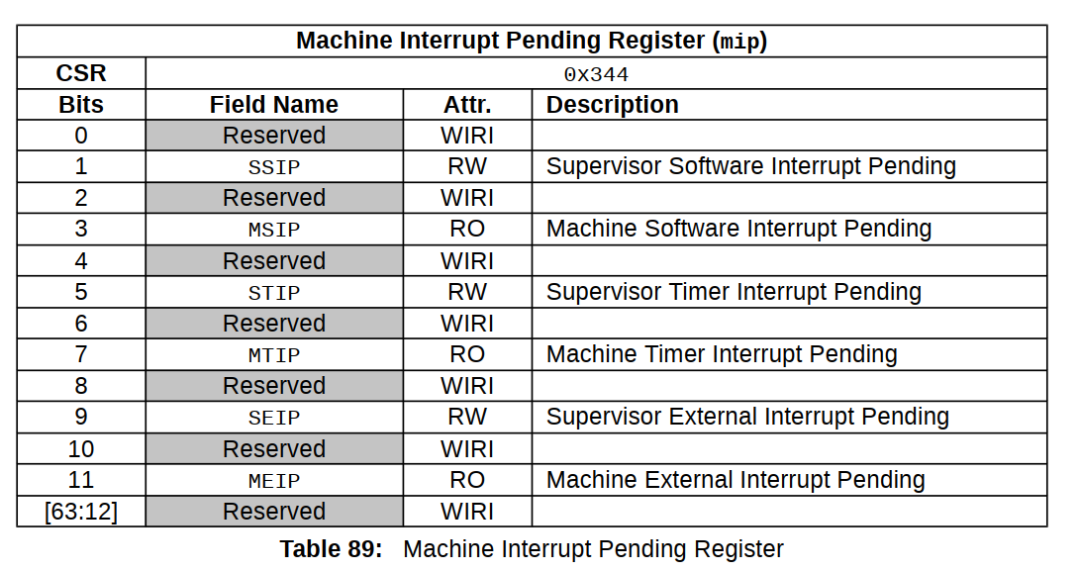

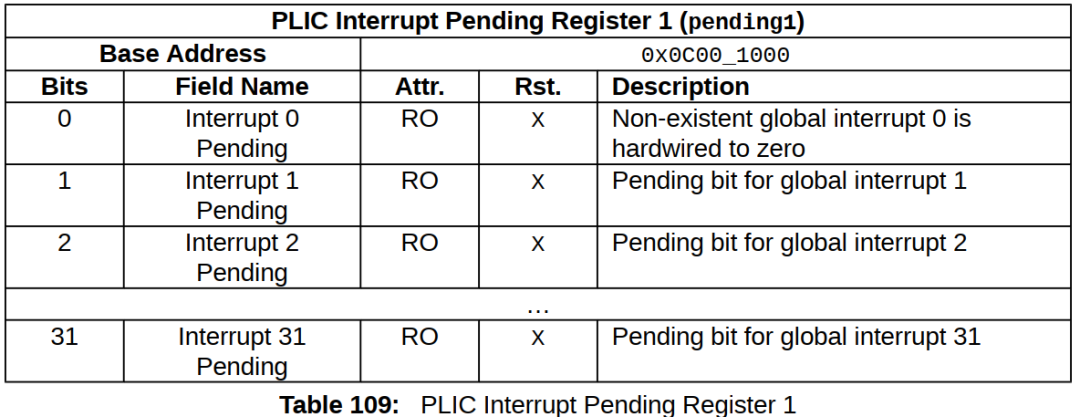

Machine Interrupt Pending (mip)

机器中断挂起 (mip) 寄存器指示当前哪些中断处于挂起状态。

-

寄存器

+关注

关注

31文章

5377浏览量

121396 -

内核

+关注

关注

3文章

1384浏览量

40458 -

中断

+关注

关注

5文章

900浏览量

41838 -

RISC

+关注

关注

6文章

468浏览量

83944 -

sifive

+关注

关注

0文章

36浏览量

9480

发布评论请先 登录

相关推荐

STM32串口通信相关寄存器和中断回调函数

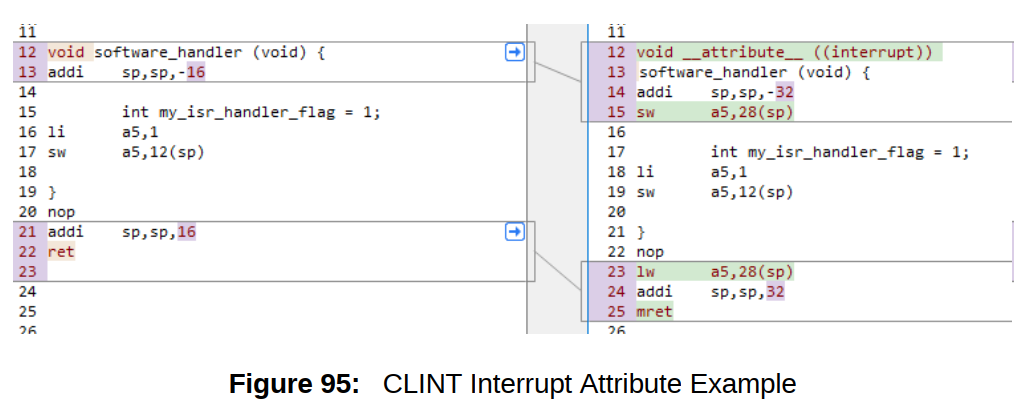

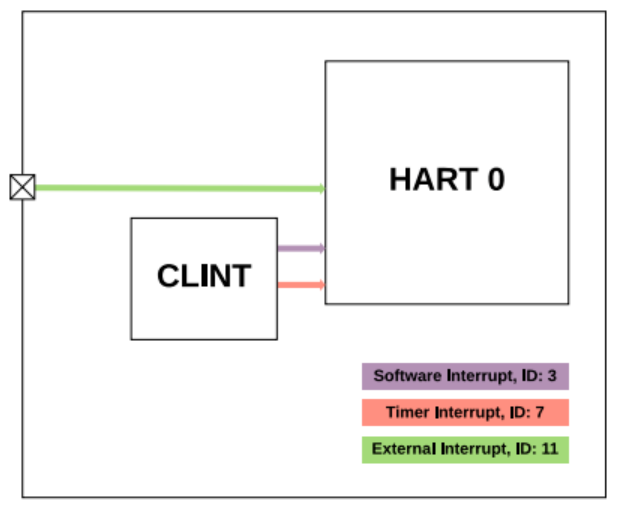

U54内核上CLINT的内存映射

U54内核中断进入和退出

U54内核中断控制和状态寄存器

U54内核中断控制和状态寄存器

评论