不可屏蔽中断

rnmi(可恢复不可屏蔽中断)中断信号是 hart 的电平敏感输入。不可屏蔽中断比 hart上的任何其他中断或异常具有更高的优先级,并且不能被软件禁用。具体来说,它们不会通过清除mstatus.mie 寄存器来禁用。

Handler Addresses

NMI 有一个关联的异常陷阱处理程序地址。该地址由外部输入信号设置。

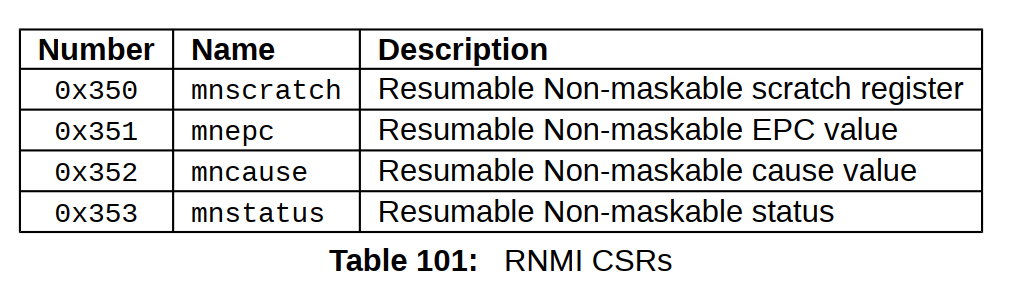

RNMI CSRs

这些 M 模式 CSR 启用可恢复非屏蔽中断 (RNMI)。

mnscratch CSR 拥有一个 64 位读写寄存器,它使 NMI 陷阱处理程序能够保存和恢复被中断的上下文。

mnepc CSR 是一个 64 位读写寄存器,在进入 NMI 陷阱处理程序时,它保存接受中断的指令的 PC。mnepc 的最低位硬连线为零。

mncause CSR 包含 NMI 的原因,第 63 位设置为 1,并且 NMI 原因编码在最低有效位中,如果不支持 NMI原因,则为零。mncause 的低位,定义为 exception_code,如下:

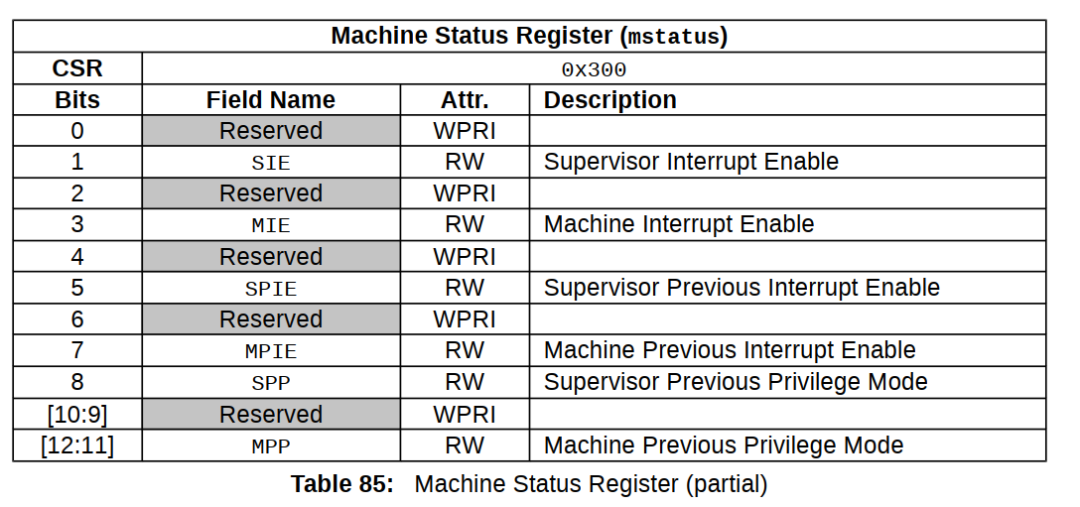

mnstatus CSR 包含一个两位字段,在进入陷阱处理程序时,它包含以与 mstatus.mpp 相同的方式编码的中断上下文的特权模式

MNRET Instruction

此仅 M 模式指令使用 mnepc 和 mnstatus 中的值分别返回中断上下文的程序计数器和特权模式。该指令还设置内部 rnmie状态位。

编码与 MRET 相同,除了第 30 位设置(即 funct7=0111000)。例如:

.word 0x70200073 // opcode for MNRET (return from RNMI)

RNMI Operation

当检测到RNMI中断时,将中断的PC写入mnepc CSR,RNMI的类型写入mncause CSR,中断上下文的特权模式写入mnstatusCSR。内部微体系结构状态位 rnmie 被清除以指示处理器处于 RNMI 处理程序中并且不能接受新的 RNMI 中断。清除时,内部 rnmie位还会禁用所有其他中断。

这些中断被称为不可屏蔽的,因为软件无法屏蔽中断。但是,为了正确操作,必须推迟同一中断的其他实例,直到处理程序完成,因此内部状态位

RNMI 处理程序可以使用 MNRET 指令(在第 7.11.3 节中描述)恢复原始执行,该指令从 mnepc 恢复 PC,从 mnstatus恢复特权模式,并设置内部 rnmie 状态位,重新启用其他中断。

如果hart在rnmie位清零时遇到异常,则将异常状态写入mepc和mcause,mstatus.mpp设置为M-mode,hart跳转到RNMI异常处理程序地址。

RNMI 处理程序中的陷阱只有在处理程序正在服务发生在机器模式之外的中断时发生时才能恢复。

-

内核

+关注

关注

3文章

1372浏览量

40287 -

RISC

+关注

关注

6文章

462浏览量

83723 -

sifive

+关注

关注

0文章

36浏览量

9459

发布评论请先 登录

相关推荐

stm32上的中断挂起和屏蔽与ARM内核中的挂起屏蔽是相同的吗?

转:IAR编译环境禁用NMI(不可屏蔽中断)

ARM7内核的中断屏蔽方法

U54内核PLIC中断处理例子

U54内核上CLINT的内存映射

U54内核中断进入和退出

U54内核中断控制和状态寄存器

U54内核不可屏蔽中断信号

U54内核不可屏蔽中断信号

评论