1. 在组相联cache中,用于替换cache line的算法有哪些?

- LRU(Least Recently Used)算法:该算法会跟踪每个cache line的age(年龄)情况,并在需要时替换掉近期最少使用的cache line。

- MRU(Most Recently Used)算法:这与LRU相反,最年轻的cache line会优先被替换掉。

- PLRU(Pseudo LRU)算法:这与LRU相似,它没有age跟踪cache line(这样开销较大),只有1个或2个bit来跟踪cache line使用情况。

- LFU(Least Frequently Used)算法:该算法会跟踪一个cache line访问的频率,并决定替换使用次数最少的cache line。

- Random replacement算法:该算法不存储任何信息,当需要替换时随机选择一个cache line。

2. Cache coherency的问题是什么?

在SMP(Shared Multiprocessor systems)中,多个处理器都有自己的cache,同一数据(同一地址)的多个副本可能同时存在于不同的cache中。如果允许每个处理器自由更新cache,则可能导致数据一致性被破坏了。例如:如果允许两个处理器向相同的地址写入值,那么在不同的处理器上读取相同的地址可能会看到不同的值。

3. 基于snoop的缓存一致性协议和基于directory的缓存一致性协议有什么区别?

在基于Snoop的一致性协议中,来自处理器的数据请求被发送到共享系统里的所有其它处理器。其它处理器根据这个请求查看自己是否有数据的副本,并做出相应的响应。因此,每个处理器都试图保持内存的一致性视图。

在基于directory的一致性协议中,directory用于跟踪哪些处理器正在访问和缓存哪些地址。任何发出新请求的处理器都将检查该directory,以了解是否有任何其它处理器用于数据副本,然后可以向该处理器发送点到点请求,以获取最新的数据副本。

两者的优缺点为:基于snoop的一致性协议用于较小的系统的话,如果有足够的带宽用于传递请求,它会更快。但对于较大的SMP系统不具有可伸缩性,因此需要为每个请求广播消息,可能会使系统过载阻塞。基于directory的一致性协议由于在发送消息之前需要查找记录的表,可能会有较长的延迟。但它没有广播消息,可伸缩性更好,通常用于较大的SMP系统中。

4. 什么是MESI协议?

MESI协议是具有多个write-back 类型cache的设计中最常用的cache一致性协议。MESI表示在所有cache中跟踪每个cache line并用于响应snoop请求的状态。这些不同的状态可以解释如下:

- M(Modified):表示cache line数据相对于memory数据被修改过了,为dirty的。

- E(Exclusive):此状态表示cache line数据相对于内存是clean的,且只在该cache中存在。Exclusive属性允许该cache所在的处理器对该cache line进行写操作。

- S(Shared):该状态表示cache line被多个cache共享,并且相对memory也是clean的。由于这是在所有cache共享的,因此协议不允许直接对该cache line进行写操作。

- I(Invalid):该状态表示cache line无效,没有任何有效数据。

- 当cache line处于除Invalid之外的任何状态时,cache都可以处理读请求。当cache line处于Modified或Exclusive状态时,才可以处理写请求。

5. 什么是MESIF和MOESIF协议?

这两个协议都是MESI协议的扩展,引入了两个新的状态”F”和”O”,解释如下:

- F(Forward):F状态时S状态的一种特殊形式,表明cache应该通过转发数据来充当给定cache line的任何请求的指定反馈者。如果系统中有多个cache具有处于S状态的同一cache line,则将其中一个指定为F状态,以便为来自不同处理器的新请求转发数据。该协议确保,如果任何cache保存的cache line为S状态,那么最多只有一个(其他)cache保存的cache line为F状态。这种状态有助于减少对memory带宽的占用,因为没有F状态,即使一条cache line在多个cache中处于S状态,它们都不能将数据转发给请求读或写的不同处理器。(请注意,cache中的S状态cache line只能服务于相同的处理器读取)

- O(Owned):O状态时一种特殊的状态,它是为了在不需要写回memory的情况下在系统的不同cache中移动修改过的或dirty的数据而引入的。如果cache line还与其它可以使cache line保持S状态的cache共享,则cache line需要从M状态转换到O状态。O状态有助于将修改后的数据推迟写回memory,直到真正需要时再写。

6. 什么是RFO?

RFO代表Read for Ownership。这是cache一致性协议中的一种操作。它是由处理器试图写入共享或无效状态的cache line时发出的,这将导致所有其它处理器将该cache line的状态设置为Invalid。RFO是意图写入该memory地址的读操作。因此,该操作是排他的,它将数据读到cache中,并使持有该memory地址的所有其它处理器的cache无效掉这个cache line。

-

处理器

+关注

关注

68文章

19274浏览量

229735 -

存储器

+关注

关注

38文章

7487浏览量

163801 -

SMP

+关注

关注

0文章

74浏览量

19657 -

状态机

+关注

关注

2文章

492浏览量

27536 -

cache技术

+关注

关注

0文章

41浏览量

1064

发布评论请先 登录

相关推荐

什么是缓存(Cache)及其作用

Cache和内存有什么区别

解析Arm Neoverse N2 PMU事件L2D_CACHE_WR

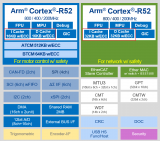

Cortex R52内核Cache的相关概念(1)

为什么HAL库在操作Flash erase的时候,需要把I-Cache和D-Cache关闭呢?

STM32F429使用外部SPI flash,只要执行Bitmap::cache(id)就进入硬件错误怎么解决?

STM32H7配置FileX时,开关“Enable data cache maintenance”的作用是什么?发生HardFault_Handler的原因?

STM32h7开启Cache后,串口发送DMA会导致中断触发如何解决?

请问STM32MP13X的MMU和Cache如何使能?

STM32H750在使能内存保护后启用cache导致SPI+DMA传输不准确怎么解决?

Cache中的data在不同核间获取数据的时候如何保证拿到的数据是最新的?

先楫HPM片上Cache使用指南经验分享

在组相联cache中,用于替换cache line的算法有哪些?

在组相联cache中,用于替换cache line的算法有哪些?

评论