ESD静电放电在芯片实际使用过程中越来越影响到芯片的可靠性,是影响芯片质量和性能的重要因素之一。因此,ESD抗干扰测试是非常重要的,防止ESD对芯片造成损坏。

什么是ESD抗干扰测试?

ESD即Electro-Static discharge,意思是静电放电测试。原理是模拟人或物体接触设备时产生的放电,以及人或物体对邻近物体的放电,来检测设备对静电放电抗干扰的能力。

ESD分为直接放电和间接放电。直接放电是指利用放电点击直接对设备进行放电;间接放电是指对设备附近的耦合版实施放电,以模拟人对被测设备附近物体的放电。

ESD抗干扰测试可以检测芯片的抗干扰能力,从而为采取ESD防护、ESD防护材料的选择、产品抗静电性能提升等提供依据,提升芯片质量和可靠性。

影响ESD抗干扰测试的因素

1. 产品本身的材质

不同外壳材质的产品有不一样的放电路径,对静电放电抗干扰测试也会有不一样的影响。如导体、绝缘体、喷有导电漆的绝缘体等。

2. 测试时的放置方式

不同的放置方式有不同的放电路径,影响也是不一样的。

3.放电点与敏感线路的距离

静电是一种高频干扰,放电时会产生电磁场,距离近会有较大的寄生电容和较小的耦合阻抗,更容易被干扰。

4.芯片本身的抗干扰能力

这个涉及多个方面,比如芯片本身承受脉冲干扰而不发生逻辑错误的能力、外围电路的处理、外部连接的布线等。

5.放电点的静电流放电路径和阻抗

不同路径会造成不同的阻抗,不同的阻抗会产生不同的干扰。

6.直接注入情况下的防护措施

如MIC、喇叭等在进行空气放电时会直接冲击信号线,如果此线路没有做防护,大多情况下会直接击穿毁坏芯片。

常见芯片抗ESD的方法

1. 设计ESD保护电路

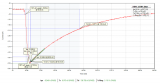

ESD保护电路如二极管、MOSFET、静电放电器等。将ESD保护电路集成到芯片设计中,可以防止ESD损坏芯片。

2. 增加芯片的接地和电源引脚数量

增加芯片的接地和电源引脚数量来降低ESD放电时的电阻,帮助更好地分散ESD能量。

3. 减小芯片尺寸

芯片尺寸减小可以帮助减小芯片内部的电容以及静电放电时芯片受到的电压峰值,从而降低ESD对芯片的损害。

4. 选择合适的材料

合适的材料可以降低ESD放电时产生的热能,降低芯片损坏的风险。

5. 在芯片外部添加防护措施

比如添加ESD保护器件和EMI滤波器等,可以保护芯片不受外部环境ESD和EMI干扰。

6. 严格的测试和验证

在芯片设计和制造的过程中,进行严格的ESD测试和验证,以确保芯片符合相关标准,并能够在ESD环境下正常工作。

纳米软件专注于各类仪器测试软件开发,其芯片测试系统与传统手动测试相比极大提高了测试效率和精度,支持批量测试,并且可以自动汇总管理测试数据,对数据进行智能分析,多样化数据报告模板可以一键导出生成。该系统致力于为广大用户提供测试解决方案,解决测试难点。

审核编辑 黄宇

-

ESD

+关注

关注

49文章

2112浏览量

173610 -

芯片测试

+关注

关注

6文章

135浏览量

20255

发布评论请先 登录

相关推荐

用ADS7830做一个按键检测,做3KV ESD测试时,ESD信号打到外壳的地时,ADS7830会锁死,怎么解决?

EMI电磁干扰测试方法 如何有效防止EMI电磁干扰

ESD器件的测试方法和标准

ESD测试仪器的使用方法

ESD测试是什么?CW32能扛8000V?

选择ESD有哪些建议?

CYT2B75BADQ0AZEGST ESD抗干扰能力问题求解

ESD的3种模型和RF PA ESD保护方案介绍

干货 | 电路设计中如何减少ESD?

ESD对电子元件的影响 如何选择ESD保护元件?

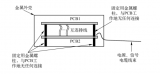

PCB工作地与金属外壳连接对ESD干扰影响的实例分析

ESD抗干扰测试是什么?防止ESD的常见方法有哪些

ESD抗干扰测试是什么?防止ESD的常见方法有哪些

评论