引言

在数字系统中,总是需要对一些数据进行比较,比较两个数值甚至多个数值的大小,然后进行排序,于是,数值比较器(Comparator)的逻辑电路便应运而生。

一、半加器的 Verilog 代码实现和 RTL 电路实现

比较器呢,比较简单,那就让我们从底层硬件代码看一看到底有多简单!!!

下面是比较器的 Verilog 代码实现:

module Comparator(

input wire [7:0] a, // 比较数

input wire [7:0] b, // 比较数

output reg result, // 比较结果

output reg equal // 比较结果

);

// 行为描述

always @(a or b) begin

if(a > b)

{equal,result} <= 2'b01; // a 比 b 大

else begin

if(a < b)

{equal,result} <= 2'b00; // a 比 b 小

else

{equal,result} <= 2'b10; // 相等

end

end

// 数据流描述

// assign equal = (a == b) ? 1 : 0;

// assign result = (a > b) ? 1 : 0;

endmodule

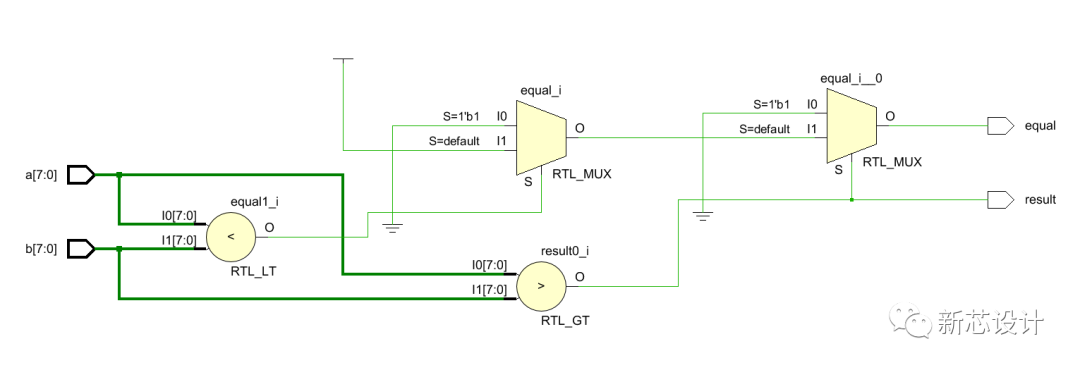

这是一个 8 位数值比较器,其 RTL 电路图如下所示:

8 位数值比较器的 RTL 电路图

对两个 8 位二进制输入信号进行大小判断:如果 a 大,则 out 为高电平;如果 b 大,则 out 为低电平;如果 a 和 b 大小相等,那么 equal 则输出高电平,否则输出低电平。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

逻辑电路

+关注

关注

13文章

494浏览量

42609 -

比较器

+关注

关注

14文章

1649浏览量

107180 -

二进制

+关注

关注

2文章

794浏览量

41637 -

RTL

+关注

关注

1文章

385浏览量

59752 -

Verilog设计

+关注

关注

0文章

20浏览量

6517

发布评论请先 登录

相关推荐

数字电路设计中的一款强大工具—Verilog编程语言介绍

Verilog是一种硬件描述语言,用于描述数字电路的结构和行为。与传统的编程语言不同,Verilog更加注重电路的行为和时序特性。

发表于 08-01 09:00

•4454次阅读

招聘:数字电路设计师

数字集成电路设计ASIC设计/验证经验;2.熟悉逻辑/时序电路的原理和设计;3.精通verilog语言;熟练使用Cadence,Modelsim,NC-

发表于 02-27 10:52

数字电路设计的基本方法有哪些

在数字电子技术基础课程中,数字电路设计的数学基础是布尔函数,并利用卡诺图进行化简。卡诺图只适用于输入比较少的逻辑函数的化简。数字电路的设计方法是:组合

发表于 02-27 11:55

基于LabVIEW的数字电路设计和仿真

基于LabVIEW的数字电路设计和仿真

数字电路设计和仿真是电子工程领域的基本技术。介绍了基于LabV IEW的数字电路设计和仿真的原理和方法,比较了其与专业EDA软

发表于 03-30 16:09

•124次下载

高速数字电路设计

高速数字电路设计

关于高速数字电路的电气特性,设计重点大略可分为三项 : Ø 正时 (Timing) :由于数字电路大多依据时脉信号来做信号间的同

发表于 10-16 17:22

•3205次阅读

Verilog数字系统设计——复杂数字电路设计2(FIFO控制器设计)

Verilog数字系统设计十二复杂数字电路设计2文章目录Verilog数字系统设计十二前言一、什

发表于 12-05 15:51

•9次下载

如何使用 Verilog 进行数字电路设计

使用Verilog进行数字电路设计是一个复杂但有序的过程,它涉及从概念设计到实现、验证和优化的多个阶段。以下是一个基本的步骤指南,帮助你理解如何使用Verilog来设计数字电路: 1.

基于Verilog的经典数字电路设计(2)比较器

基于Verilog的经典数字电路设计(2)比较器

评论