1.采用for循环来计算1的数量

采用for循环语句,逐个bit位判断是否为1,为1则累加,否则保持不变,最终输出输入信号中1的数量。

module try_top #(

parameter DATA_WIDTH = 8 , //

parameter CNT_WIDTH = ($clog2(DATA_WIDTH)+1) //

)

(

input clk , //

input rst_n , //

input [DATA_WIDTH-1:0] data_in , //

output reg [CNT_WIDTH-1:0] one_cnt //

);

always@(*) begin

one_cnt = 'b0 ;

for(int i=0; i< DATA_WIDTH;i=i+1) begin : one_cnt_gen

if(data_in[i])

one_cnt = one_cnt + 1'b1 ;

else

one_cnt = one_cnt ;

end

end

endmodule

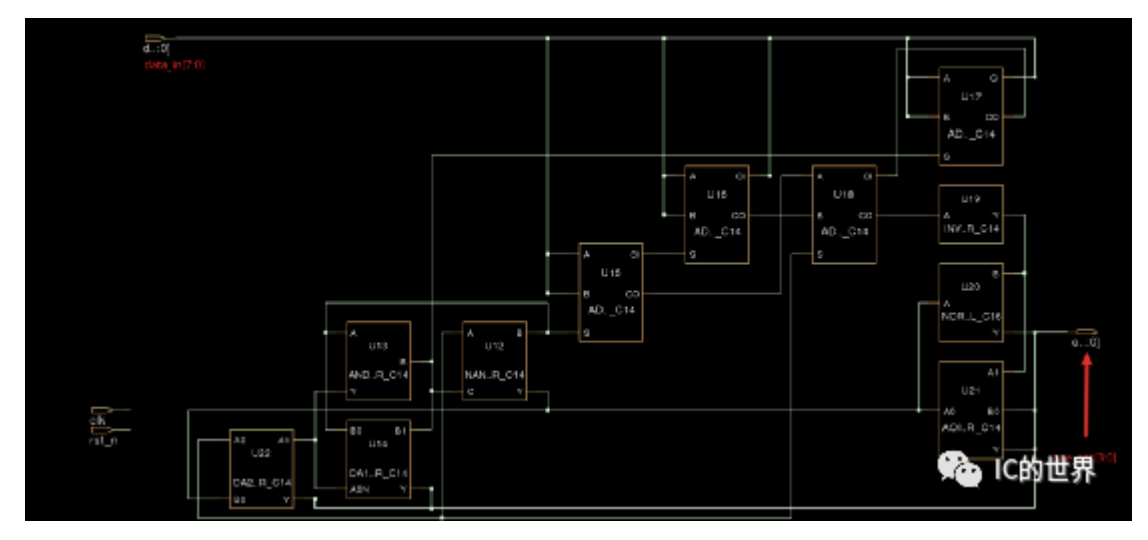

综合实现--实际就是一团组合逻辑

module try_top ( clk, rst_n, data_in, one_cnt );

input [7:0] data_in;

output [3:0] one_cnt;

input clk, rst_n;

wire n12, n13, n14, n15, n16, n17, n18, n19, n20, n21, n22;

NAND3_X1N_*Cell_TYPE* U12 ( .A(n22), .B(n14), .C(n13), .Y(n20) );

AND2_X1N_*Cell_TYPE* U13 ( .A(n14), .B(n13), .Y(n21) );

OA1B2_X1N_*Cell_TYPE* U14 ( .B0(n14), .B1(n13), .A0N(n21), .Y(one_cnt[0])

);

ADDF_X1N_*Cell_TYPE* U15 ( .A(data_in[7]), .B(data_in[6]), .CI(n12), .CO(

n17), .S(n14) );

ADDF_X1N_*Cell_TYPE* U16 ( .A(data_in[1]), .B(data_in[0]), .CI(data_in[2]),

.CO(n16), .S(n12) );

ADDF_X1N_*Cell_TYPE* U17 ( .A(data_in[3]), .B(data_in[5]), .CI(data_in[4]),

.CO(n15), .S(n13) );

ADDF_X1N_*Cell_TYPE* U18 ( .A(n17), .B(n16), .CI(n15), .CO(n18), .S(n22) );

INVP_X1R_*Cell_TYPE* U19 ( .A(n18), .Y(n19) );

NOR2_X1F_*Cell_TYPE* U20 ( .A(n20), .B(n19), .Y(one_cnt[3]) );

AOI21_X1N_*Cell_TYPE* U21 ( .A0(n20), .A1(n19), .B0(one_cnt[3]), .Y(

one_cnt[2]) );

OA21_X1N_*Cell_TYPE* U22 ( .A0(n22), .A1(n21), .B0(n20), .Y(one_cnt[1]) );

endmodule

2.综合实现解读

综合工具基本原理也是for循环不断计算,提取电路结构,只不过最后一级for循环的电路结果会覆盖之前的计算结果,for循环结束,电路结构也就确定了。

因此综合工具要求for循环的次数一定是固定值,而不能是个变量。

此处需要注意的是:除了协议中明确规定是属于测试类的语法格式,其他语法格式理论上都是可以综合的,关键在于综合工具是否支持。所以是否可综合完全取决于综合工具的版本迭代。

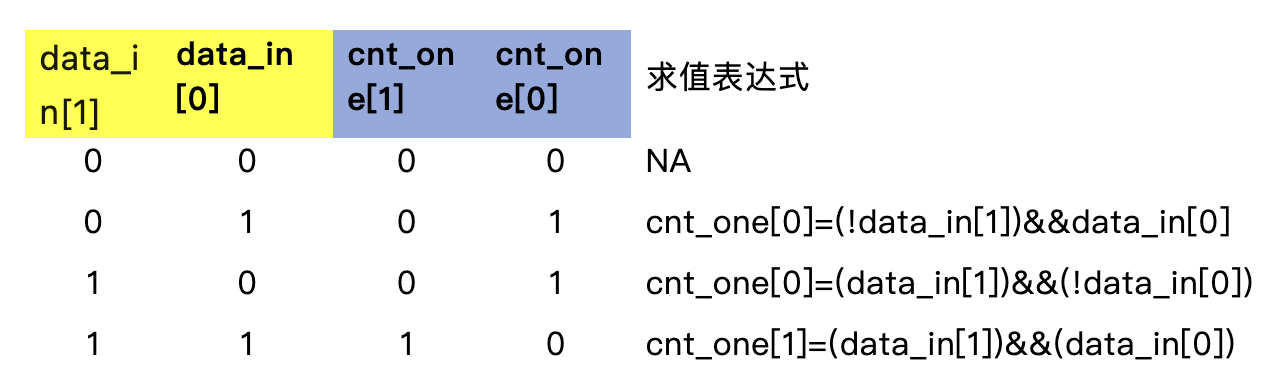

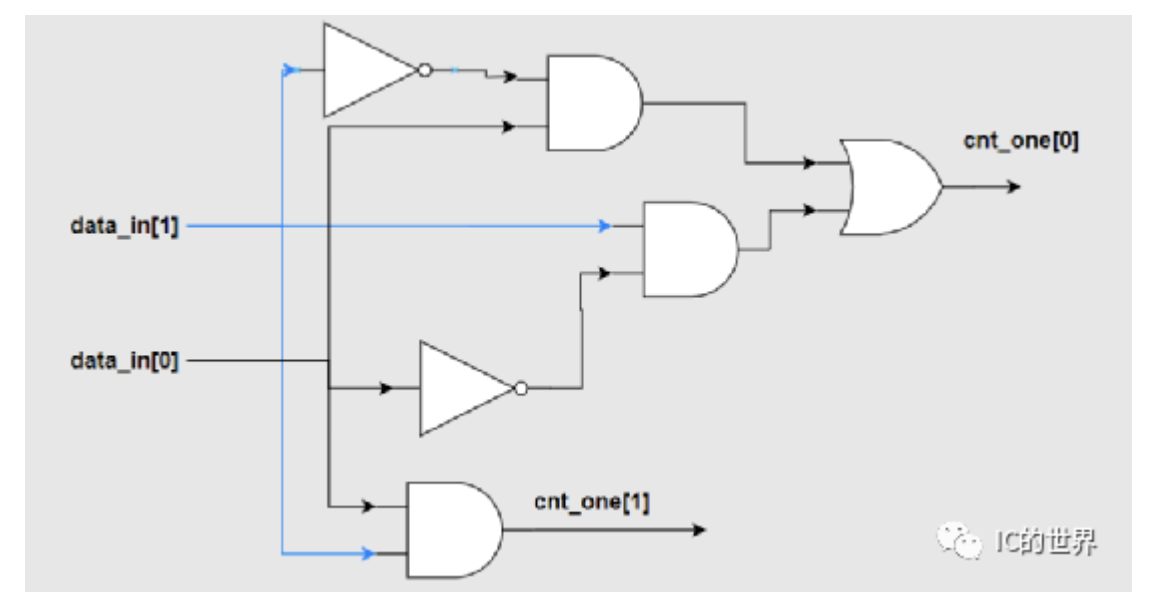

3.人工实现解读

刚才说过了综合工具的实现方式,接下来我们试试人工翻译for循环。

为了简化分析流程,以DATA_WIDTH为2为例进行讲解。首先进行穷举操作,列出所有的情况,因为dat_in只有2bit,所以本案例中只有4种情况,然后计算cnt_one的表达式,将cnt_one的表达式进行逻辑化简,最终得出电路图。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog

+关注

关注

28文章

1352浏览量

110516 -

for循环

+关注

关注

0文章

61浏览量

2554

发布评论请先 登录

相关推荐

verilog HDL 可综合模型的结构

。 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: (1)不使用初始化语句。 (2)不使用带有延时的描述。 (3)不使用循环次数不确定的

发表于 10-20 08:10

讨论Verilog语言的综合问题

在本篇里,我们讨论 Verilog 语言的综合问题,Verilog HDL (Hardware Description Language) 中文名为硬件描述语言,而不是硬件设计语言。这个名称提醒我们

发表于 07-29 07:42

Verilog HDL综合实用教程

Verilog HDL 综合实用教程第1章 基础知识第2章 从Verilog结构到逻辑门第3章 建模示例第4章 模型的优化第5章 验证附录A 可综合的语言结构附录B 通用库

发表于 07-20 11:21

•86次下载

如何设计可综合的Verilog代码和应该遵循什么原则

在接触Verilog 语法参考手册的时候,我们发现其提供了一组非常丰富的功能来描述硬件。所以大家往往会疑惑那些Verilog语句是可综合的,那些是只能用于写Testbench的,其实,参考手册中只有

发表于 04-20 10:59

•4685次阅读

Verilog可综合的循环语句

Verilog中提供了四种循环语句,可用于控制语句的执行次数,分别为:for,while,repeat,forever。其中,for,while,repeat是可综合的,但循环的次数需

发表于 10-13 12:23

•2w次阅读

如何使用Verilog HDL描述可综合电路?

1、如何使用Verilog HDL描述可综合电路 Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL语言仅是对已知硬件电路的文本描述。所以编写前: 对

Verilog逻辑设计中的循环语句和运算符

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括循环语句(forever、repeat、while和for)、运算符。”

Verilog中循环语句简介

在这篇文章中,我们讨论了可以在verilog中使用的不同类型的循环 - for循环,while循环,forever循环和repeat

verilog中for循环是串行执行还是并行执行

的for循环也是并行执行的。 Verilog中的for循环可以用来实现重复的操作,例如在一个时钟周期中对多个电路进行操作。在循环内部,多个语

Verilog:for循环的综合实现

Verilog:for循环的综合实现

评论