什么是传输时延?

首先介绍下传输时延指标。

传输时延定义:时延是指最小系统输出信号对输入信号的时间延迟。

传输时延的指标:

选频型 ≤20μs;

宽带型 ≤10μs;

每链型增加一级扩展设备,时延增加小于1.5μs;

另外还有一个相关的指标,这个指标对于两级以上的直放站系统需要关注,这个指标是时延校正范围及补偿精度。

定义:时延校正补偿精度是指系统对由于支路之间的链型级数和光纤长度不同引起的不同远端单元时延偏差的校准补偿能力。

指标:

时延补偿范围≥50μs

时延校正补偿精度±2μs

系统应具备手动和自动时延调整功能。

为什么需要传输时延指标?

信息在空间传播的速度是3×108m/s(即一公里有3.3μs时延),在光纤中的速度约为自由空间的2/3(即一公里的光纤有5μs时延)。对于时分多址系统来说,每个终端都是按顺序先后发送数据。通常是离基站近的信号就早点到达,离得远就晚点到。

问题来了,如果有一个终端用户离得基站特别远呢?基站没有识别到这个终端,这样就有可能和其他终端信号一起到达,从而形成信号重叠,而导致信号干扰。

所以直放站作为基站和用户终端之间的信号传输通道,时延不能无限制。一般系统的时延+空间传输的时延要小于各制式的保护间隔。

那么时延校准是为什么呢?

用户终端发射的信号是一个球状,如果一个用户终端刚好在两个远端的重叠覆盖区,那么用户发射的信号到达基站的时延差不一样,如果不调整,其中一个信号就成为另外一个信号的同频干扰了。所以需要把每个远端的时延调整到一个合理区间。

怎么设计才能满足传输时延?

固有传输时延设计建议:

1、数字预的滤波器:如果是模拟系统,其实整个时延就是1us内。主要是数字系统的直放站时延很大,其中很大一部分是数字预的成型滤波器。带外抑制越好成型滤波器的阶数越高,需要FPGA在做滤波器时做好兼顾。

2、光口传输速率:光口传输速率之前聊过,大家想把传输速率做低,这样可以传输更大带宽的信号,但是这样时延会增加,这个也需要同时兼顾的。

3、采样速率:采样速率越高,时延越低。但是这样会增加数字预的内插和抽取倍数,从而增加一定的时延。这个也需要同时兼顾。

4、组帧和解帧:这个是固有时延,当然如果系统时延不满足的时候,也可以优化这部分。

时延调整范围和精读设计建议:

这个比较简单,时延只可以增加,不能减少,所以FPGA在内部数字预里面做一个时延调整功能即可。但是精读尽量做细点,也就是每个sample需要足够小。

-

滤波器

+关注

关注

161文章

7919浏览量

179507 -

FPGA器件

+关注

关注

1文章

22浏览量

11670 -

传输时延

+关注

关注

0文章

5浏览量

1882

发布评论请先 登录

相关推荐

使用1.8V FPGA和DAC5662进行数据传输的问题求解

HarmonyOS应用点击完成时延问题定位流程及原理

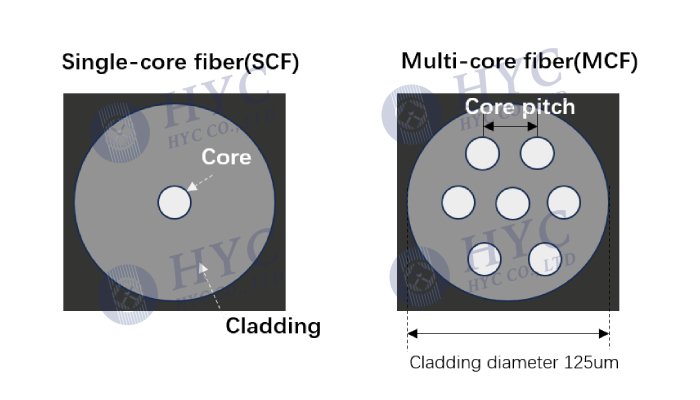

突破传输容量瓶颈:多芯光纤与空芯光纤

传输频率和传输速率怎么换算

汉得利亮相延锋国际合作伙伴技术创新大会

采用opa695用TINA-TI仿真一个时延放大电路,输出的信号有尖峰,请问是怎么回事?

TLV3201电流检测电路的时延应该怎么算?

TC367在GPT中断下驱动PWM输出会导致定时器发生时延怎么解决?

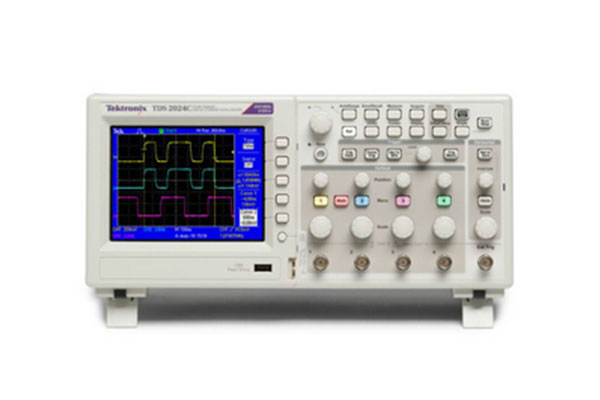

示波器如何测量时延呢?有哪几种方法?

HarmonyOS实战开发-如何实现音频低时延录制和播放,AudioVivid音乐播放的相关功能

泰克示波器如何测量时延?

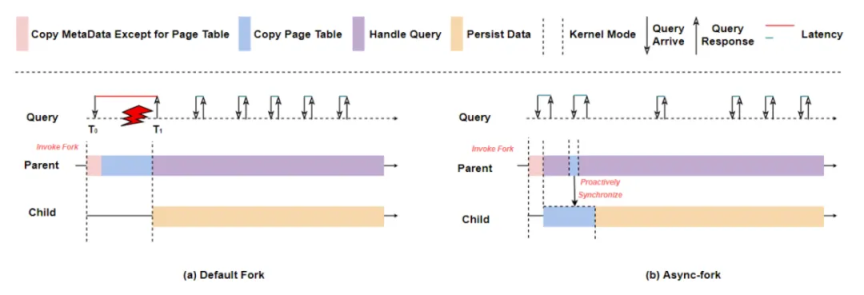

浅析 KV 存储之长尾时延问题,探寻行业更优解决方案!

什么是传输时延?为什么需要传输时延指标?

什么是传输时延?为什么需要传输时延指标?

评论