1.前言

Live-Simulation (live-sim)模式允许Visualizer调试环境与Questasim进行交互操作,此模式将Visualizer GUI与Questasim仿真相结合,因此可以在线调试当前仿真的结果和波形。

在livesim模式中,可以在Visualizer GUI中控制仿真、设置断点(Breakpoints)、单步调试、检查记录或未记录的数据值、以及跟踪类对象。因此,在调试验证环境或RTL的问题时,livesim可以更有效率地定位问题。下文介绍下live-simulation模式如何启动以常用功能。

2.启动live-sim模式

Questasim要求使用3步仿真流程(vlog, vopt, vsim)来调用livesim模式下的Visualizer,而不是2步仿真流程(vlog, vsim+vopt)。

第一步:准备TB和RTL代码

这里简单创建名为livesim_example.sv的文件,它的内容是:

module livesim_example;

int a = 600;

int b = 66;

int c;

reg clk = 1'b0;

initial begin

c = a + b;

$display("result1: The sum of a(%0d) and b(%0d) is c(%0d)", a, b, c);

# 10ns;

forever begin

# 5ns;

clk = ~clk;

c = c + 1;

$display("The current c: %0d", c);

# 5ns;

c = c + 2;

$display("The current c: %0d", c);

end

end

endmodule

第二步:vlog命令编译

需要调用Questasim的vlog命令把代码先编译过,命令如下:

vlib work

vlog livesim_example.sv

这时候会生成livesim_example的top module。(注意,如果是VHDL文件的话,要使用vcom命令,而不是vlog)

第三步:vopt命令优化

需要调用Questasim的vopt命令把design优化下,命令如下:

vopt -debug livesim_example -o live_opt -designfile design.bin

这时候会生成名为live_opt的优化design名。

在优化过程中,必须的-designfile参数的作用是创建Visualizer所需的design数据库文件名称(design.bin),如果默认用design.bin名称的话,其实-designfile design.bin可以替换为+designfile,这样Questasim默认生成的bin文件名字为design.bin。必须的-o参数为design的优化版本指定一个名称,名称可以包含小写字母、大写字母、数字字符或下划线。可选的-debug参数限制优化以保证行号的可见性,这就可以在Visualizer的livesim模式下启用行breakpoints。其它需要的vopt参数大家可以根据需要添加。

第四步:vsim命令仿真

使用vsim命令开始仿真,命令如下:

vsim -visualizer live_opt

这里live_opt的名字就是第三步vopt命令-o参数生成的名字。vsim命令将design加载到仿真器中,然后将design.bin文件和仿真控制传递给Visualizer GUI。

在design elaboration过程中,仿真elaboration消息显示在启动shell中,并且也保存在visualizer.log文件中。如果elaboration有错误,则显示消息并退出仿真。如果elaboration成功,将调用Visualizer GUI。Visualizer GUI首先读取数据并连接到仿真器,当GUI准备好接受CLI命令时,在transcript窗口会出现” Visualizer 1>”。

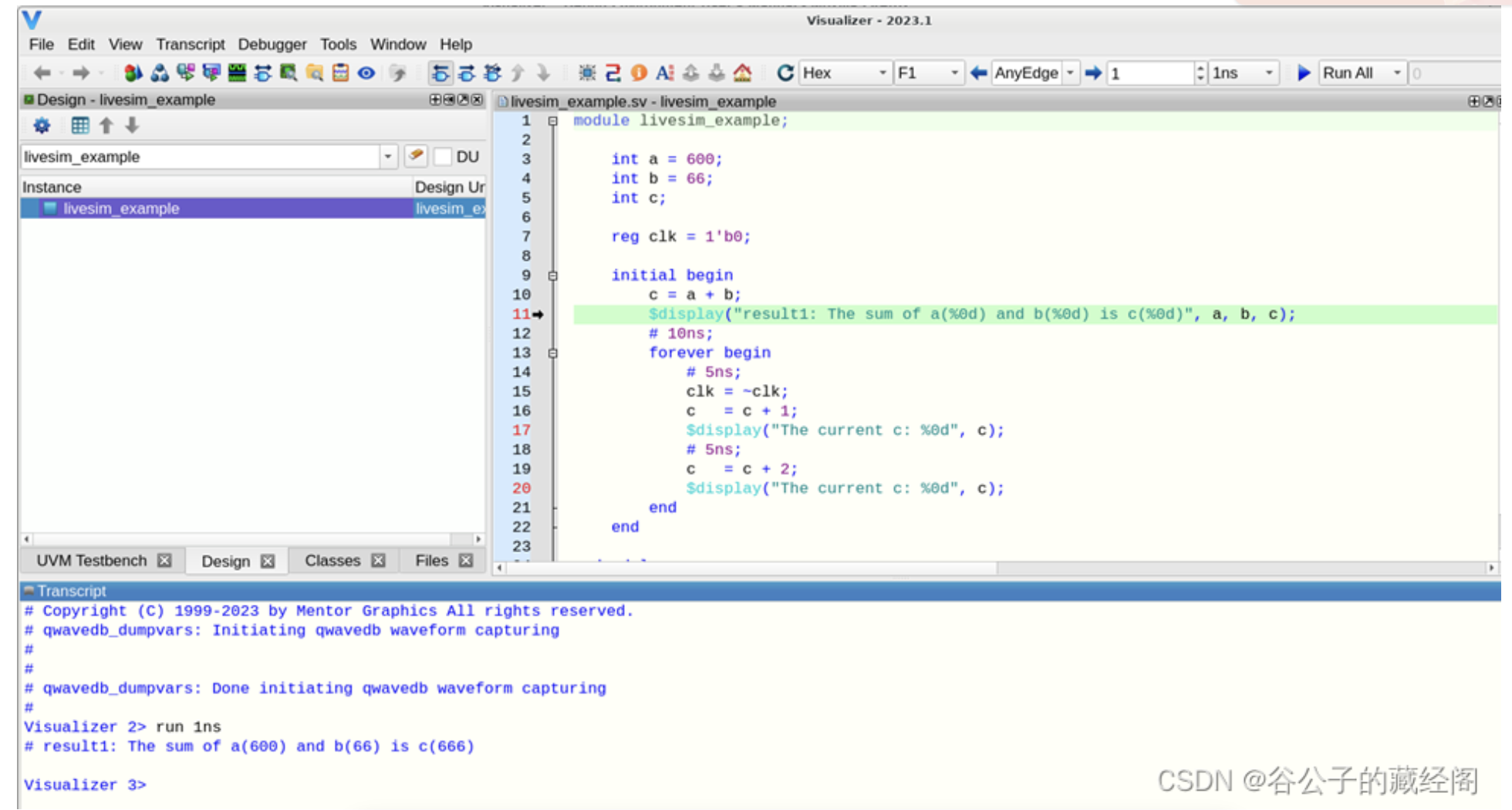

只要完成了以上的几个步骤,就会出现以下界面,表示进入livesim模式了,也就是联合Questasim和Visualizer进行实时仿真调试。

3. livesim仿真常用功能

进入livesim模式后,就是使用Visualizer GUI界面去debug代码了,这里简单介绍几个常用功能,更多的用法大家可以去探索下。

3.1 变量值提示

当启用变量值提示(Value Tool Tip)功能后,记那个鼠标悬停在源代码、原理图和许多其它窗口中的对象上时,弹出的工具提示将显示该对象的值、大小和带有下划线 (_) 的基数前缀。此默认值格式化在仿真期间被记录。

不过通过vsim命令中指定+vis_no_format_num,可以禁用值格式化,只显示对象值。变量值提示(Value Tool Tip)启动和关闭按钮在下图红色箭头指向的地方。

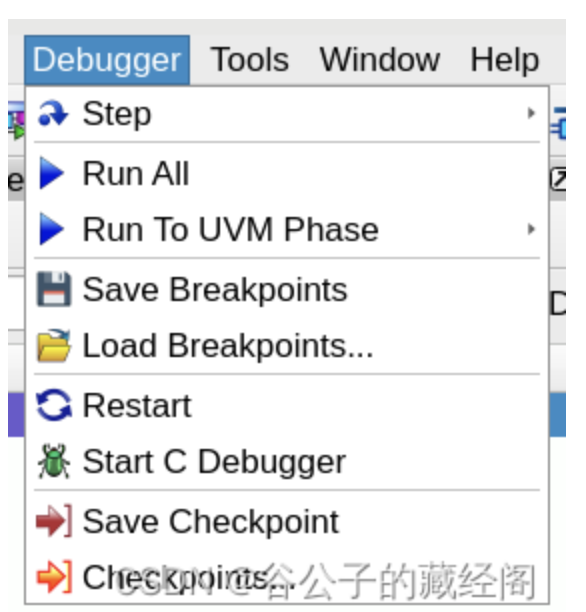

3.2 Debugger菜单

在Debugger菜单下有运行、步进、重新启动、保存或恢复checkpoints点,以及使用C调试器。

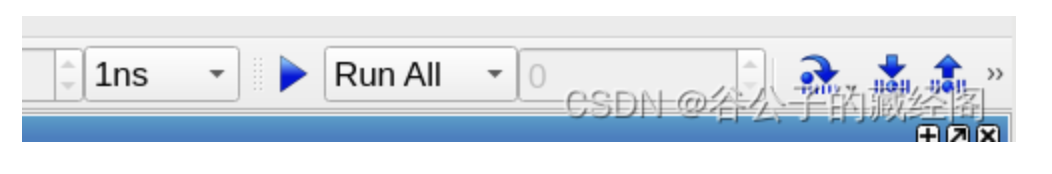

3.3 工具栏的调试

在工具栏上也可以方便的控制仿真的进行。

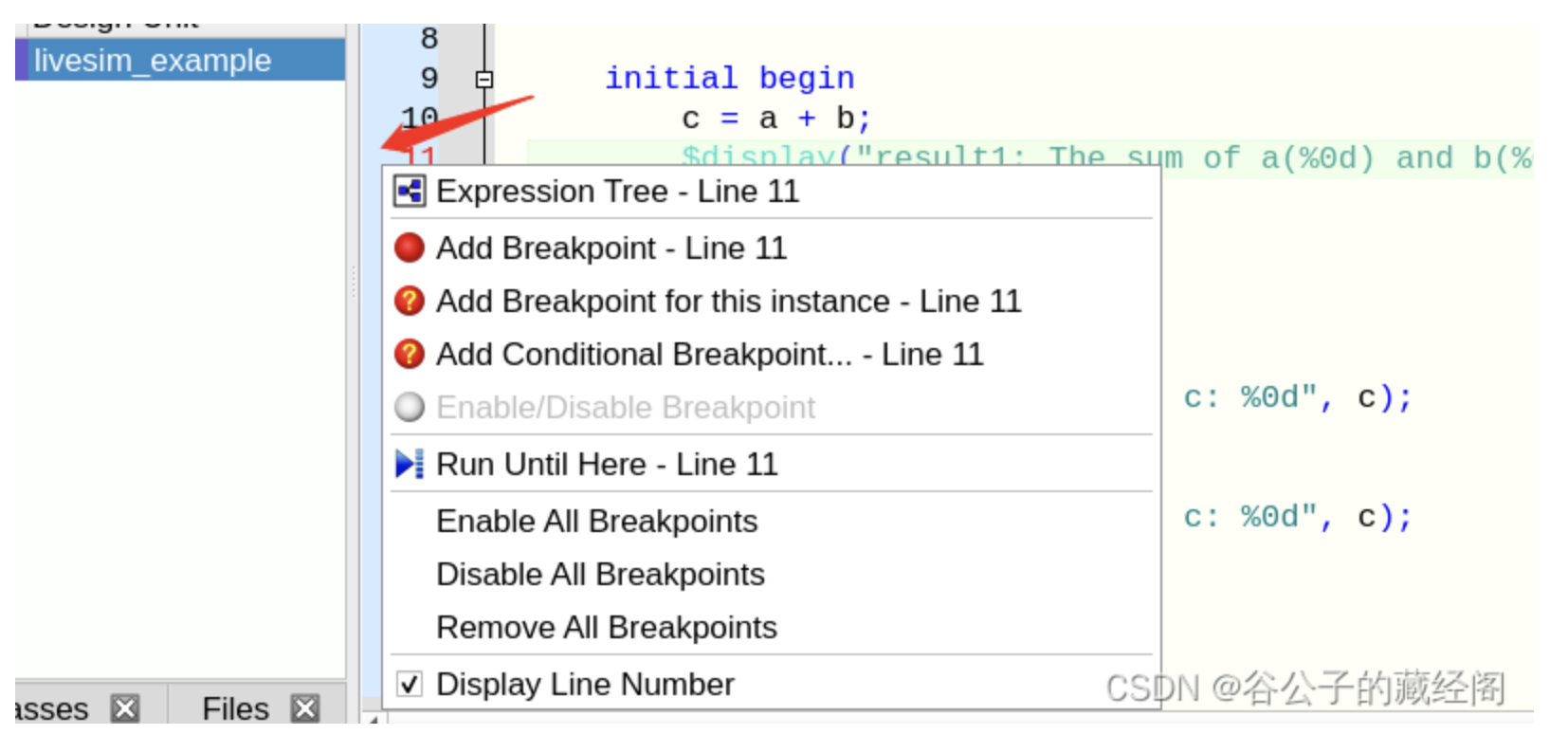

3.4 设置breakpoint

右键代码的前方,会出现以下窗口,我们就可以设置一些breakpoint来辅助debug。

-

仿真器

+关注

关注

14文章

1018浏览量

83796 -

RTL

+关注

关注

1文章

385浏览量

59841 -

GUI

+关注

关注

3文章

662浏览量

39747 -

VHDL电路

+关注

关注

0文章

4浏览量

1421

发布评论请先 登录

相关推荐

NCSIM、VCS和QuestaSim后仿真如何屏蔽冗余的违例信息呢?

如何用questasim进行systemverilog仿真

ISE设计,questasim仿真时库编译的问题

PROTOLINK PROBE VISUALIZER的优势

介绍一下波形仿真如何进行

全新WEBENCH Visualizer设计工具

ModelSim和QuestaSim功能简介及应用

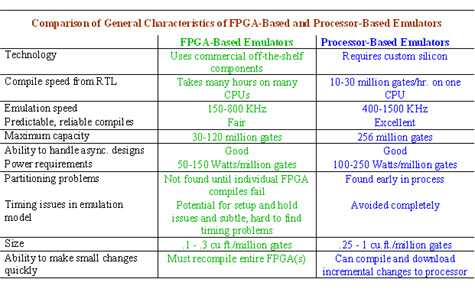

基于FPGA的仿真如何工作

如何通过自动化脚本实现Questasim和Verdi的联合仿真

Questasim与Visualizer的livesim仿真如何启动呢?

Questasim与Visualizer的livesim仿真如何启动呢?

评论