什么是ACLR?

邻道泄露抑制比是用于衡量下行的发射性能,是主信道的发射功率与测得的相邻信道的功率之比。ACLR值越低,表示相临信道的功率的干扰越小,说明系统的性能越好。一般用dBc作为单位。

现在有些厂家或运营商的招标规范喜欢用“输入互调抑制”来定义该指标,主要是目前直放站系统需要兼容多制式,通过一个指标去衡量2G、3G、4G和5G的ACLR。

另外一个原因是由于ACLR的指标太严格,如果设备是没有DPD或是纯模拟的,那么实现这个指标完全靠末级的功放了,要满足这么好的ACLR,一般得使用大功率功放,这样整机的功耗和散热又受影响了。所以提出一个新指标,就不用参考3GPP,进而降低下标准。

那我们看看什么是输入互调?

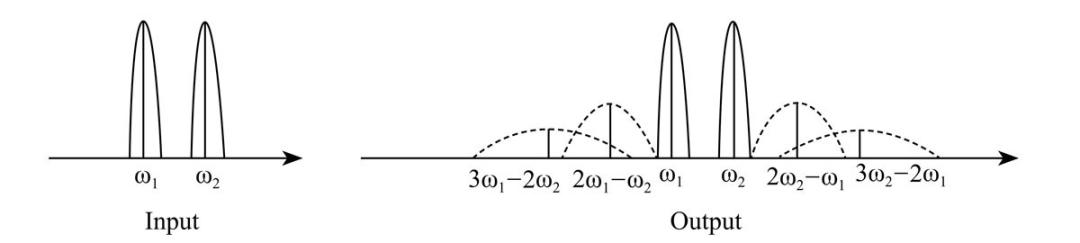

输入互调是指两个及两个以上载波所导致的带内及带外互调干扰信号和抑制能力。类似下图所述:

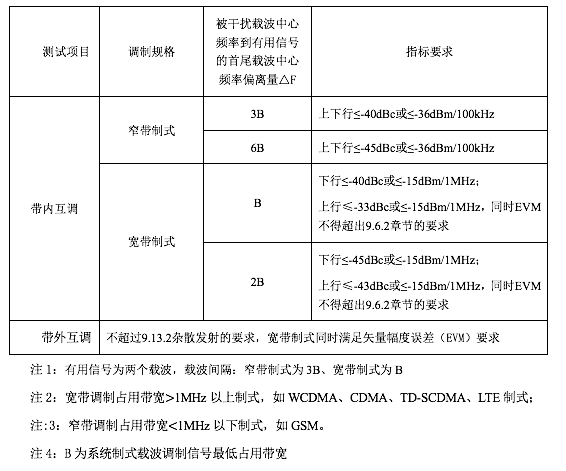

输入互调的指标如下:

为什么需要ACLR?

ACLR、输入互调和SEM都是衡量系统的工作频段内的“带外杂散”。由于调制过程中和传输过程中的非线性产生的相邻有用信道外的有害杂散。这个不包含杂散发射,杂散发射是指工作频段外的,而ACLR和SEM衡量的带外杂散都是属于工作频段内。

由以上定义可以知道,ACLR和SEM类似,衡量设备共址的情况下,别互相干扰对方。

但ACLR和SEM还是有区别的,具体区别下期可以展开聊聊。

怎么设计才能满足ACLR?

这个指标优化起来需要注意以下几个方面:

1、末级功放的线性:主要是末级和推动级的功放的性能不好,特别是级联后的线性,需要在设计前测试、仿真和计算。

2、信噪比不足:主要的输出功率过小,特别是上行。输出功率过小,底噪又很大,导致信噪比不足,这样满足不了ACLR。需要提高输出功率或者降低底噪。

3、杂散泄露:特别是DA产生的杂散,特别是零中频方案的设备,会有一个直流杂散,需要优化到底噪之下。

4、DPD性能:除了小信号时功放的性能需要保证10dB以上的预留外,DPD算法的性能也需要保证,这都需要使用不同的制式信号去调测的。

-

SEM

+关注

关注

0文章

275浏览量

15726 -

零中频

+关注

关注

0文章

64浏览量

9512 -

DPD算法

+关注

关注

0文章

4浏览量

7241 -

ACLR

+关注

关注

0文章

12浏览量

8475

发布评论请先 登录

Aigtek宽带功率放大器在电源纹波抑制比(PSRR)研究中的应用

Voohu:音频变压器的共模抑制比(CMRR)测量方法与带宽限制因素

如何通过高抑制比设计优化射频转换器性能

DC-7200MHz 8W SMA低通滤波器:7.2GHz超高频射频链路的谐波抑制学术级解决方案

罗德与施瓦茨矢量信号发生器SMW200A单次射频连接测量

从“只看中心频点”到“系统权衡”:SAW IF 滤波器的 IL、抑制、群时延怎么取舍?

技术演进与路径分化:全球民用大涵道比涡扇发动机高压压气机技术发展脉络与竞争格局深度剖析

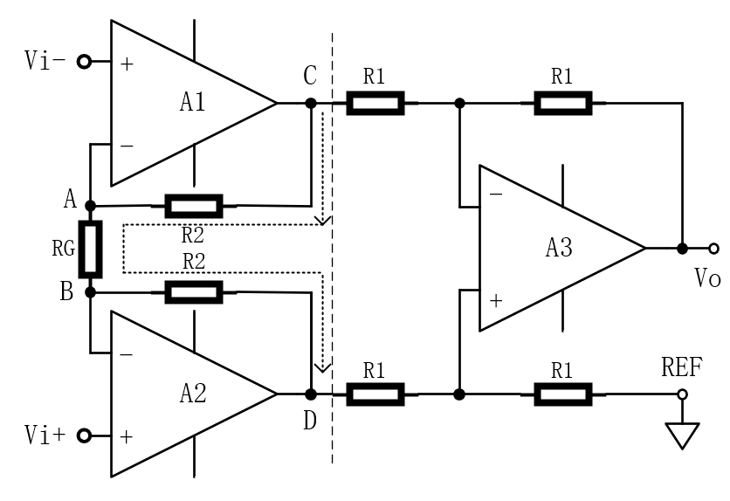

仿真分析仪表放大器共模抑制比

创邻科技出海新范式:技术破局与生态重构下的全球化突围

多通道FM广播方案求教:8 天线并行的互调/邻道干扰如何控制?

芯对话 | CBM97D79TQ:双通道16位1GSPS DAC的性能与设计实践

什么是共模抑制比?

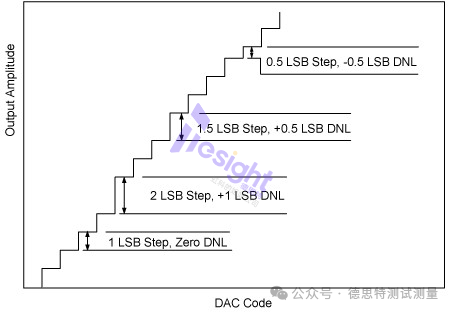

从偏移误差到电源抑制比,DAC核心术语全解析

海洋仪器电源抑制比测试方案26800元起

什么是邻道泄露抑制比(ACLR)?

什么是邻道泄露抑制比(ACLR)?

评论