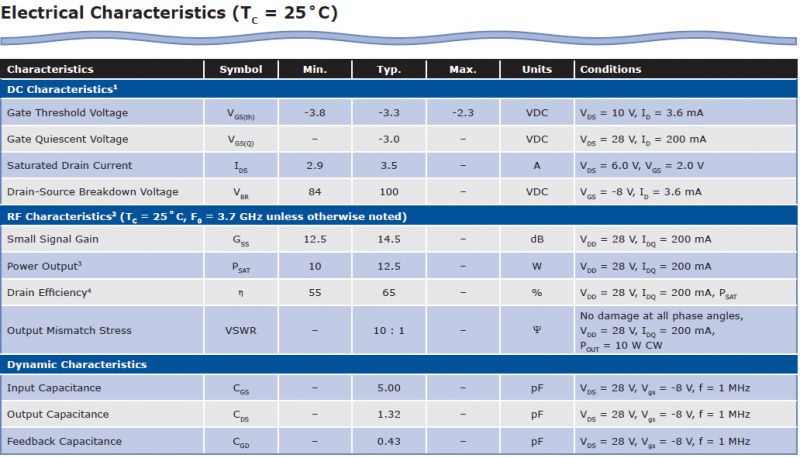

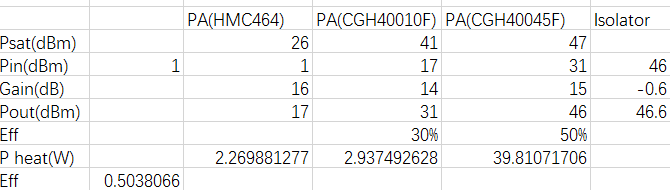

具体指标如下:

频段 2.7-3.5GHz

输入功率<1dBm

输出饱和功率>46dBm

介质板为Rogers 4003,介电常数为3.38,厚度为0.508mm

- 末级功放电路设计

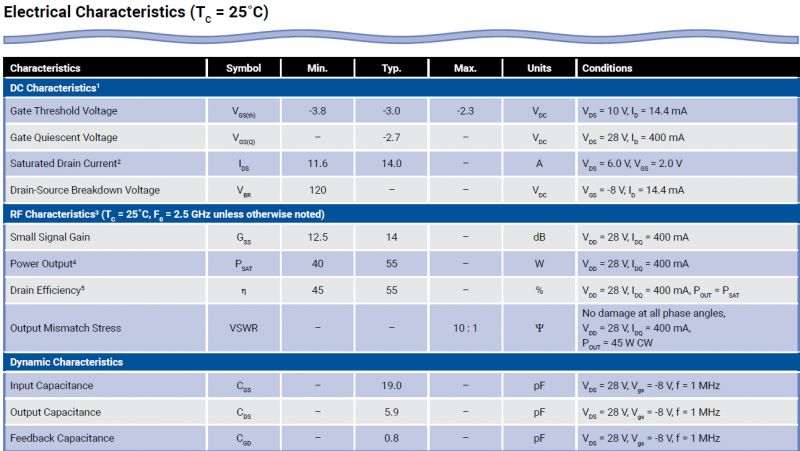

末级功率放大电路选用CREE公司的CGH40045高电子迁移速率晶体管。资料中CGH40045的饱和输出功率为55W,效率为55%

设计流程如下:

- 1 静态工作点的设置

在芯片资料中,漏源电压28V,栅源电压的工作范围为-3.0V

1.2 稳定性分析

对晶体管进行稳定性仿真可以得到稳定判断的K线图和B线图,分别如下图所示,K>1且B>0,CGH40045F在应用频段属于稳定的。

1.3晶体管输入与输出阻抗分析

利用CREE公司提供的大型号模型,结合ADS 负载牵引可以仿真得出输出与输出阻抗变化呈线性分布,因此设计电路考虑输入输出对称拓扑结构。

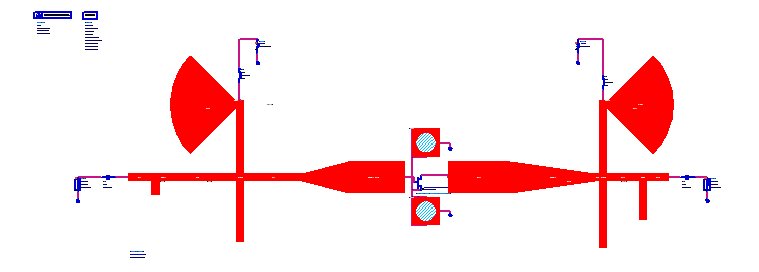

1.4 馈电端λ/4高阻线设计

偏置电源为其供电时,必须要保证电源的直流信号可以顺利向CGH40045F所在的功放电路的栅极、漏极提供偏置电压,并且还要保证功率放大器输入输出信号不会从偏置电路泄露。故需要在所要求的频段内设计一高阻线,使其对于直流表现为通路,射频信号表现为开路,即相当于扼流圈的作用。,扇形结构由于宽度是渐变的,可以很好的满足宽带性能,拓扑结构如下图所示:

经过仿真优化得到S(1,1)、S(2,2)接近0dB,在2.7-3.5GHz频段范围内全反射,满足高阻线设计要求。

1.5 功放宽带匹配电路的设计

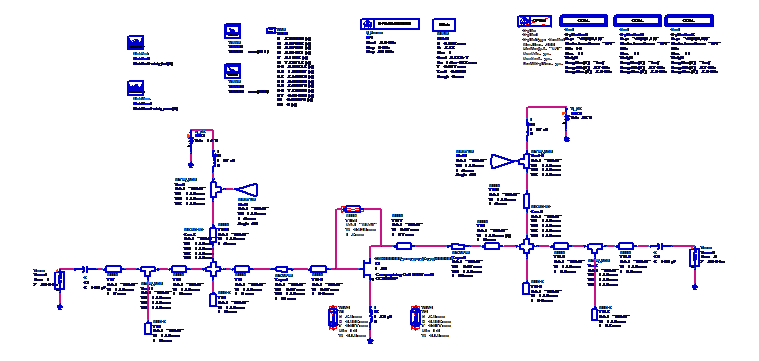

如下图所示,本文采用典型的双分支平衡匹配电路,由于其结构具有较多的可控变量,适用频段更宽,同时由于晶体管输入,输出阻抗变化较为线性,在输入端和输出端各有一段渐变线,进行阻抗平滑过渡。

根据S参数不断进行原理图优化,满足要求后进行EM版图联合仿真。

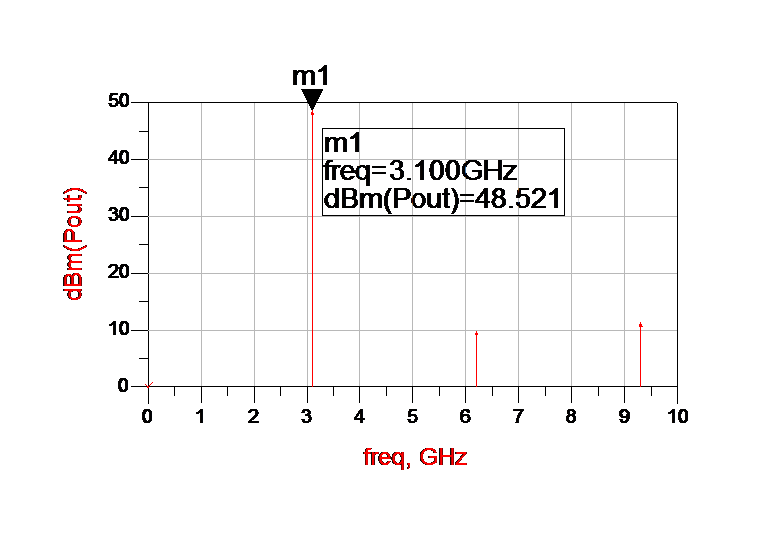

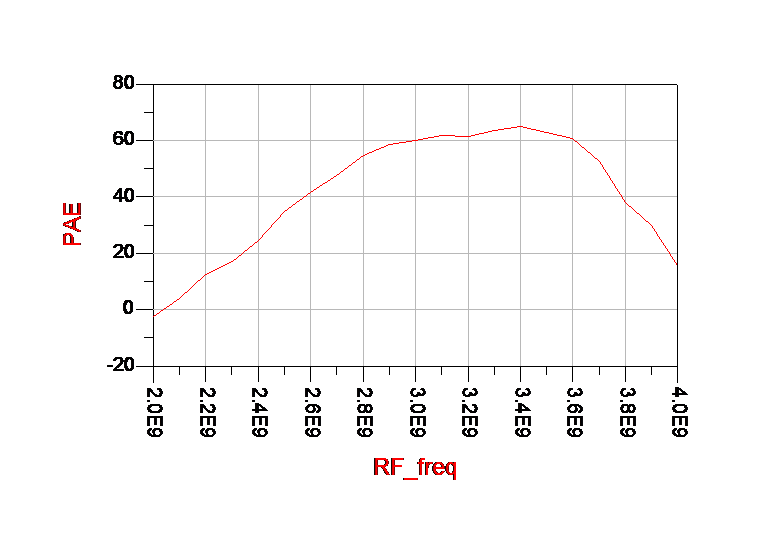

版图联合仿真满足S参数指标要求后,进行谐波平衡仿真与增益,功率仿真,结果如下,可见基波在3.1GHz处的功率为48.5dBm,二次谐波和三次谐波的功率为10dBm左右,谐波相对于基波可以忽略不计。CGH40045F晶体管的3dB输出功率约48.5dBm,而实际需要46.6dBm就已经足够,因此在正常工作时,没有必要达到此3dB压缩点,在全频段功放效率在50%以上。

- 驱动级功放设计

驱动级选择的CREE的CGH40010F,芯片资料中,给出了CGH40010氮化镓高电子迁移速率晶体管的饱和输出功率为13W,在饱和输出功率下的效率为65%。

根据大信号模型仿真其阻抗点跟末级功放一样,具有线性的增长变化,因此中间级驱动具有相同的拓扑结构,通过优化变量使其S参数指标满足要求。

原理图结合EM版图联合仿真,同时分别调用ADS电磁仿真软件下的S参数仿真模块对其功率增益以及一端口二端口的反射情况进行仿真分析;调用谐波平衡仿真模块对其二次谐波、三次谐波的大小进行分析;调用增益压缩仿真模块,对匹配电路的1dB功率增益压缩点进行仿真分析等。

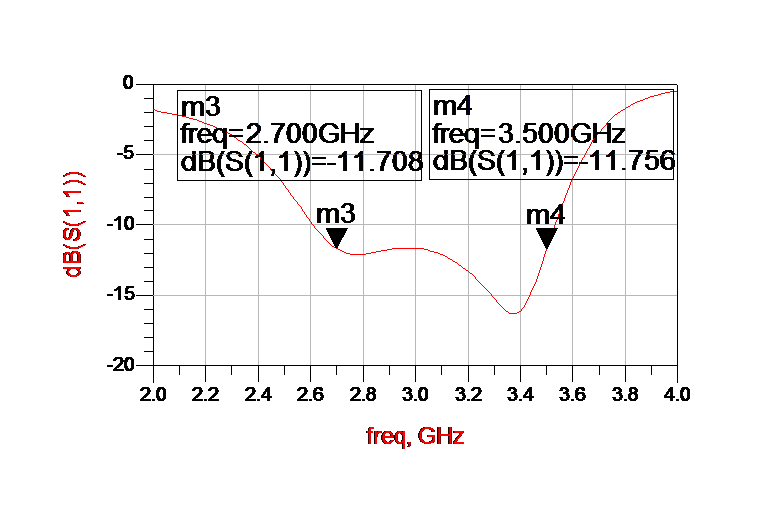

2.1 驱动级功放S参数仿真分析

如下图所示,S(1,1)<-11dB,S(2,1)>13dB。

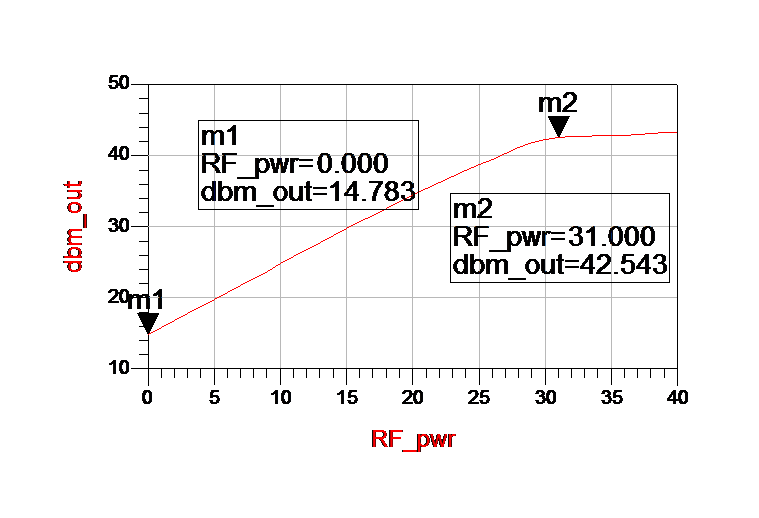

2.2 驱动级功放谐波平衡仿真

如下图所示,中心频率3.1GHz处,基波的3dB压缩点的输出功率约为42.5dBm,二次谐波和三次谐波的3dB压缩点的输出功率分别约为20.2dBm、13.2dBm,较基波的输出功率小得多,对基波影响较小。晶体管全频带效率大概在35%以上。

3 前级功放的设计

前级功放选择Hittite公司的HMC 464功放芯片,其增益在2GHz~4GHz内大于16dB,回波损耗在-15dB以下,输出功率1dB压缩点为26dBm。

- 末级隔离器的选型

为了保障功放的合理测试,防止反射功率太大损坏功放,因此末级选择了UIY(深圳优译的隔离器)UIYBDI3234A2T4,如下图所示:

- 整机链路计算

此模块采用三级放大,整个模块的效率在50%

-

功率放大电路

+关注

关注

13文章

161浏览量

25848 -

晶体管

+关注

关注

77文章

9682浏览量

138079 -

偏置电路

+关注

关注

10文章

97浏览量

30787 -

ADS仿真

+关注

关注

0文章

71浏览量

10434 -

二次谐波

+关注

关注

0文章

25浏览量

9573

发布评论请先 登录

相关推荐

请问RF的频率是1.2GHZ-3.5GHZ,本振芯片可以选什么?

3.5GHz产业市场巨大

MT8820A无线通信分析仪--30MHz至2.7GHz

TRF1216,pdf(3.5-GHz High Dynam

3.5GHz固定无线接入系统技术分析

MAX2839/MAX2839AS 2.3GHz至2.7GH

5G NR(3.5 GHz)无线网络覆盖问题及建议方案分析

美国无线通信和CTIA敦促FCC就3.5 GHz和3.7-4.2 GHz频段频谱分配做出行动

HMC546LP2E:10 W,FailSaffe,GAAs,SPDURT.2 GHz to 2.7 GHz数据Sheet

HMC114PM5E:>10W(42 Dbm)、2.7 GHz to 3.8 GHz、Gan Power Amplififer数据Sheet

HMC1114:10瓦,GaN功率放大器,2.7 GHz至3.8 GHz数据表

2.7GHz-3.5GHz功放设计分析

2.7GHz-3.5GHz功放设计分析

评论