高速信号行为、RF信号传播和PDN仿真是PCB中最难仿真的部分。在这些电磁现象中,高速信号传播和RF传播需要电磁场求解器工具来提取有用的结果。在电路仿真中需要考虑的寄生效应和设计特定效应过多。尽管我们很努力,但信息实在太多了,在这两种情况下难以建模。

PDN仿真有些不同,因为要仿真的相关频率范围较低,对于大多数设备而言通常小于10GHz。这意味着可以使用SPICE仿真而不是完整的电磁场求解器仿真,为相对较小的电路板上支持中速数字元件的PDN建模。只要电路板足够小或频率足够低以至于可以忽略传播,就可以通过SPICE仿真收获有用的结果。

如果您以前从未这样做过,我将展示如何设置以及您可能会收获什么样的结果。通过仿真连接到PDN的负载元件中的开关动作,可提取某些有用的数据来描述您的PDN,甚至可以计算其网络参数。在下方我将展示的仿真中,目标是提取:

PDN阻抗频谱

在负载元件的输入引脚处测量的瞬态响应

这些参数如何随着电容值的变化而变化

对相对低速和小型电路板的限制很重要,我将详述这到底意味着什么。

设置PDN仿真

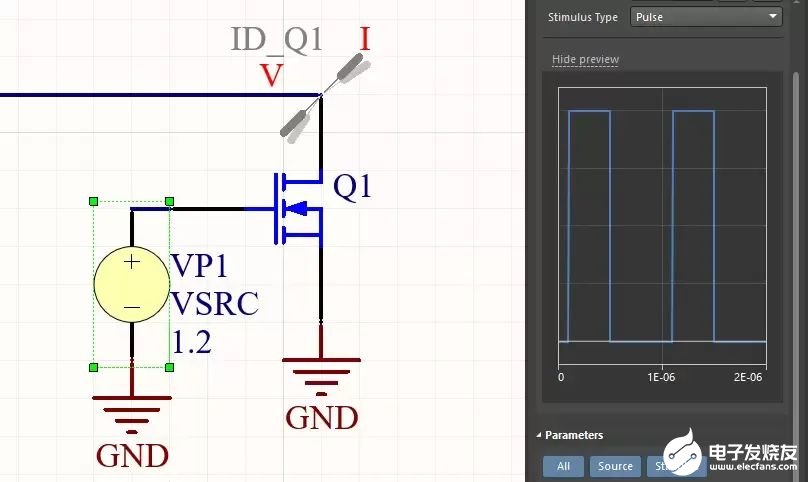

用于描述PDN阻抗和计算瞬态响应的标准仿真如下图所示。我已将其放置在Altium 365 Viewer中,以便用户可以浏览设计并查看仿真是如何设置的。

仿真原理图是使用一组未按任何特定顺序选择的去耦电容器创建的。起初我一直把这个数字保持在较低水平,但稍后我将在的仿真中增加这个数字,这样我们就可以看到增加电容会如何影响结果。在继续的同时,我们将调整其他参数。

等效电路模型

此原理图是使用Altium Designer中内置的仿真通用元件库中的元件设置的。如果不是Altium Designer用户,您当然可以使用SPICE包或其他原理图编辑器中的通用元件,在任何其他仿真程序中重新创建。正如我在原理图中指出的那样,整体仿真由四个部分组成:

稳压器:这是为PDN供电的稳压器模块或电路。我已包括其标称输出电阻和电感。

衰减:这是去耦电容器部分。电容器将ESL和ESR作为分立元件包括在内,只是为了清楚地显示它们。请注意,您还可以将这些值定义为属性面板中这些元件的参数。

平面:本节定义了我们的电源/接地平面对的电容、电感和电阻。本节中的电感是扩散电感,我在另一篇文章中对此进行了描述。

PWR_IN:这是我们负载IC中的输入电源部分。我已尝试通过电感、引脚封装电感和输入端的接触电阻,对输入进行建模。这些值因产品和封装而异,但此处的值是典型的数量级数字。

此等效电路模型需要调整平面电容(CP1)、平面电感(LP1)和去耦电容的数量。我们将使用瞬态分析和交流扫描仿真来获得这些数据。

在此之前,我们应该讨论上图所示的NMOS元件。

负载建模

PWR_IN部分包含一个负载模型,它只是一个开关n通道MOSFET。在建模负载并查看PDN上的瞬态响应时,目标是检查PDN如何对开关操作做出反应,然后吸收电流。以这种方式使用快速MOSFET,可检查负载电流如何根据某些逻辑输入突然切换到高电流状态。该逻辑输入通过在属性面板中将VSRC元素设置为脉冲模式以实现建模目的。我已将升压和降压时间设置为1ns。尽管1/(升压时间)带宽为500MHz,但这不在超高频范围内,因此信号可能会受到平面去耦不良和较大电容器的影响。

仿真中的PWR_IN部分

另一种方法是将电流源设置为脉冲模式。这将有效地执行在低电流状态和高电流状态之间切换负载的相同功能。然后,仿真将读取输出给MOSFET漏极的电流和电压。更准确的方法是放置一个CMOS缓冲电路来仿真IO,但这对于检查接地反弹或抖动等问题会更好,因此我们将其保存以备后用。现在,我们将查看上述模型,以检查当逻辑电路切换状态并通过PDN汲取电流时会发生什么。

结果

首先,我想看看上述案例的结果,我们有9个不同值的并联去耦电容器,它们都具有相似的ESL和适中的ESR值。ESR值在这里很重要,因为它有助于拉平PDN阻抗频谱,正如我在另一篇关于PDN阻抗的文章中所展示的那样。仿真参数如下:

瞬态分析:10ns步长,5-10us总仿真时间

交流扫描:10GHz最大频率,计算PDN的|Z|

去耦电容器编号:我将查看上面的9个电容器模块和一个由36个电容器组成的四倍模块。

平面电容:低态(CP1 = 20 pF)和高态(CP1 = 1 nF)

内芯电压:VDD = 1.8 V

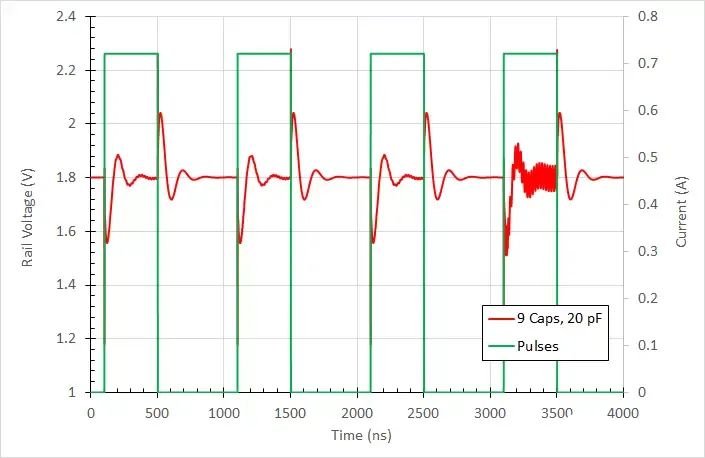

9个电容器,20pF平面电容

仅使用9个去耦电容器和20pF平面电容,我们可以看到瞬态响应中具有非常大的波动,幅度达到约300 mV,叠加在所需的1.8V内芯电压上。这对于任何实际应用来说都大到无法接受,并且会在输出上产生大的干扰。此处显示的数据摘自.sdf文件并导出为Excel格式。

使用9个去耦电容器和20 pF平面电容的瞬态结果

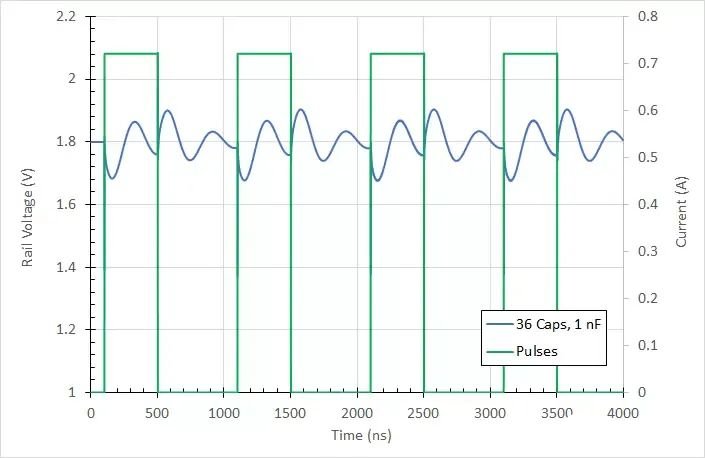

36个电容,1 nF平面电容

让我们看看当我们将去耦电容器的数量增加到四倍并将平面电容增加到50倍时会发生什么。此设计的新版本和改进版本如下所示。基本上,复制去耦电容器模块是为了增加该去耦网络的等效电容。

结果清楚地显示了具有电源/接地平面对以及更多去耦电容器的好处;随着电容的增加,瞬态响应的幅度通常会下降,正如我们所预料的那样。当我们将电容器数量增加到四倍并增加平面电容时,PDN上的电源轨响应仅以100mV的幅度波动。

使用36个去耦电容器和1 nF平面电容的瞬态结果

对于1.8V电源轨来说,这仍然有点大,似乎使用36个电容器应该会产生更好的结果。通过查看每种情况下的阻抗频谱,我们可以了解为什么使用更多电容器不会产生明显的阻尼。

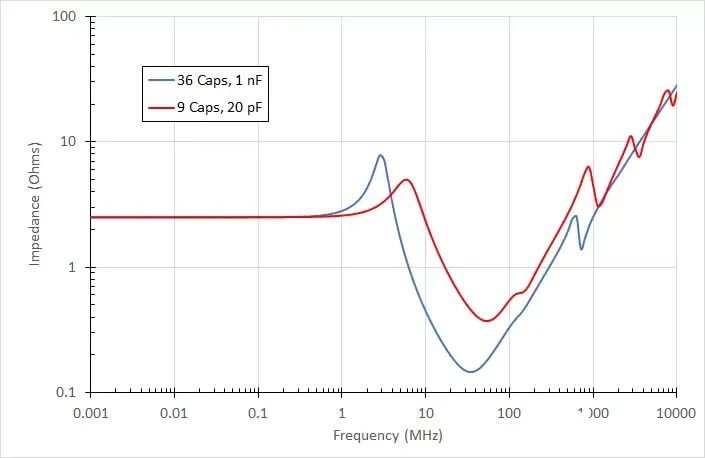

阻抗比较

我们还可以取频域中复V/I响应函数的比率(AC扫描结果),然后计算该比率的大小以获得PDN阻抗。我们可以看到PDN阻抗仍然偏大,尤其是在1/(升压时间)带宽限制附近。在查看PDN阻抗频谱时,我们也可以看到其优势,如下所示。下图将36 decaps/1 nF的当前情况与之前的9 decaps/20 pF情况进行了比较。

PDN阻抗仿真结果对比

请注意,在大约10年内,我们能达到低阻抗(100 mOHM)。我们希望这个低阻抗频带更低更宽。我们还有一些在3MHz左右的峰值和630MHz的高频响应。为了解决这些问题,我们可能需要更多数量和多样性的电容器。我们可以使用一些其他技巧,例如在层过渡到IC期间增加过孔数,因为这会减少PWR_IN输入级的总电感,而我们可以在SPICE仿真中反映这一点。 实际上,在高IO计数IC中,具有36个低ESL/低ESR电容器很常见;当然,在单脉冲中会产生720mA电流的IC中也是如此。事实上,如果您查看一些使用具有高IO计数的高速元件的参考设计或评估产品,您会发现36个去耦电容器是一个较低的数字。仅供参考,此脉冲的dI/dt值为720MA/秒(即每秒720兆安!),这是一个庞大的数字,需要许多电容器快速放电。在这种薄平面分离电介质上嵌入电容材料也会增加平面电容。

为什么是“小型”电路板?

什么才算是“小型”PDN?请记住,当负载切换时,宽带电流脉冲被拉入PDN,并且该脉冲以光速沿PDN传播。将其视为一种传播信号,但它承载的是能量而不是数据。在小型PDN的限制下,我们可以像在传输线中一样忽略传播效应。事实上,传输线比较在这里是恰当的,PDN有时被描述为使用与传输线相同的集总电路模型。 当传输功率脉冲中具有最大频率元件的波长远大于标称电路板尺寸时,我们可以忽略传输功率必须从稳压器输出传播到负载输入这一事实。这与理解为什么我们可以在传输线中定义临界长度的逻辑相同。一旦设计过大,或者当相关带宽达到非常高的频率时,将需要电磁求解器来运行完整的PDN阻抗仿真并提取瞬态响应。

缺少什么?

精明的设计工程师应该注意到一些重要的事情:我们没有将耗散包括在平面电容中!这引用了介电常数的虚部,通过将一些与平面电容串联的电阻相加来实现建模目的。它在传输线的阻抗方程中基本上起着与G相同的作用。此电阻的大小需要一些额外的计算,这将取决于分隔平面层的介电材料的损耗量。在下一篇关于电源平面谐振的文章中,我们将能够看到层压板中高损耗切线的有益影响。

我们还能仿真什么?

上方结果清楚地显示了增加电容如何降低PDN阻抗并有助于稳定内芯电压。上述电容器仅为随机选择,并非基于针对特定频率范围的全面分析。如果我们通过这项练习并在更宽的带宽上降低PDN阻抗,就能收获更好的结果。 我们可以在SPICE中仿真的其他一些点包括:

我们已经通过计算输入和输出端口的阻抗,得出PDN的S参数

拉入PDN的任何电流脉冲的脉冲响应

PDN中多轨之间的传输阻抗

额外电感影响,例如在电源引脚上添加铁氧体;我们将在即将发表的文章中对此进行探讨

将旁路电容器直接添加到负载的电源输入中(与Q1并联)

Altium Designer中的内置SPICE包可以帮助您执行一系列仿真,包括PDN仿真。当您准备将这些文件发布给您的协作者进行更高级的仿真时,Altium 365平台可以轻松协作和共享您的项目。您可以在一个软件包中找到设计和生产高级电子产品所需的一切。

博客作者:Zachariah Peterson

-

pcb

+关注

关注

4418文章

23979浏览量

426300 -

阻抗

+关注

关注

17文章

994浏览量

49514 -

仿真

+关注

关注

55文章

4539浏览量

138689 -

SPICE

+关注

关注

6文章

199浏览量

44707 -

PDN

+关注

关注

0文章

86浏览量

23505 -

Altium Designer

+关注

关注

50文章

407浏览量

47310

原文标题:SPICE中的PDN阻抗仿真与分析

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

浅谈复杂芯片设计中的SPICE仿真困境

铜厚对阻抗的影响在实际设计中如何验证?

使用MPS MPQ8785负载点器件实现PDN阻抗容限要求

英飞凌IPOSIM平台加入基于SPICE的模型生成工具,助力提升系统级仿真精度

SPICE中的PDN阻抗仿真与分析

SPICE中的PDN阻抗仿真与分析

评论