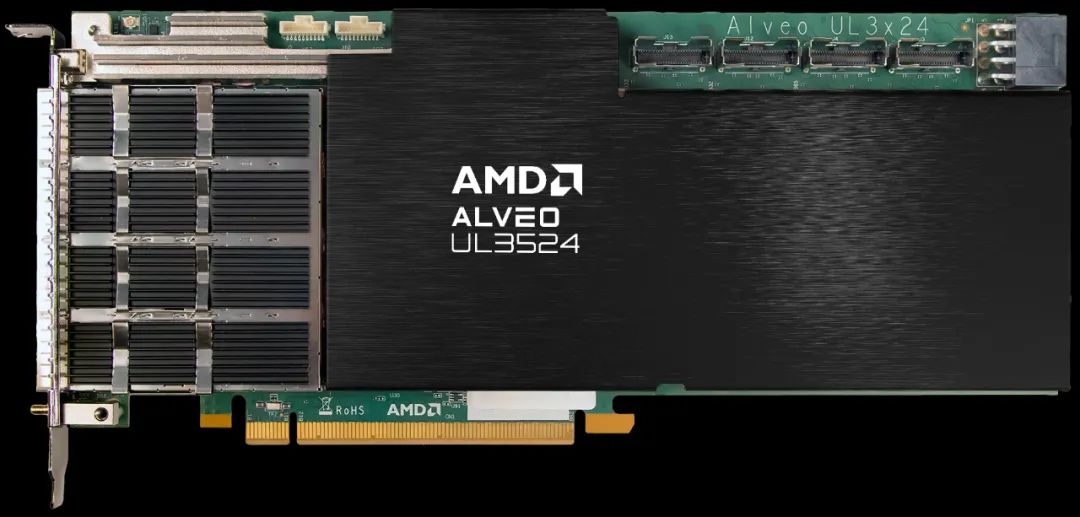

AMD Alveo UL3524

- 新款 AMD Alveo 金融科技加速卡能为交易公司和经纪商提供突破性的纳秒级交易执行性能以及 AI 赋能的交易策略 -

-解决方案合作伙伴 Alpha Data、Exegy 和 Hypertec 加入到不断壮大的面向金融科技市场的超低时延解决方案生态系统 -

AMD(超威,纳斯达克股票代码:AMD)日前宣布推出 AMD Alveo UL3524 加速卡,这是一款面向超低时延电子交易应用设计的新款金融科技( fintech )加速卡。Alveo UL3524 已由领先的交易公司进行了部署,并且支持多种解决方案合作伙伴产品,能够为自营交易商、做市商、对冲基金、经纪商和交易所提供一流的 FPGA 平台,以纳秒( ns )速度进行电子交易。 较之上一代 FPGA 技术,Alveo UL3524 带来了 7 倍的时延提升[注释1],从而达到小于 3 纳秒的 FPGA 收发器时延[注释2],加速交易执行。其由定制的 16nm Virtex UltraScale+ FPGA 提供支持,采用新颖的收发器架构,其具备硬化且经过优化的网络连接核,以实现突破性能。通过在量产平台上将硬件灵活性与超低时延网络相结合,Alveo UL3524 能够比传统 FPGA 替代方案更快实现设计收敛与部署。

较之上一代 FPGA 技术,Alveo UL3524 带来了 7 倍的时延提升[注释1],从而达到小于 3 纳秒的 FPGA 收发器时延[注释2],加速交易执行。其由定制的 16nm Virtex UltraScale+ FPGA 提供支持,采用新颖的收发器架构,其具备硬化且经过优化的网络连接核,以实现突破性能。通过在量产平台上将硬件灵活性与超低时延网络相结合,Alveo UL3524 能够比传统 FPGA 替代方案更快实现设计收敛与部署。

AMD 产品营销总监 Hamid Salehi:

“在超低时延交易中,1 纳秒即可决定交易的盈亏。Alveo UL3524 加速卡由 AMD 超低时延 FPGA 收发器提供支持,专为给我们身处金融市场的金融科技客户带来可观的竞争优势而打造。”

硬件灵活性以及人工智能赋能的交易策略

Alveo UL3254 采用 64 个超低时延收发器、78 万个 FPGA 架构查找表( LUT )以及 1,680 个数字信号处理( DSP )计算片,旨在加速硬件中的定制交易算法,令交易商能够根据不断演进的策略和市场条件定制其设计。该产品为采用 Vivado 设计套件的传统 FPGA 流程所支持,配套提供一套参考设计和性能基准,使 FPGA 设计人员能够快速探索关键指标并根据规范开发定制交易策略,并得到 AMD 领域专家的全球支持。 为了简化人工智能( AI )在算法交易市场中日益普遍的采用,AMD 为开发人员提供了开源且受到社区支持的FINN 开发框架。通过使用 PyTorch 和神经网络量化技术,FINN 项目令开发人员能够在缩小 AI 模型尺寸的同时保持准确性、编译到硬件 IP 以及将网络模型集成到算法的数据路径中,带来低时延性能。作为一项开源计划,该解决方案为开发人员赋予了灵活性与可及性,可随项目演进获取最新技术进展。

实现不断壮大的超低时延

金融科技解决方案生态系统

Alveo UL3524 及专属打造的 FPGA 技术使战略合作伙伴能够为金融科技市场构建定制解决方案和基础设施。目前可供使用的合作伙伴解决方案包括来自 Alpha Data、Exegy 和 Hypertec 的产品。

为 Alveo UL3524 加速卡提供支持的 AMD Virtex UltraScale+ VU2P FPGA 使 Alpha Data 的超低时延设备成为可能。

Alpha Data 总经理 David Miller 表示:“AMD 的新款 Virtex UltraScale+ FPGA 为超低时延交易和网络带来了跨越式改进。我们开发的 ADA-R9100 机架式设备使客户能够轻松地充分发挥全新 AMD FPGA 器件的全部潜力。”

Exegy 作为端到端前台交易解决方案提供商,正在利用其 nxFramework 为 Alveo UL3524 卡提供支持。nxFramework 是一种软件与硬件开发环境,专为在金融行业内创建和维护超低时延 FPGA 应用定制而成。

Exegy FPGA 解决方案总监 Olivier Cousin 表示:“通过结合 AMD 开创性的超低时延 FPGA 技术与 Exegy 在资本市场的专长,我们得以提供一款综合全面的解决方案,应对构建未来交易基础设施所需面临的日益增多的优化问题。”

针对 Alveo UL3524,Hypertec 借助定制冷却系统优化了其 ORION HF X410R-G6 高频服务器,使之部署在 1U 服务器尺寸规格中。

Hypertec 产品营销总监 David Lim 表示:“Hypertec 工程师专门设计了 HF X410R-G6,以充分施展 Alveo UL3524 平台的功能和速度,使我们的解决方案能够满足低时延任务极其严苛的需求。”

AMD Alveo UL3524 加速卡目前已投入量产,并向全球金融服务客户供货。

如果您希望进一步了解 Alveo UL3524 加速卡,请访问产品专区。

欲购买该产品,请在官方微信后台回复“Alveo UL3524 购买”,获取购买方式。

[1] 截至 2023 年 8 月 16 日,AMD 性能实验室使用 Vivado Design Suite 2023.1,对运行在 Vivado Lab(硬件管理器) 2023.1 上的 Alveo UL3524 加速卡进行了测试。基于 GTF 时延基准设计,经过配置,可在内部近端回送模式下启用 GTF 收发器。GTF TX 和 RX 时钟在大约 644MHz 的相同频率下工作,相移为 180 度。GTF 时延基准设计通过锁存单个空闲运行计数器的值来测量硬件中的时延。时延即为 TX 数据在 GTF 收发器处锁存的时间与其在路由回 FPGA 架构之前在 GTF 接收器处锁存的时间之间的差值。时延测量不包括协议开销、协议帧、可编程逻辑 (PL) 时延、TX PL 接口设置时间、RX PL 接口时钟输出、包飞行时间和其它时延来源。基准测试运行了 1,000 次,每次测试 250 帧。引用的测量结果基于 GTF 收发器“RAW 模式”,其中收发器的物理介质连接子层 (PMA) 将数据“按原样”传递到 FPGA 架构。时延测量结果在此配置的所有测试运行中保持一致。系统制造商可能会修改配置,因此产生不同的结果。ALV-10 [2] 基于 Virtex UltraScale+ GTY 收发器与超低时延 GTF 收发器的仿真比较。

原文标题:AMD 为超低时延电子交易推出 Alveo UL3524 加速卡

文章出处:【微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

-

赛灵思

+关注

关注

33文章

1798浏览量

133651 -

Xilinx

+关注

关注

73文章

2206浏览量

131867

原文标题:AMD 为超低时延电子交易推出 Alveo UL3524 加速卡

文章出处:【微信号:赛灵思,微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

选择AMD Alveo V80加速卡的五大理由

AMD Alveo MA35D媒体加速卡的AMA SDK 1.4.0版本发布

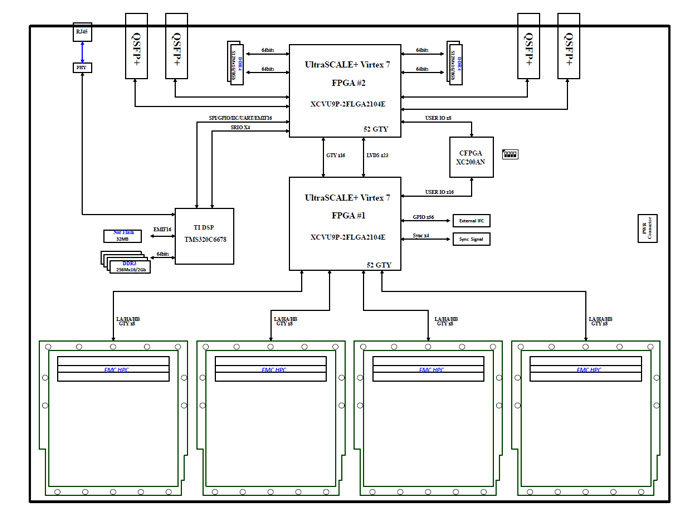

FPGA硬件加速卡设计原理图:1-基于Xilinx XCKU115的半高PCIe x8 硬件加速卡 PCIe半高 XCKU115-3-FLVF1924-E芯片

新品 | LLM-8850 Kit,高性能AI加速卡套件 DinMeter v1.1,1/32DIN标准嵌入式开发板

AMD Alveo MA35D加速器:开启大规模交互式流媒体新时代

专为边缘而生:深度解析昆仑芯K100 AI加速卡,释放128 TOPS极致能效

算力密度翻倍!江原D20加速卡发布,一卡双芯重构AI推理标杆

虚拟电厂加速卡不是噱头!万点规模VPP的性能分水岭

新品 | LLM-8850 Card, AX8850边缘设备AI加速卡

智算加速卡是什么东西?它真能在AI战场上干掉GPU和TPU!

边缘AI运算革新 DeepX DX-M1 AI加速卡结合Rockchip RK3588多路物体检测解决方案

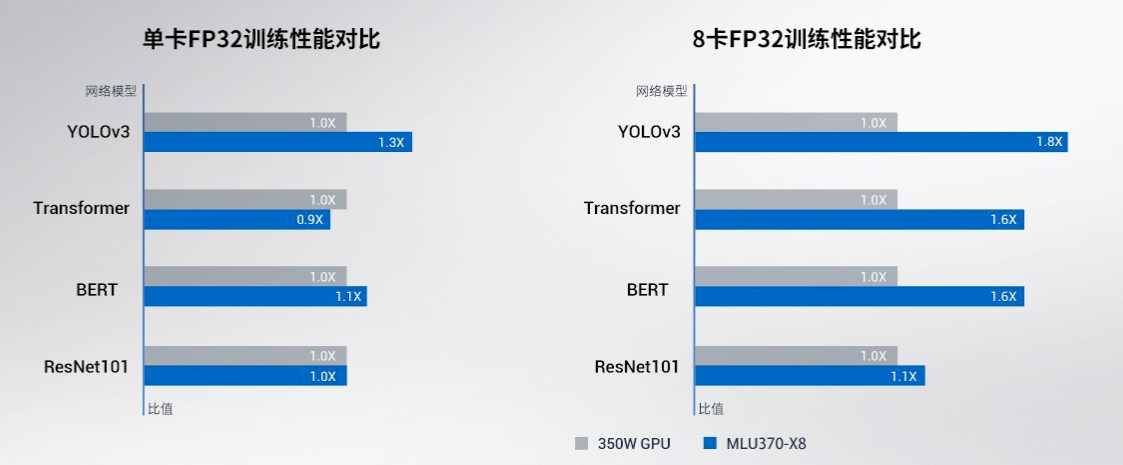

寒武纪基于思元370芯片的MLU370-X8 智能加速卡产品手册详解

AMD 为超低时延电子交易推出 Alveo UL3524 加速卡

AMD 为超低时延电子交易推出 Alveo UL3524 加速卡

评论